- •Основы цифровой электроники

- •1.1. Логические функции

- •1.1.1Аксиомы и теоремы алгебры логики

- •1.1.2Операция сумма по модулю два

- •1.2. Логические элементы

- •Комбинационные схемы

- •1.3. Некоторые системы счисления

- •1.4. Дешифратор

- •1.5. Шифратор

- •1.6. Демультиплексор

- •1.7. Увеличение разрядности дешифраторов и демультиплексоров

- •1.8. Мультиплексор

- •1.9. Преобразователи кода

- •1.10. Сумматоры

- •Последовательностные схемы

- •1.11. Триггеры

- •1.11.1Асинхронный rs-триггер

- •1.11.2Синхронный rs-триггер

- •1.11.4Синхронный (динамический) d-триггер

- •1.11.5Универсальный jk-триггер

- •1.11.7Взаимные преобразования триггеров

- •1.12. Счетчики

- •1.13. Регистры

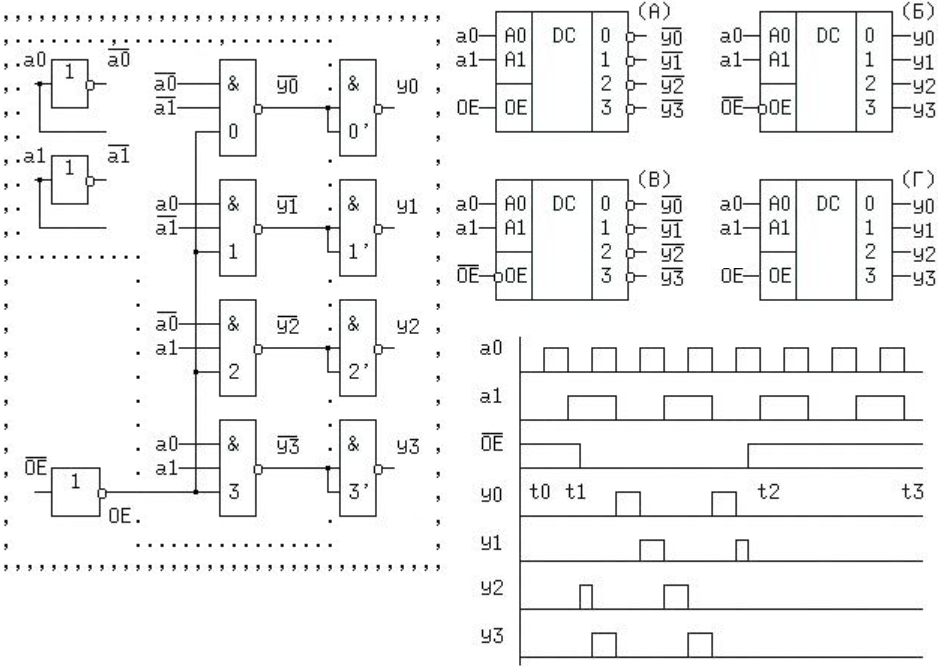

1.4. Дешифратор

Дешифратор (ДШ) преобразует двоичный код на входах в активный сигнал на том выходе, номер которого равен десятичному эквиваленту двоичного кода на входах. Например, входной код 1001 должен сделать активным провод с номером 9. Во всех остальных проводах дешифратора сигналы должны быть нулевыми (или единичными – в зависимости от организации выходной логики: прямая или инверсная). Дешифратор можно считать преобразователем параллельного кода в позиционный.

В полном дешифраторе количество выходов N = 2n, где n – число входов. В неполном ДШ N < 2n. По другому определению, полный ДШ, имеющий n входов, должен реализовывать 2n минтермов уi, определенных на всех наборах из n входных переменных.

Большинство

дешифраторов снабжено одним или

несколькими дополнительными входами

разрешения выходов (прямыми ОЕ или

инверсными

![]() ).

Если на таком входе активный уровень,

то ДШ работает в соответствии со своим

определением, а если пассивный, то на

всех выходах также будут пассивные

значения (для прямых выходов – нули, а

для инверсных – единицы).

).

Если на таком входе активный уровень,

то ДШ работает в соответствии со своим

определением, а если пассивный, то на

всех выходах также будут пассивные

значения (для прямых выходов – нули, а

для инверсных – единицы).

Рассмотрим ДШ с n=2 и N=4, называемый также дешифратором "2 в 4" или "два на четыре". Активным уровнем сигнала на прямых входах/выходах будет 1, а на инверсных – 0. По этому определению заполним таблицу истинности, где величина х может принимать любые значения.

DEC число |

Входы |

Выходы (прямые и инверсные) |

ЛФ |

||||||||||

al |

a0 |

ОЕ |

|

y0 |

y1 |

y2 |

у3 |

|

|

|

|

||

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

|

||

2 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

|

||

3 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

|

||

x |

x |

x |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

yi=0

( |

Преобразуем

полученные для yi

уравнения с помощью закона двойного

отрицания к базису

И-НЕ:

![]() .

Решению соответствует схема на рис.2.1.

.

Решению соответствует схема на рис.2.1.

Рис.2.1

Схема слева, обведенная точками, имеет условное графическое обозначение (А), а схема в запятых – обозначение (Б). Возможны также еще две комбинации прямых и инверсных входов и выходов, показанные на В и Г.

Пояснить

работу ДШ можно с помощью временных

диаграмм для схемы (Б). Во время действия

сигнала

![]() на нижних входах элементов И-НЕ(0…3)

присутствует ОЕ=0, и независимо от

значений a0,al

выходные значения

на нижних входах элементов И-НЕ(0…3)

присутствует ОЕ=0, и независимо от

значений a0,al

выходные значения

![]() ,

a

yi=0,

что и видно из рис.2.1 (в эти отрезки

времени t0…t1

и t2…t3

выходы "запрещены", т.е. на прямых

выходах yi

устанавливается пассивный уровень "0",

а на инверсных выходах пассивная "1").

В интервале t1…t2

сигнал

,

a

yi=0,

что и видно из рис.2.1 (в эти отрезки

времени t0…t1

и t2…t3

выходы "запрещены", т.е. на прямых

выходах yi

устанавливается пассивный уровень "0",

а на инверсных выходах пассивная "1").

В интервале t1…t2

сигнал

![]() (ОЕ=1), и значения yi

зависят только от переменных a1,

a0.

Если код на входах а1а0=10 (BIN),

что соответствует десятичной двойке,

на входах элемента И-НЕ (2) соберутся три

логических "1". Сигнал

(ОЕ=1), и значения yi

зависят только от переменных a1,

a0.

Если код на входах а1а0=10 (BIN),

что соответствует десятичной двойке,

на входах элемента И-НЕ (2) соберутся три

логических "1". Сигнал

![]() ,

а у2=1, что видно на диаграмме у2.

,

а у2=1, что видно на диаграмме у2.

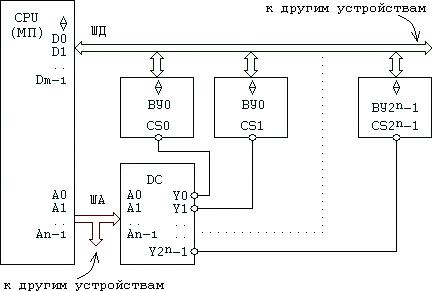

Дешифраторы

широко применяются в вычислительной

технике (рис.2.2), как часть больших

интегральных схем, для выбора одного

из нескольких внешних устройств (ВУ)

при обмене данными между ним и

микропроцессором (CPU).

В этом случае на входы Ai

дешифратора микропроцессор (МП) по шине

адреса (ША) помещает адрес ВУ, поэтому

такие входы называются адресными.

Активный

сигнал

![]() с одного из выходов ДШ поступает на

инверсный вход

с одного из выходов ДШ поступает на

инверсный вход

![]() – "выбор микросхемы - Chip

Select"

– адресуемого ВУ, подключая его к шине

данных (ШД)

Вслед за этим МП производит обмен данными

с выбранным ВУ по шине данных. Все

остальные ВУ пассивны, т.к. на их входах

– "выбор микросхемы - Chip

Select"

– адресуемого ВУ, подключая его к шине

данных (ШД)

Вслед за этим МП производит обмен данными

с выбранным ВУ по шине данных. Все

остальные ВУ пассивны, т.к. на их входах

![]() и их информационные выводы, подключенные

к ШД, находятся в третьем

состоянии

и не препятствуют обмену данными между

адресованным ВУ и МП (Шина – группа

проводников, имеющих одинаковое

функциональное назначение).

и их информационные выводы, подключенные

к ШД, находятся в третьем

состоянии

и не препятствуют обмену данными между

адресованным ВУ и МП (Шина – группа

проводников, имеющих одинаковое

функциональное назначение).

Рис.2.2