- •Структура эвм.

- •2. Системы счисления. Основание системы. Разряд числа.

- •Анализ позиционных систем счисления.

- •Двоичная система счисления

- •Восьмеричная система счисления

- •Шестнадцатеричная система счисления

- •Преобразование чисел в разных системах счисления.

- •5. Выполнение машинных операций сложения и вычитания.

- •6. Выполнение машинных операций умножения и деления.

- •7. Представление двоичных чисел в форме с плавающей точкой. Мантисса и порядок числа. Нормализация чисел.

- •Нормализация чисел

- •8. Организация записи разряда числа. Триггер. Синхронный и асинхронный триггер.

- •9. Арифметические операции над числами с плавующей точкой.

- •10. Логические функции. Основные понятия.

- •11. Булевы функции одной переменной.

- •12. Булевы функции двух переменных – дизъюнкция, конъюнкция, неравнозначность.

- •14. Булевы функции двух переменных: импликация, стрелка Пирса, штрих Шеффера.

- •15. Основные зависимости между булевыми функциями.

- •16. Основные законы булевой алгебры.

- •17. Нормальные формы: днф, кнф. Порядок приведения к нормальным формам.

- •18. Совершенные нормальные формы. Порядок приведения к сднф и скнф.

- •19. Минимизация логических выражений. Метод карт Карно.

- •20. Представление логических функций в алгебре Жегалкина.

- •21. Понятие логического элемента. Основные логические элементы.

- •22. Логические схемы. Порядок построения логических схем.

- •23. Порядок построения многовыходных логических схем.

- •24. Построение комбинационных схем для частично-определенных функций.

- •25. Основные комбинационные устройства: одноразрядный полусумматор и сумматор.

- •26. Реализация логических схем в различных базисах.

- •27. Организация переноса в сумматорах. Сумматоры с последовательным и параллельным переносом.

- •28. Применение сумматоров: различные структуры для выполнения арифметических операций.

- •29. Организация суммирования чисел: параллельный и последовательный способ.

- •30. Запись чисел в прямом, обратном и дополнительном коде. Использование сумматоров для вычитания.

- •31. Организация построения сумматоров: сумматоры с групповым и условным переносом.

- •32. Организация построения сумматоров: сумматоры со сквозным переносом, накапливающие сумматоры.

- •33. Основные комбинационные устройства: одноразрядный полувычитатель и вычитатель.

- •Объединенная схема одноразрядного комбинационного сумматора-вычитателя

- •34. Организация умножения чисел с помощью накапливающего сумматора.

- •35. Матричные умножители двоичных чисел.

- •36.Умножение двоичных чисел со сдвигом в регистре множимого и сумматора.

- •37. Методы ускоренного умножения.

- •38.Деление двоичных чисел с восстановлением и без восстановления остатка.

- •39. Основные комбинационные устройства: мультиплексоры и компараторы.

- •Цифровые компараторы.

- •40. Основные комбинационные устройства: демультиплексоры и дешифраторы.

- •41.Организация памяти эвм. Виды зу, их характеристики.

- •42.Организация доступа к памяти эвм.

- •43.Организация записи и сдвига информации с помощью регистров.

- •44.Оперативная память эвм.

- •45.Организация работы триггеров. Rs-, d-, t-триггеры.

- •46.Постоянная память эвм.

- •47.Понятие счетчика. Двоичные и двоично-десятичные счетчики. Изменение модуля счета.

- •48. Изменение направления счета и организация переноса в счетчиках.

- •49.Использование счетчиков в качестве делителей частоты.

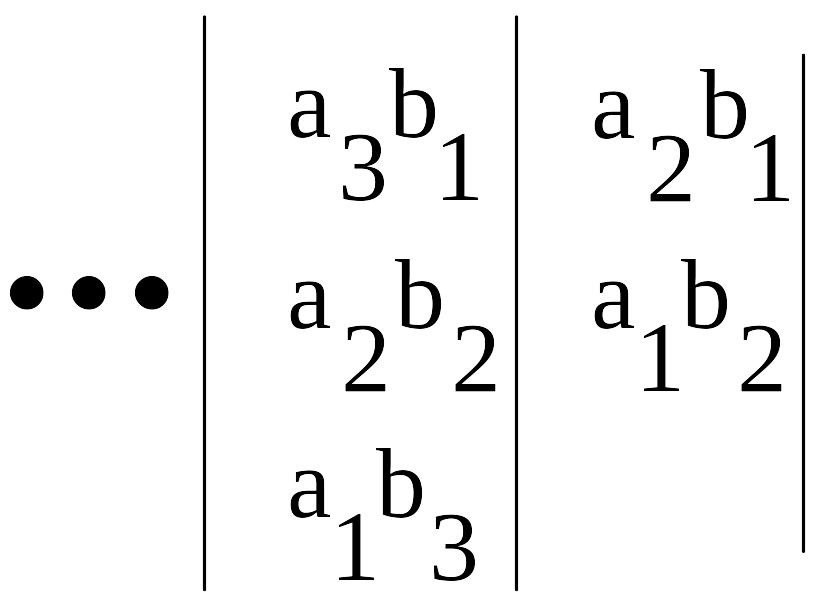

35. Матричные умножители двоичных чисел.

Кроме рассмотренных методов ускоренного умножения существуют методы умножения, основанные на использовании матриц промежуточных результатов.

Пусть имеем сомножители: Мн = А = аn ... a2 a1

Мт = B = bn ... b2 b1

Рассмотрим схему традиционного (“школьного”) алгоритма умножения (Б).

А = аn ... a2 a1

* B = bn ... b2 b1

anb1

... a3b,

a2b1,

a1b1

anb1

... a3b,

a2b1,

a1b1

+anb2 . . . a2b2, a1b2

+ . . .

anbn ... a2bn, a1bn

C = C2n

. . . .

C2

C1

C = C2n

. . . .

C2

C1

Рассмотренная схема умножения может быть представлена в виде матрицы.

-

an

. . .

a2

a1

b1

an b1

. . .

a2 b1

a1 b1

b2

an b2

. . .

a2 b2

a1 b2

bn

an bn

. . .

a2 bn

a1 bn

К аждый

элемент ai

bj (

i, j = 1, n) принимает значение 0 или 1.

Произведение A∙B может

быть получено, если суммировать элементы

матрицы (по диагонали).

аждый

элемент ai

bj (

i, j = 1, n) принимает значение 0 или 1.

Произведение A∙B может

быть получено, если суммировать элементы

матрицы (по диагонали).

\

+

Для суммирования по столбцам могут быть использованы счетчики. Однако при достаточно большом значении величины n потребуются счетчики с большим числом входов, что существенно увеличит время сложения. Но этот принцип умножения может быть реализован на устройствах имеющих не более трех входов. В качестве их могут быть использованы одноразрядные двоичные сумматоры и полусумматоры.

На рис. 10 приведена структурная схема устройства умножения для реализации матричного алгоритма.

Реализация методов матричного умножения требует большего количества оборудования, чем метод последовательного умножения и дает больший выигрыш во времени. В связи с увеличением степени интеграции элементной базы ограничения по качеству оборудования становятся не столь строгими.

36.Умножение двоичных чисел со сдвигом в регистре множимого и сумматора.

5

37. Методы ускоренного умножения.

Умножение с хранением переносов

Время, затрачиваемое на сложения двоичных чисел, состоит из времени

необходимого для поразрядного сложения и времени на формирование переноса

tсл= t++ tпер

Поразрядное сложение является элементарной операцией, и время на эту операцию может быть сокращено путем использования более быстродействующих элементов. В то же время, если исключить необходимость выполнения межразрядных переносов при сложении, то время умножения уменьшится на tпер

Переносы, формируемые при сложении, записываются в отдельный регистр. Содержимое этого регистра добавляется в сумматор вместе с очередным частичным произведением. При этом сложение может выполняться параллельно по всем разрядам.