- •Справочник по системе команд микроконтроллера lpc2000 на базеArm-ядра

- •Введение

- •1. Общие сведения

- •Обработка данных

- •Региcтры cpsr/sprs

- •2. Перечень команд микроконтроллера lpc2000 на базе arm-ядра

- •3. Подробное описание команд микроконтроллера lpc2000 на базе arm-ядра

- •Команда сложения с переносом (Addition with carry)

- •Команда сложения с переносом (Addition with carry)

- •Команда сложения (Addition)

- •Операция сложения без учета флага переноса (Addition)

- •Операция сложения без учета флага переноса (Addition)

- •Операция сложения без учета флага переноса (Addition)

- •Операция сложения без учета флага переноса (Addition)

- •Операция сложения без учета флага переноса (Addition)

- •Команда логического и (And)

- •Команда логического и (and)

- •Команда арифметического сдвига вправо (Arithmetic Shift Right)

- •Команда арифметического сдвига вправо (Arithmetic Shift Right)

- •Переход (Branch)

- •Команда перехода по условию (Branch)

- •Команда безусловного перехода (Branch)

- •Команда сброса битов (Bit Clear)

- •Команда сброса битов (Bit Clear)

- •Контрольные точки (breakpoints)

- •Команда перехода со ссылкой (Branch and Link)

- •Команда перехода со ссылкой (Branch with Link)

- •Команда перехода со ссылкой и сменой режима (Branch with Link and Exchange)

- •Команда перехода со ссылкой и сменой режима (Branch with Link and Exchange)

- •Команда перехода со ссылкой и сменой режима (Branch with Link and Exchange)

- •Переход и переключение режима ядра (Branch and Exchange)

- •Переход и переключение режима ядра

- •Сообщение сопроцессору (Coprocessor Data Processing)

- •Подсчет нулевых битов (Count Leading Zeros)

- •Сравнение с отрицанием (Compare Negative)

- •Сравнение (Compare)

- •Установить флаги регистра cpsr для Rd – Rs.

- •Логическое побитовое «исключающее или» (Exclusive or)

- •Логическое побитовое «исключающее или» (Exclusive or)

- •Загрузить в сопроцессор из памяти (Load Coprocessor)

- •Загрузить в сопроцессор из памяти (Load Coprocessor)

- •Загрузить сразу несколько регистров (Load Multiple)

- •Загрузить сразу несколько регистров (Load Multiple)

- •Загрузить сразу несколько регистров (Load Multiple)

- •Команды множественной загрузки

- •Команда множественной загрузки( Load Multiple Increment)

- •Команда записи слова в регистр (Load Register)

- •Команда однократной передачи данных (Load Register)

- •Команда однократной передачи данных (Load Registr)

- •Команда однократной передачи данных (Load Registr)

- •Команда однократной передачи данных (Load Registr)

- •Команда записи байта в регистр (Load Register Byte)

- •Загрузка байта в регистр из памяти (Load register byte value from memory)

- •Загрузка двойного слова со знаком (Load Reister Doubleword)

- •Команда записи полуслова в регистр (Load Register Halfword)

- •Команда записи полуслова в регистр (Load Register Halfword)

- •Загрузка байта со знаком (Load Register Signed Byte)

- •Команда загрузки знакового байта (Load Register Signed Byte)

- •Загрузка полуслова со знаком (Load Register Signed Halfword)

- •Загрузка регистра полусловом со знаком (Load Register Signed Halfword)

- •Логический сдвиг влево (Logical Shift Left)

- •Логический сдвиг влево (Logical Shift Left)

- •Логический сдвиг вправо (Logical Shift Right)

- •Логический сдвиг вправо (Logical Shift Right)

- •Команда регистрового обмена с сопроцессором

- •Команда регистрового обмена с сопроцессором

- •Команда регистрового обмена с сопроцессором

- •Команда умножения, накопления

- •Загрузить в регистр константу

- •Пересылка (Move)

- •Пересылка (Move)

- •Пересылка (Move)

- •Команда перемещения данных из сопроцессора в arm регистр (Move to arm Register from Coprocessor)

- •Команда перемещения данных из сопроцессора в два регистра arm одновременно

- •Запись psr в регистр общего назначения (Move psr to General-purpose Register)

- •Запись в регистр состояния (Move to Status Register from arm Register)

- •Умножение (Multiply)

- •Умножение (Multiply)

- •Пересылка инверсии (Move Not)

- •Пересылка с инверсией (Move not)

- •Команда инвертирования (Negate)

- •Нет операции (No oPeration)

- •Логическое или (or)

- •Команда логического или (Or)

- •Команда перезагрузки кэша (a cache preload instruction)

- •Команда презагрузки кэша

- •Команда извлечения из стека (pop)

- •Размещение регистров в вершине стека

- •Команда добавление сразу нескольких операндов

- •Команда добавление сразу нескольких операндов с удвоением одного из них

- •Команда приведённого вычитания с удвоением второго операнда (double saturated substraction)

- •Команда приведённого вычитания (saturated substraction)

- •Циклический сдвиг вправо (Rotate Right Register)

- •Команда обратного вычитания (reverse substract)

- •Команда обратного вычитания с заемом (Reverse substract with carry)

- •Команда вычитания с заемом (Substract with carry)

- •Вычитание с переносом (Subtract with Carry)

- •Команда умножения числа со знаком и с накоплением

- •Команда умножения числа со знаком и накоплением

- •Знаковая операция умножения и сложения

- •Команда знакового умножения двух 16-ти битных операндов (Signed multyply)

- •Знаковая операция умножения

- •Команда обмена данными с сопроцесcором

- •Команда обмена данными с сопроцессором

- •Команда обмена данными с сопроцесcором

- •Команда обмена данными с сопроцессором

- •Команда группового хранения (Store Multiple )

- •Соответствия между мнемониками и состояниями битов команд

- •Сохранение не пустого подмножества рон (Store Multiple Increment After)

- •Команда сохранения регистра в памяти(Store Register )

- •Сохранение в памяти 32-х разрядных данных из рон (Store Register)

- •Сохранение в памяти 32-х разрядных данных из рон (Store Register)

- •Сохранение в памяти 32-х разрядных данных из рон (Store Register)

- •Команда сохранения регистра в памяти(Store Register Byte ) (байта)

- •Сохранение в памяти 8-ми разрядных данных из рон (Store Register)

- •Запоминание 2х слов (Stores two words).

- •Команда передачи полуслова между Lo регистром и памятью.

- •Команда сохранения значения регистра (Store Register Halfword)

- •Вычитание (Subtraction).

- •Команда вычитания (Subtract)

- •Команда программного прерывания (Software Interrupt)

- •Команда программного прерывания (Software Interrupt)

- •Команда обмена (Swap)

- •Команда обмена (Swap Byte)

- •Побитовая проверка на равенство (Test Equivalence)

- •Проверка битов (test)

- •Команда сравнения (Test)

- •Список литературы

Обработка данных

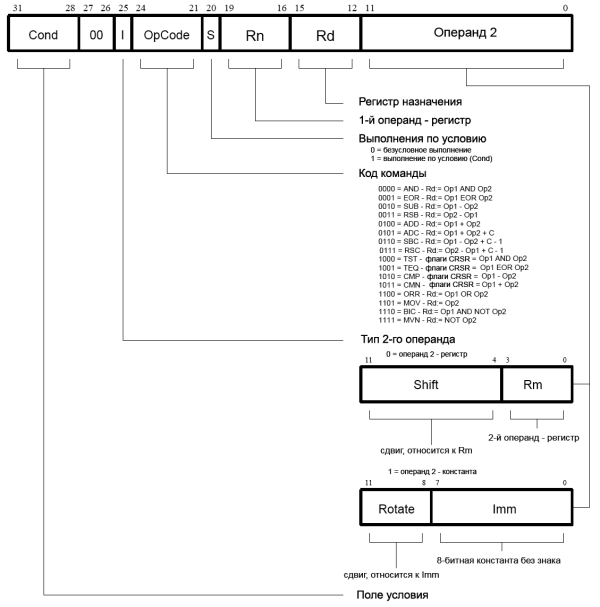

Эта команда будет выполнена, если условие истинно. Все различные условия перечислены в табл. 1. Формат команды группы ARM приведен на рис. 1.

Рис. 1. Команда обработки данных группы ARM

Команда формирует результат, выполняя указанную арифметическую или логическую операцию с одним или двумя операндами.

Первый операнд - всегда регистр (Rn). Второй операнд <shifter_operand> может быть регистром со сдвигом (Rm), или 8-битной константой с циклическим сдвигом (Imm) (в зависимости от значения бита "I" в команде). Флаги CPSR могут оставаться без изменений (S = 0) или выставлены в зависимости от результата выполнения этой команды (S = 1). Некоторые операции в команде (ТЕСТ, TEQ, CMP, CMN) не записывают результат в регистр Rd. Они используются только для того, чтобы в зависимости от результата установить/сбросить флаги CPSR (только при S = 1).

Рис. 2. Команда обработки данных группы THUMB

Далее будут использоваться следующие обозначения:

В угловых скобках «< >» обозначаются объекты. Например, адреса регистров. В круглых скобках «( )» обозначаются значения этих объектов. Например, при описании синтаксиса в ассемблере мы используем объекты:

ADD{<cond>}{S} <Rd>, <Rn>, <shifter_operand>

А при описании работы команды мы используем значения, записанные по указанному исполнительному адресу объектов:

(Rd) = (Rn) + (shifter_operand)

То есть, <Rn> – адрес регистра (от 0 до 15), (Rn) – 32-х разрядное содержимое этого регистра.

Региcтры cpsr/sprs

Описание

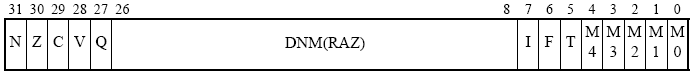

Регистр статуса текущего состояния (Current Program Status Register, CPSR) (рис. 3), содержит флаги условий, биты прерываний, текущий режим процессора и другую информацию, описывающую статус процессора. Каждый режим прерывания так же имеет регистр сохраненного статуса состояния процессора (Saved Program Status Register, SPRS), он используется для сохранения значения CPSR когда возникает прерывание. Значения параметров регистров CPSR/SPRS приведены в таблице 4

Подробное описание регистрового блока приведено в [4].

Рис. 3. Структура регистров CPSR/SPRS

Таблица 4. Регистр CPSR/SPRS

|

Флаг |

№ бита |

Название |

Описание |

|

N |

[31] |

Negative |

Флаг результата выполнения команды. Если N = 1, то результат отрицательный. |

|

Z |

[30] |

Zero |

Флаг результата выполнения команды. Если Z = 1, то результат равен 0. |

|

C |

[29] |

Carry |

– для операции сложения, включающую команду сравнения CMN, флаг C устанавливается в 1 если сложение создает перенос (беззнаковое переполнение) и в значение 0, если переноса нет. – для операции умножения, включающей команду сравнения CMN, C устанавливается в 0 если умножения создает перенос(беззнаковое переполнение) и в значение 1, если переноса нет. – для операций сдвига, в С устанавливается значение бита который был вытеснен в рузультате сдивга – для других операций С остаеться без именений. |

|

V |

[28] |

oVerflow |

– для операций сложения или вычитания если V = 1, то это означает наличие переполнения. – для остальных операций флаг V обычно не меняют. |

|

Q |

[27] |

Q |

Показывает было ли получено переполнение или насыщение в результате выполнения DSP операций |

|

I |

[7] |

IRQ |

Когда установлен, запрещает IRQ прерывание. |

|

F |

[6] |

FIQ |

Когда установлен, запрещает FRQ прерывание. |

|

T |

[5] |

Thumb |

Переключение между ARM и THUMB режимами. Если T=1, то выбран режим THUMB. |

|

M |

[4:0] |

Mode |

Биты определяющие режим работы процессора. |