- •Порядок виконання лабораторних робіт

- •Основні правила техніки безпеки при роботі в лабораторії

- •Мета роботи

- •Теоретичні відомості

- •Виконання роботи

- •Вимірювання амплітудної напруги

- •1 .Під'єднати входи осцилографа й цифрового вольтметра до виходу звукового генератора (рис.2).

- •Вимірювання періоду

- •Вимірювання параметрів імпульсного сигналу

- •1. Під'єднати вхід осцилографа до виходу імпульсного генератора.

- •Контрольні запитання

- •Лабораторна робота n 2

- •Мета роботи

- •Теоретичні відомості

- •Коротка технічна характеристика увтз-1м Номінальна напруга, в 220 Установка опору спрацювання 2100 Ом

- •Виконання роботи

- •Контрольні запитання

- •Теоретичні відомості

- •Основна технічна характеристика. Напруга живлення, в 220

- •Максимальний струм навантаження 15 а

- •Будова та принцип дії

- •В иконання роботи

- •Контрольні запитання

- •Теоретичні відомості

- •Технічна характеристика

- •Допустимі коливання напруги від номінального значення 15%

- •Будова та принцип роботи реле

- •Виконання роботи

- •Контрольні запитання

- •Основна технічна характеристика

- •Мета роботи

- •Теоретичні відомості

- •Перевірка конденсаторів на відсутність замикання

- •Перевірка електролітичних конденсаторів

- •Випробування транзисторів

- •Монтажні випробування транзисторів

- •Вимір внутрішнього опору омметра

- •Визначення основи транзистора

- •Випробування тріодних тиристорів

- •Контрольні запитання

Теоретичні відомості

Реле контролю трифазної напруги ЕЛ-10 призначене для захисту електродвигунів, тиристорних агрегатів та інших споживачів трифазного струму, при недопустимому зниженні симетричної напруги, оберненому чергуванні фаз, асиметрії трифазних напруг, а також для використання в системах керування.

Технічна характеристика

Номінальна напруга, В при частоті 50 Гі. 100, 110, 220, 300, 380, 400

Частоті 60 Гі. 220, 380.

Допустимі коливання напруги від номінального значення 15%

Реле спрацьовує при: зниженні напруги в будь-якій із фаз до величини 0,65-0,55 В від номінального значення і нижче, при номінальній напрузі в останніх фазах; обриві двох або трьох фаз одночасно;

подачі на реле трифазної напруги з оберненим чергуванням фаз; симетричному зниженні напруги до 0,75 - 0,7 номінального значення.

Кількість контактів, шт.:

замикаючих 1

розмикаючих 1

Будова та принцип роботи реле

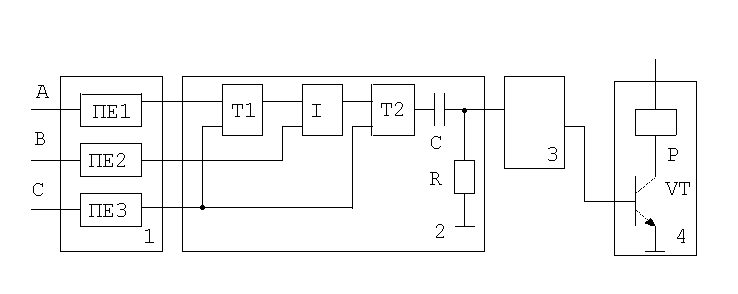

Реле контролю трифазної напруги ЕЛ-10 являє собою електронний пристрій, який має такі функціональні вузли, рис.1:

пороговий блок 1, який складається з трьох порогових елементів ПЕ1, ПЕ2, ПЕ3;

логічної схеми 2, що складається з двох тригерів Т1, Т2, логічної схеми "І" і диференцюючого кола R,C;

схеми часової витримки 3;

вихідного устрою, який складається із транзистора Т і вихідного реле Р.

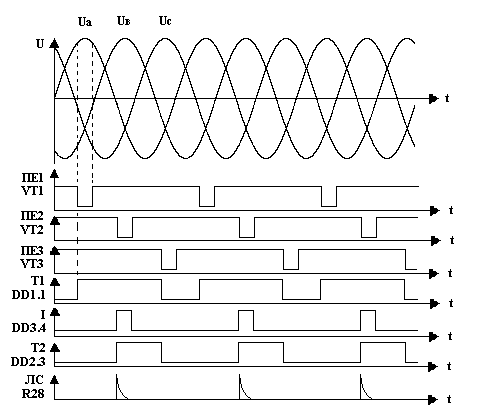

При подачі на вхід трифазної напруги допустимої величини на виходах порогового блоку (1) з’являється послідовність імпульсів з частотою і часовим зсувом відповідно діючої частоти і часового зсуву трифазної напруги. Часові діаграми, що ілюструють роботу реле, показані на рис.2.

Як видно з часових діаграм, на виході логічної схеми (2) має місце послідовність імпульсів тільки в тому випадку, коли на реле подана трифазна напруга з прямим порядком чергування фаз допустимої величини. Послідовність імпульсів з логічної схеми (2) подається на схему часової витримки (3),яка разом з вихідним пристроєм забезпечує вимкнення вихідного реле Р. При недопустимій зміні трифазної напруги або порядку чергування фаз на виході логічної схеми (2) зникає послідовність імпульсів і по закінченню

Рис.1 Реле контролю трифазної напруги ЕЛ-10:

1 - пороговий блок ПЕ1, ПЕ2, ПЕ3, порогові елементи; 2 - логічна схема; Т1, Т2 - тригери; R, С - диференцююче коло; 3 - схема часової витримки; 4 - вихідний пристрій: Т - транзистор; Р - вихідне реле.

витримки часу в схемі часової витримки (3) остання подає сигнал на вимкнення вихідного реле Р. Таким чином, за наявності на вході реле ЕЛ-10 трифазної напруги допустимої величини з прямим чергуванням фаз вихідне реле включене, а при виникненні аварійного режиму трифазної мережі вихідне реле вимикається з витримкою в часі.

Рис.2. Часові діаграми

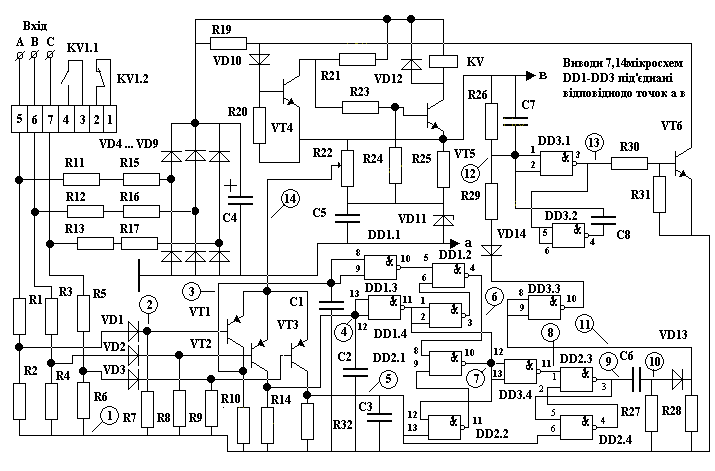

На рис. 3 наведена принципова електрична схема ЕЛ-10. Вона включає порогові елементи фаз А, В, С, які складаються з опорів R1...R10, R14, VD1...VD3, VT1...VT3); логічної схеми з елементами С1, С2, С3, DD1.1...DD1.4, DD3.4; двох RS тригерів на елементах DD2.1, DD2.2 і DD2.3, DD2.4; диференцюючого кола на елементах С6, R27; схеми часової витримки (елемен-ти VD13, R28, DD3.1...DD3.3, VD14, R29, R26, С8, R30,31, VT6); вихідного пристрою, який являє собою тригер Шмідта, зібраний на елементах VT4, VT5, R19...R25, VD10, VD12; вихідного реле Р; блока живлення на елементах R11…

Рис.3

R13, R15...R17; трифазного випрямляча VD4...VD9 C4, С5, VD11. Стабілітрон VD11 стабілізує напругу живлення мікросхем DD1...DD3.

Із вхідних клем 5, 6, 7 трифазна напруга через обмежуючі опори R11...R13, R15...R17 подається на трифазний випрямляч VD4...VD9 блока живлення і одночасно на подільник напруги на опорах R1...R6. Звідти через діоди VD1... VD3 сигнал подається на бази транзисторів VT1...VT3, що відповідно виконують функцію порогових елементів ПЕ1, ПЕ2, ПЕ3 фаз А,В,С.

Розглянемо роботу порогового елементу на транзисторі VT1. В момент, коли миттєва вхідна напруга фази А дорівнює нулеві (рис.2) транзистор VT1 відкритий за рахунок подачі від’ємного потенціалу через опір R9 на його базу. До опору R10, включеного в колекторне коло транзистора VT1, прикладається напруга живлення через відкритий транзистор VT1, яка регулюється змінним опором R22. Оскільки на базі транзистора діє однопівперіодна випрямлена синусоїдальна напруга (за рахунок діода VD1) в закриваючому напрямку, то при досягненні її певного значення транзистор VT1 закривається і знаходиться в такому стані доти, доки вхідна напруга на базі транзистора не зменшиться до величини відкриття транзистора VT1 (регулюється потенціометром R22). Отже на резисторі R10 формуються імпульси напруги з частотою 50 Гц. Робота ПЕ2 і ПЕ3 на транзисторах VT2 і VT3 аналогічна роботі ПЕ1 на VT1 з урахуванням того, що імпульси сформовані пороговими елементами, зсунуті по фазі один від одного на 120 ел. градусів (рис.2).Таким чином, на опорах R10, R14, R32 ми маємо імпульси, зсунуті один від одного на 120 ел. градусів. Ці імпульси подаються на входи логічних елементів DD1.1, DD1.3, DD2.2 і DD2.4. Логічні елементи DD1, DD2, DD3.4 з’єднані таким чином, що на виході елемента DD2.3 ми маємо послідовність імпульсів при правильному чергуванні фаз на порогових елементах. В усіх інших випадках на виході логічного елементу DD2.3 не змінний вихідний рівень сигналу.

Розглянемо роботу схеми логічного блока при правильному чергуванні фаз. Припустимо, що транзистор VT1 закритий, а VT2 і VT3 відкриті, тоді на вході логічного елементу DD1.1 діє напруга логічного нуля, а на входах елементів DD1.3, DD2.2, DD2.4 - логічної одиниці. При цьому співвідношенні вхідних логічних напруг вихідна напруга логічних елементів встановлюється таким чином: логічна "1" дії на виходах елементів DD1.1, DD1.4, DD2.1, DD3.4, логічний "0" дії на виходах DD1.3, DD1.2, DD2.2, DD2.3. Наступний цикл роботи: VT1, VT3 відкриті, VT2 закритий. При цьому вхідному алгоритмі відбувається перемикання тригера Т2, зібраного на елементах DD2.3, DD2.4, на виході DD2.3 з'являється логічна "1". Стан тригера Т1 на елементах DD2.1, DD2.2 не змінюється. рис. 2. Останній цикл (далі цикли повторюються) VT1, VT2 відкриті, VT3 - закритий. Відбувається перемикання тригерів Т1 і Т2 отже на виходах мікросхем DD2.1 DD2.3, з’являється логічний "0". Таким чином при правильному чергуванні фаз на виході елемента DD2.3 ми маємо серію прямокутних імпульсів частотою 50 Гц., що диференціюються колом, яке складається з С6, R27. Через роздільний діод VD13 імпульси подаються на вхід інвертора DD3.3, з виходу останнього - на вхід вузла затримки, який працює так. Вхід елемента DD3.1 через інвертор DD3.3 підключається до мінусової шини живлення під час дії на вході DD3.3 імпульсів, які надходять з логічного блока. Це не дозволяє заряджатися конденсатору С8 до напруги включення DD3.1. Отже, на виході DD3.1 присутній високий логічний рівень. Транзистор VТ6 відкритий, VТ4 закритий і VT5 відкритий. Котушка реле КV через відкритий транзистор VT5 підключена до джерела живлення. При обриві фази або при оберненому їх чергуванні, зниженні напруги живлення нижче встановленого значення на виході тригера Т2 (вихід мікросхеми DD2.3) імпульси відсутні, отже на виході елемента DD3.3 діє логічна одиниця. Це дозволяє конденсатору С8 через опір R26 зарядитися до напруги живлення через вихід DD3.2. На вході мікросхеми DD3.1 з’являється логічна "1", на виході "0". З виходу DD3.1 логічний "0" подається на вхід інвертора DD3.2, що відключає нижню обкладинку конденсатора С8 від мінуса джерела живлення. Одночасно логічний "0" через опір R30 подається на базу транзистора VT6, останній закривається, спрацьовує тригер на транзисторах VТ4 і VT5, реле КV вимикається.