- •Введение.

- •Глава 1. Первый уровень иерархии систем автоматизации и управления – логические элементы Лабораторная работа №1. Логические элементы малой степени интеграции.

- •1.1 Формальный язык описания логических элементов.

- •1.2. Функционально полные наборы логических элементов.

- •Элемент и – не Элемент или – не

- •1.4 Работа в среде графического программирования LabView.

- •Типа не и и-не.

- •1.5. Порядок выполнения лабораторной работы №1.

- •Лабораторная работа №2. Логические элементы средней степени интеграции.

- •1.8. Порядок выполнения лабораторной работы №2.

- •Глава 2. Первый уровень иерархии систем автоматизации и управления – элементы памяти Лабораторная работа №3. Изучение принципов работы элементов памяти

- •2.1 Элементы памяти.

- •2.2 Конечные автоматы средней степени интеграции – двоичные счетчики и регистры

- •2.2.1. Счётчики импульсов

- •2.3. Работа в среде визуального редактора Visual Basic 6.0.

- •2.3.1. Интерфейс и форма

- •2.3.2. Программа выполнения логических операций с переменными типа «Byte».

- •2.3.3. Программа выполнения логических операций с переменными типа «Boolean».

- •2.4. Порядок выполнения лабораторной работы №3.

- •Глава 3. Первый уровень иерархии систем автоматизации и управления – элементы силовой электроники

- •3.1 Элементы силовой электроники систем управления

- •3.2 Устройства связи с объектами (усо).

- •Глава 4. Второй и третий уровни иерархии систем автоматизации и управления – микропроцессоры и контроллеры Лабораторная работа №4. Изучение принципов работы контроллера

- •4.1 Контроллер.

- •4.3 Создание управляющей программы контроллера.

- •4.3. Порядок выполнения лабораторной работы №4.

- •Глава 5. Создание программы управления объектом Лабораторная работа №5. Изучение процесса проектирования системы автоматизированного управления 5-го уровня иерархии.

- •5.1 Некоторые положения языка с, наиболее часто применяемые при программировании контроллеров.

- •If (выражение) оператор_1 else оператор_2

- •5.2 Программа обмена информацией между управляющей эвм и контроллером

- •Текст программы управления обменом информацией для контроллера через универсальный асинхронный приёмопередатчик – uart.

- •5.3 Порядок выполнения лабораторной работы №5

- •Заключение

- •Библиографический список

- •Глава 1. Первый уровень иерархии систем автоматизации и

- •Глава 2. Первый уровень иерархии систем автоматизации

- •2.2 Конечные автоматы средней степени интеграции – двоичные счетчики и регистры…………………………………..24

- •Глава 3. Первый уровень иерархии систем автоматизации

- •Глава 4. Второй и третий уровни иерархии систем автоматизации

- •Глава 5. Создание программы управления объектом……………………...52

1.8. Порядок выполнения лабораторной работы №2.

Цели работы: изучить способы формального описания работы комбинационных схем средней степени интеграции: шифраторов, дешифраторов, сумматоров и способов их моделирования.

Для этого: составить таблицы истинности для трёхразрядного двоичного дешифратора и одноразрядного сумматора двоичных чисел, записать законы функционирования в СДНФ и промоделировать их работу в среде LabVIEW. При составлении таблицы истинности для сумматора следует учитывать возможность переноса 1 из младшего разряда.

Отчёт о проделанной работе должен включать таблицы истинности, все алгебраические преобразования переключательных функций и схемы всех экспериментов в среде LabVIEW .

Глава 2. Первый уровень иерархии систем автоматизации и управления – элементы памяти Лабораторная работа №3. Изучение принципов работы элементов памяти

2.1 Элементы памяти.

Для описания законов функционирования элементов памяти и устройств, работающих на их основе используется теория конечных автоматов [5,25]. Элемент памяти является элементарным автоматом, имеющим два устойчивых состояния, кодируемых 0 и 1. Работа элементарного автомата осуществляется в дискретные моменты времени (такты). Соседние такты обозначаются символами (t) и (t+1). Алгоритм его работы задаётся таблицей переходов (табл. 2.1), определяющей зависимость переходов элементарного автомата из состояния Q(t)в такте t в состояние Q(t+1) в такте t+1 в зависимости от значений входных сигналов X(t).

Таблица 2.1

|

X1(t) |

X2(t) |

Q(t) |

Q(t+1) |

|

0 |

0 |

0 |

– |

|

0 |

0 |

1 |

– |

|

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

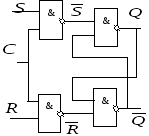

Рис.2.1. Схема бистабильной ячейки (триггера) и таблица переходов.

Сначала построим схему бистабильной ячейки (триггера), которая может находиться в двух устойчивых состояниях, на логических элементах И – НЕ (рис. ). Для этого триггера активным является сигнал нулевого уровня. Поэтому состояние входов X1(t) = 0 и X2(t) = 0, которое приводит к появлению на обоих выходах сигнала 1, называется запрещённым, а состояние выхода Q(t+1) называется неопределённым. Состояние входов X1(t) = 0, X2(t) =1 переводит триггер в состояние 1, независимо от предыдущего состояния, а состояние входов X1(t) = 1, X2(t) =0 – в состояние 0. Если же X1(t) = 1 и X2(t) =1, то триггер сохраняет предыдущее состояние (табл. 2.1).

Таблица 2.2

|

S(t) |

R(t) |

Q(t) |

Q(t+1) |

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

– |

|

1 |

1 |

1 |

– |

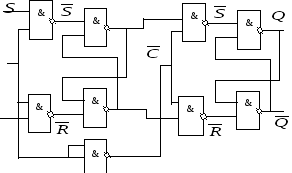

Рис.2.2. Схема и таблица переходов SR-триггера, тактируемого потенциалом.

В

реальных схемах триггеров изменение

состояния происходит в фиксированные

моменты времени, определяемые сигналом

на тактовом входе C.

Схема и таблица переходов такого триггера

приведены на рис.2.2. В этом триггере

изменение состояния возможно только

при единичном значении сигнала на входе

синхронизации С. Теперь для установки

триггера в единичное состояние

необходимо, чтобы S(t) = 1, R(t) = 0, а для

установки в нулевое состояние - S(t) = 0,

R(t) = 1. Состояние входов S(t) = 1, R(t) = 1 является

запрещённым, а состояние выхода

триггера Q(t+1) при этом не определено.

Такой элементарный автомат называют

S-R триггером, тактируемым потенциалом.

Обозначение входов S

и R

происходит от английских слов Set

– установить и Reset

– переустановить. В некоторых случаях

необходимо, чтобы триггер срабатывал

в строго определённый момент времени,

например в момент изменения уровня

синхросигнала, Такой триггер называется

триггером, тактируемым фронтом (перепад

0 – 1) или срезом (перепад 1 – 0) синхроимпульса.

Схема SR

триггера, тактируемого срезом, приведена

на рисунке 2.3. Работает триггер следующим

образом. В момент установки С входа в

состояние 1 сигналы со входов S

и R

записываются в первую бистабильную

ячейку и поступают на входы второй. Но

быть записанными во вторую ячейку они

не могут, так как на её входе синхронизации

установлен запрещающий нулевой уровень

сигнала

![]() .

При изменении сигнала синхронизации С

из 1 в 0, сигнал

.

При изменении сигнала синхронизации С

из 1 в 0, сигнал![]() примет значение 1 и информация будет

записана во вторую бистабильную ячейку.

При этом запись информации в первую

ячейку будет запрещена, и можно установить

новые значенияS

и R входов.

примет значение 1 и информация будет

записана во вторую бистабильную ячейку.

При этом запись информации в первую

ячейку будет запрещена, и можно установить

новые значенияS

и R входов.

![]()

![]()

Рис.2.3. Схема SR триггера, тактируемого срезом (перепадом 1 – 0) синхросигнала

Триггер типа SR называется элементарным автоматом с двумя информационными входами. Существуют элементарные автоматы с одним информационным входом. Это элементарные автоматы типа Т (триггер со счётным входом, таб. 2.3) и D (триггер задержки, таб. 2.4). Их переходы отображены в следующих таблицах.

Таблица 2.3 Таблица 2.4

-

q(t)

Q(t)

Q(t+1)

0

0

0

0

1

1

1

0

1

1

1

0

q(t)

Q(t)

Q(t+1)

0

0

0

0

1

0

1

0

1

1

1

1

В этих таблицах q(t) – входной сигнал в момент времени t, Q(t) – состояние элементарного автомата в момент времени t, Q(t+1) – состояние элементарного автомата в момент времени t+1 (в следующем такте).

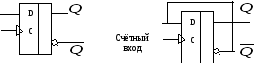

Триггер со счётным входом работает так: при подаче на вход сигнала 0 триггер не меняет своего состояния, а при подаче сигнала 1 – меняет состояние на противоположное, то есть считает до двух. В технических схемах t-триггер обычно реализуется на основе D-триггера или JK-триггера (рис.2.4).

У триггера задержки состояние автомата в момент времени Q(t+1) равно значению входа в момент времени q(t) , то есть повторяет значение входного сигнала с задержкой на 1 такт. Название D-триггер происходит от английского слова delay – задержка.

Рис.2.4. D-триггер и t-триггер, построенный на основе D-триггера

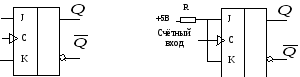

Разработан триггер с двумя информационными входами типа JK, для которого не существует запрещённого состояния входов. Если на его входы J (Jump) и K (Keep), соответствующие входам S и R предыдущего триггера, подать сигналы J=1 и K=1, то триггер изменит состояние на противоположное при подаче на вход С перепада 1 – 0. Такой переход позволяет из JK триггера получить триггер со счётным входом. Схема такого триггера представлена на рис. 2.5.

Рис.2.5. JK-триггер и t-триггер, построенный на основе JK-триггера