- •Введение.

- •Глава 1. Первый уровень иерархии систем автоматизации и управления – логические элементы Лабораторная работа №1. Логические элементы малой степени интеграции.

- •1.1 Формальный язык описания логических элементов.

- •1.2. Функционально полные наборы логических элементов.

- •Элемент и – не Элемент или – не

- •1.4 Работа в среде графического программирования LabView.

- •Типа не и и-не.

- •1.5. Порядок выполнения лабораторной работы №1.

- •Лабораторная работа №2. Логические элементы средней степени интеграции.

- •1.8. Порядок выполнения лабораторной работы №2.

- •Глава 2. Первый уровень иерархии систем автоматизации и управления – элементы памяти Лабораторная работа №3. Изучение принципов работы элементов памяти

- •2.1 Элементы памяти.

- •2.2 Конечные автоматы средней степени интеграции – двоичные счетчики и регистры

- •2.2.1. Счётчики импульсов

- •2.3. Работа в среде визуального редактора Visual Basic 6.0.

- •2.3.1. Интерфейс и форма

- •2.3.2. Программа выполнения логических операций с переменными типа «Byte».

- •2.3.3. Программа выполнения логических операций с переменными типа «Boolean».

- •2.4. Порядок выполнения лабораторной работы №3.

- •Глава 3. Первый уровень иерархии систем автоматизации и управления – элементы силовой электроники

- •3.1 Элементы силовой электроники систем управления

- •3.2 Устройства связи с объектами (усо).

- •Глава 4. Второй и третий уровни иерархии систем автоматизации и управления – микропроцессоры и контроллеры Лабораторная работа №4. Изучение принципов работы контроллера

- •4.1 Контроллер.

- •4.3 Создание управляющей программы контроллера.

- •4.3. Порядок выполнения лабораторной работы №4.

- •Глава 5. Создание программы управления объектом Лабораторная работа №5. Изучение процесса проектирования системы автоматизированного управления 5-го уровня иерархии.

- •5.1 Некоторые положения языка с, наиболее часто применяемые при программировании контроллеров.

- •If (выражение) оператор_1 else оператор_2

- •5.2 Программа обмена информацией между управляющей эвм и контроллером

- •Текст программы управления обменом информацией для контроллера через универсальный асинхронный приёмопередатчик – uart.

- •5.3 Порядок выполнения лабораторной работы №5

- •Заключение

- •Библиографический список

- •Глава 1. Первый уровень иерархии систем автоматизации и

- •Глава 2. Первый уровень иерархии систем автоматизации

- •2.2 Конечные автоматы средней степени интеграции – двоичные счетчики и регистры…………………………………..24

- •Глава 3. Первый уровень иерархии систем автоматизации

- •Глава 4. Второй и третий уровни иерархии систем автоматизации

- •Глава 5. Создание программы управления объектом……………………...52

Глава 4. Второй и третий уровни иерархии систем автоматизации и управления – микропроцессоры и контроллеры Лабораторная работа №4. Изучение принципов работы контроллера

4.1 Контроллер.

Раньше это определение относилось к небольшой вычислительной машине, управляющей отдельным агрегатом или процессом. Теперь, с ростом вычислительной мощности этих устройств, они находят всё более широкое применение в различных регуляторах промышленных и бытовых установок, а маленькие размеры позволяют включать их в конструкции агрегатов, которыми они должны управлять.

В функционально полный набор элементов контроллера должны

входить:

ЦПУ (CPU) – центральное процессорное устройство,

УВВ (I/O) - устройства ввода-вывода для последовательного и параллельного обмена информацией,

схемы памяти - постоянной (ПЗУ) и оперативной (ОЗУ).

Однако, для повышения универсальности и быстродействия, в состав контроллера могут быть включены

таймер для поддержки режима реального времени,

устройство прерываний для организации перехода к другой программе по внешнему сигналу,

АЦП (ADC) - аналого-цифровой преобразователь сигналов,

устройство отображения информации, например ЖКИ (LCD) – жидко- кристаллический индикатор.

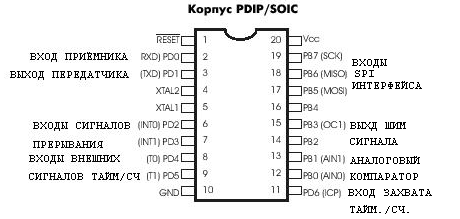

В качестве объекта изучения используем контроллер фирмы Atmel AT90S2313 или его более новую модификацию Atiny2313 [16,17,18]

Функциональная схема контроллера представлена на рис.4.1.

Перейдём теперь к изучению его основных узлов. Посмотрим, какие устройства, входящие в состав контроллера, должны выполнять минимально необходимые функции управления:

сбор информации о состоянии объекта управления - параллельные порты ввода / вывода информации (Ports B,D),

входы для подачи внешних сигналов прерывания выполнения программы (External IRQ),

передачу информации на пункт обработки - универсальный асинхронный приёмник-передатчик (UART),

обработку информации согласно алгоритму и формирование команды управления - центральный процессор, таймеры (CPU, Timers),

передачу команды системам управления исполнительными механизмами объекта управления - параллельные порты ввода / вывода информации (Ports B,D),

управление приводом (включение и выключение силового питания, регулирование скорости) в соответствии с выбранным алгоритмом - такое устройство имеется в составе специальных контроллеров.

Рис.4.1. Функциональная схема микроконтроллера AT90S2313.

Устройства, входящие в состав контроллера, являются программируемыми и поэтому в каждом из них есть вспомогательные регистры, где хранится информация о состоянии устройства и выполняемой им функции в текущий момент времени. Эти регистры имеют имена и называются регистрами данных (xDR - Data Register), регистрами управления (xCR - Control Register) и регистрами состояния (xSR - Status Register). Символ х обозначает имя устройства, которому принадлежит регистр, например UDR - UART Data Register. Управление режимами работы контроллера осуществляется путём установки в определённое состояние битов регистра управления, а состояние контроллера в конкретный момент выполнения алгоритма отображается с помощью установки в соответствующее состояние битов регистра статуса. Для установки битов командного регистра ему в программе присваивается конкретное значение, которое иногда называют словом команды, а состояние устройства определяется путём считывания значения соответствующего регистра (слова состояния). Знание правил установки битов управляющих регистров необходимо, так как изменить режим работы устройства может оказаться нужным в любом месте программы. Их подробное описание приведено в технических описаниях контроллеров.

Работу каждого устройства, входящего в состав контроллера нужно программировать и этот процесс должен быть автоматизирован. Для этого используем программу CodeVisionAVR, демоверсия которой (не для коммерческого использования распространяется в Internet [19]. После открытия нового проекта, в нашем распоряжении окажется ряд диалоговых окон. где нужно поставить имена, цифры и отметки в соответствии с нашими требованиями к проектируемой системе. Эти окна для контроллера AT90S2313 имеют следующий вид (см.рис. 4.2, 4.4 и 4.5):

Рис. 4.2. Диалоговые окна для выбора типа контроллера и настройки порта В.

Chip (Микросхема). Установим тип контроллера AT90S2313 и его рабочую частоту 7,3728 МГц, которая определяется характеристикой кварцевого резонатора.

Отметим, что все пояснения к содержанию окон, написанные на английском языке, скрываются за клавишей Help.

Ports (Порты). Порт В может быть использован для обычного двунаправленного обмена информацией с другими внешними устройствами. Однако, некоторые его выводы используются для реализации специальных функций, таких как приём сигналов внешних прерываний, сигналов записи программ во Flash-память, выдача ШИМ-сигнала и некоторых других. Основное и дополнительное назначение выводов микросхемы показано на рис 4.3. Установим, что B0 - B3 выводы порта B работают как выходные (Out), а В4 - В7 как входные (In). Пусть выводы порта D работают как входные (In), за исключением 1-го вывода D.1, который является выходом асинхронного передатчика (TxD)и поэтому также должен быть настроен на выход. Эта информация в тексте программы будет записана шестнадцатеричном коде в регистры направления передачи данных - DDRB или DDRD.

Рис.4.3. Обозначения выводов корпуса контроллера AT90S2313.

External IRQ (Запрос внешнего прерывания).

Для организации внешнего прерывания используются 6 и 7 выводы микросхемы, причём может быть выбран низкий (Low Level) уровень, фронт (Rising Edge) или срез (Falling Edge) сигнала. Результатом заполнения этого окна в программе будет вызов функции прерывания с приглашением написать программу обработки прерывания "Place your code here".

Timer (Таймер). В состав контроллера входят 2 таймера - 8-и разрядный Таймер 0 и 16-разрядный Таймер 1. Рассмотрим работу Таймера 1, так как функции, выполняемые Таймером 1, включают в свой состав и функции Таймера 0. Таймер является обычным счётчиком с некоторыми дополнительными свойствами, которые могут быть заданы программно.

Рис.4.4 Диалоговые окна IRQ и Timer1

Для формирования тактовых сигналов может быть использован внутренний (System Clock) или внешний источник, причём внутренний источник имеет предварительный делитель, позволяющий выбирать частоты, указанные в меню, а внешний источник вызывает срабатывание таймера в момент возникновения тактового импульса (T1 pin Rising Edge) или в момент его окончания (T1 pin Falling Edge). Сигналы от внешнего генератора подаются на 8 (Т0)и 9(Т1) выводы микросхемы. Таймер может быть использован для формирования ШИМ сигнала (8, 9, 10 bit Pulse Width Modulation) с инвертированным или не инвертированным (Non-Inv) выходом (В3 вывод порта В). Выход таймера может быть отключен, включен, установлен в 0 или 1 (Outpt: Disconnect, Toggle, Clear, Set). Таймер используется также для формирования команды прерывания (Interrupt on) при переполнении счётчика (Timer1 Overflow), при совпадении содержимого счётчика с заданным порогом (Compare Match) и по внешнему сигналу (Input Capture) с выдачей информации о содержимом счётчика в момент поступления сигнала (чтение "на лету"). После окончания процедуры сравнения (Compare Math) таймер может быть установлен в 0 путём установки флага Clear Timer. Кроме того, таймер может выполнять следующие функции:

- Inp. - устанавливает момент захвата при чтении "на лету" по фронту внешнего импульса (Input Capture) и включает режим подавления шума Noise Cancel,

- Timer Value - устанавливает начальное состояние счётчика,

- Cmp. - устанавливает значение порога сравнения в режиме Compare Math.

Все режимы работы таймера задаются путём установки в определённое состояние регистров управления TCCR1A (Timer/Counter 1 Control Register A) и TCCR1B (Timer/Counter 1 Control Register B), регистра сравнения выхода таймера/счётчика 1 - OCR1H и OCR1L (Output Compare Register ) и регистра захвата входа таймера/счётчика 1 - ICR1H и ICR1L (Input Capture Register). Значение таймера в процессе счёта хранится в регистре TCNTH и TCNTL. После генерации программы все управляющие регистры таймера будут установлены в заданное первоначальное состояние, а в тексте программы появятся вызовы функций прерывания и приглашения описать желаемые процедуры прерывания.

Рис.4.5. Диалоговое окно UART и LCD

UART (Universal Asynchronous Receiver Transmitter - Универсальный асинхронный приёмопередатчик). UART предназначен для обмена информацией в последовательном коде с другими контроллерами так же имеющими в своём составе UART или с ЭВМ через СОМ-порт. UART может работать в режиме приёма, передачи или в дуплексном режиме приёма и передачи. Так как передача ведётся асинхронно, то необходимо определять моменты начала и конца передачи. В контроллере для этого используется стартовый бит низкого уровня и один или два стоповых бита высокого уровня, между которыми располагаются семь или восемь бит данных и бит проверки на чётность (нечётность). Кроме режима работы программируется размер буфера для накопления информации, скорость и параметры передачи сигналов.

Для организации процесса передачи используются следующие регистры.

UDR – регистр ввода / вывода информации, где хранится принимаемая и передаваемая информация.

UCR – командный регистр, в котором должны быть установлены:

бит RXC (Receive Complete – приём окончен) – вызов функции прерывания для обработки принятой информации,

бит TXC (Transmit Complete – передача окончен) – вызов функции обработки прерывания для передачи нового слова

USR – регистр состояния, в котором должны быть установлены:

бит RXCIE (RX Complete Interrupt Enable) – разрешение прерывания по RXC флагу,

бит TXCIE (TX Complete Interrupt Enable) – разрешение прерывания по TXC флагу,

бит UDRIE (UART Data Register Empty Interrupt Enable) – разрешение прерывания по UDRE флагу,

бит RXEN (Receiver Enable) – доступность буфера приёмника,

бит TXEN (Transmitter Enable) – доступность буфера передатчика

UBRR (UART Baud Rate Register) – регистр скорости передачи.

Скорость передачи (Baud Rate) может изменяться в широких пределах и зависит от характеристик канала связи - от 9600 до 115200 бод. Параметры сигналов (Communication Parameters) говорят о том, что данные в передаваемом слове занимают 8 бит, стоп - 1 бит и нет проверки на чётность. Эти параметры тоже могут меняться и их значения приводятся в меню окна. Приём информации происходит по сигналу прерывания, который формируется в момент распознавания стартового бита путём установки флага RxC (UART Receive Complete ) в регистре состояния. Прерывание программы для передачи происходит в момент передачи информации в регистр данных контроллера (UDR) путём установки флага TxC (UART Transmit Complete) в регистре состояния.

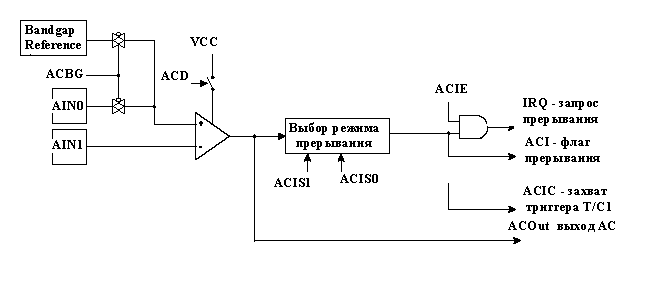

AC (Analog Comparator - Аналоговый компаратор)

Аналоговый компаратор сравнивает уровни на положительном выводе AC+ и отрицательном выводе AC-. При напряжении на положительном выводе AC+ большем, чем напряжение на отрицательном выводе AC-, выход аналогового компаратора ACO устанавливается в состояние 1. Аналоговый компаратор может формировать запрос прерывания. Пользователь может задать формирование запроса на прерывание по фронту, по срезу импульса или по переключению. Кроме того, выход компаратора может быть использован для управления входом захвата таймера/счетчика1 (T/C1). Блок-схема аналогового компаратора показана на рис.4.6.

Рис4.6. Функциональная схема аналогового компаратора.

Управление работой аналогового компаратора осуществляется через регистр статуса и управления ACSR - (The Analog Comparator Control and Status Register). Его структура представлена в таблице 4.1.

Таблица 4.1

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

ACD |

ACBG |

ACO |

ACI |

ACIE |

ACIC |

ACIS1 |

ACIS0 |

|

R/W |

R/W |

R |

R/W |

R/W |

R/W |

R/W |

R/W |

Bit 7 - ACD: Analog Comparator Disable - Запрет работы аналогового компаратора при установленном в состояние 1 бите ACD. При изменении состояния бита ACD необходимо запрещать прерывание работы аналогового компаратора очисткой бита ACIE в регистре ACSR. В противном случае при изменении состояния бита ACD может произойти прерывание.

Bit 6 – ACBG: Analog Comparator Bandgap Select. При установке этого бита в 1 в качестве положительного уровня для сравнения используется внешний сигнал AIN0.

Bit 5 - ACO: Analog Comparator Output - Выход аналогового компаратора

Bit 4 - ACI: Analog Comparator Interrupt Flag- Флаг прерывания работы аналогового компаратора. Данный бит устанавливается в состояние 1 в случае формирования компаратором прерывания, определяемого битами ACIS1 и ACIS0. Подпрограмма обработки прерывания по аналоговому компаратору будет выполняться при установленном бите ACIE и установленном бите глобального прерывания в регистре SREG. Бит ACI очищается аппаратно при выполнении соответствующего вектора обработки прерывания.

Bit 3 - ACIE: Analog Comparator Interrupt Enable - Разрешение прерывания по сигналу аналогового компаратора. При установленном бите ACIE и установленном бите разрешения глобального прерывания регистра SREG прерывание активируется.

Bit 2 - ACIC: Analog Comparator Input Capture enable - разрешение функции захвата входа таймера/счетчика1(Т/С1) по переключению аналогового компаратора. В этом случае выход аналогового компаратора подсоединяется непосредственно ко входной цепи логики захвата входа, что обеспечивает использование функций подавления шума и выбора вида срабатывания прерывания по захвату входа таймера/счетчика1. При очищенном бите ACIC соединения нет. Для запуска прерывания по захвату входа таймера/счетчика1 бит TICIE1 в регистре масок прерываний TIMSK должен быть установлен в состояние 1.

Bits 1,0 - ACIS1, ACIS0: Analog Comparator Interrupt Mode Select - Выбор режима прерывания по аналоговому компаратору. Эти биты определяют характер события компаратора, при котором запускается прерывание по аналоговому компаратору. Варианты установок показаны в таблице 4.2.

Таблица 4.2.

|

ACIS1 |

ACIS0 |

Режим прерывания |

|

0 |

0 |

Прерывание по переключению |

|

0 |

1 |

Зарезервировано |

|

1 |

0 |

Прерывание по срезу импульса |

|

1 |

1 |

Прерывание по фронту импульса |

При изменении состояния битов ACIS1/ACIS0 прерывание по сигналу аналогового компаратора должно быть запрещено очисткой бита разрешения прерывания в регистре ACSR. В противном случае при изменении состояния битов может произойти прерывание.

В микросхеме Attiny2313 в составе аналогового компаратора входит регистр DIDR – Digital Input Disable Register.

Его биты Bit 1,0 – AIN1D, AIN0D во время работы аналогового компаратора устанавливаются в 1 для снижения энергопотребления.

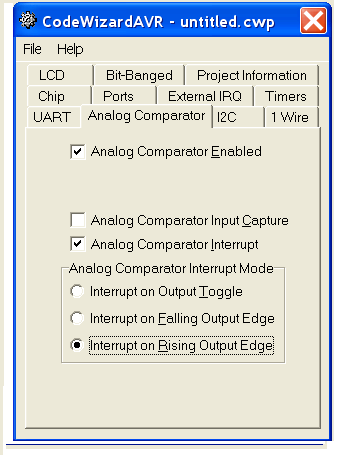

Начальная установка регистра управления и статуса аналогового компаратора может быть произведена с помощью автоматического генератора программ CodeVision AVR. Диалоговое окно аналогового компаратора изображено на рис.4.7.

Аналоговый компаратор в системах управления используется для решения важной задачи защиты силовых цепей от перегрузки.

Программирование оставшихся устройств контроллера – линии связи с жидкокристаллическим дисплеем LCD, с другими внешними устройствами I2Cи 1-Wire рассматривать не будем, так как они в лабораторных работах по этому курсу не используются. На этом этап установки контролллера в начальное состояние заканчивается.

Рис. 4.7. Диалоговое окно аналогового компаратора