- •Аппаратные средства вычислительной техники

- •Элементы и узлы эвм Системный блок

- •Корпуса

- •Блок питания

- •Кабели и разъемы

- •Проводники

- •Системная плата

- •Корпуса и маркировка

- •Накопители

- •Винчестеры

- •Цифровая информация

- •Флоппи диски (fdd)

- •Стримеры

- •Прочие накопители

- •Накопители на эффекте Бернулли

- •Накопитель на компакт дисках

- •Магнитооптические накопители

- •Видеоподсистемы

- •Lr мониторы

- •Green мониторы

- •Видеоадаптеры

- •Проблемы цветопередачи

- •Карта ускорителей

- •Рекомендации по выбору видеоадаптера

- •Структура центрального процессора

- •Микропроцессорные устройства. Основные понятия

- •Разрядность адресов и данных;

- •Организация структуры памяти Организация памяти микропроцессорных устройств

- •Теги и дескрипторы

- •Особенности risc _ архитектуры

- •Согласование пропускных способностей микропроцессора и памяти. Кэш-память

- •Защита памяти

- •Динамическое распределение памяти. Организация виртуальной памяти

- •Организация памяти

- •Режимы работы памяти

- •Другие типы динамической памяти

- •Логическая организация памяти

- •Дополнительная память

- •Расширенная память

- •Устройства оперативной памяти

- •Bios и cmos ram

- •Кэширование адреса

- •Системы прерывания Прерывания и исключения

- •Системы ввода вывода Организация ввода - вывода микропроцессорного устройства

- •Ввод вывод в режиме прямого доступа к памяти

- •Ввод вывод

- •Защищенный режим

- •Дескрипторы

- •Привилегии

- •Переключение задач

- •Страничное управление памятью

- •Режим виртуального 86 (v86)

- •Переферийные устройства Интерфейсы периферийных устройств

- •Последовательный порт

- •Организация памяти микропроцессорного устройства

- •Регистры микропроцессора

- •Адресация ввода вывода

- •Инициализация прерывания останов и синхронизация микропроцессора

- •Задание типа работы микропроцессора

- •Шинные циклы микропроцессора

- •Основные особенности архитектур микропроцессоров 286, 386 и 486 Общие характеристики структуры

- •Вспомогательные микросхемы для смпу. Системные локальные шины Тактовый генератор

- •Контроллер прерываний

- •Контроллер прямого доступа к памяти

- •Другие вспомогательные микросхемы

- •Набор микросхем или chipset

- •Системные локальные шины

- •Шина isa

- •Шина esa

- •Локальные шины

- •Стандарт pcmcia

- •Архитектура современного эвм расширение mmx

- •Внутренний кэш

- •Синхронизация

- •Разгон и торможение процессора

- •Варианты разгона Pentium

- •Логическая структура диска

- •Структура br (бутсектора)

- •Архитектура ориентированная на программное обеспечение Интерфейс накопителей

- •Интерфейс ata (ide)

- •Интерфейс Enhanced ide

Системы ввода вывода Организация ввода - вывода микропроцессорного устройства

Ввод _ вывод _ это процесс обмена данными между ядром микропроцессорного устройства и периферийными устройствами. В микропроцессорном устройстве применяют три режима:

программный;

по прерываниям;

прямой доступ к памяти.

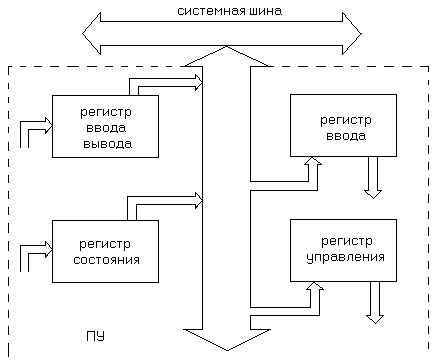

Группа бит, к которым обращается микропроцессор при вводе _ выводе, называется портом или регистром ввода _ вывода. При вводе выводе периферийные устройства представлены следующей программной моделью (рис.10).

Все реестры имеют адрес, в зависимости от конкретной реализации порты могут объединяться. Признак готовности периферийного устройства к вводу _ выводу обычно содержится в одном из разрядов порта состояния, различают изолированный и неизолированный ввод _ вывод. В первом случае в системе команд есть специальные команды ввода _ вывода, в которых содержится номер порта, указываемый во втором слове код операции ввода _ вывода. Адресное пространство портов и ячеек памяти в этом случае изолированы, так как для пересылки в память имеются особые команды. В этом случае адреса портов ввода _ вывода, некоторых, ячеек могут совпадать. Во втором случае адресные пространства едины и совпадения адресов нет. При постоянном способе ввода _ вывода инициализируется программой выполняемой в микропроцессорном устройстве. При вводе _ выводе важна проверка готовности периферийного устройства, то есть состояние определяющего бита порта состояния. В некоторых микропроцессорах, это делается независимо от вида команды и при неготовности периферийного устройства микропроцессор переходит в состояние ожидания. Тем самым достигается согласование во времени работы микропроцессора и более медленных периферийных устройств. При асинхронном вводе _ выводе в программу включаются специальные команды проверки готовности.

Микропроцессор проверяет бит готовности с помощью одной или нескольких команд. Если бит установлен в единицу, то инициируется собственно ввод или вывод одного или нескольких слов данных. Если бит сброшен, то микропроцессор выполняет цикл из двух-трех команд, проверяющих состояние бита до тех пор пока периферийное устройство не будет готово к вводу выводу. Этот цикл называется циклом ожидания. Из-за него микропроцессор непроизводительно теряет время, что является главным недостатком программного ввода вывода, достоинство: простота реализации без дополнительных аппаратных затрат.

Ввод вывод по прерываниям лишен недостатка программного ввода вывода и применяется при работе в реальном времени. Периферийное устройство подает сигнал `запрос прерывания' на соответствующий вход микропроцессора. Микропроцессор после выполнения текущей команды приостанавливает выполнение основной программы, вырабатывает сигнал подтверждения прерывания и переходит к подпрограмме обработки прерывания, расположенной в фиксированной области памяти. После выполнения этой подпрограммы происходит возврат к основной программе. Для реализации подпрограммы обработки прерывания в микропроцессоре должны выполнятся следующие действия:

идентификация источника прерывания;

сохранение состояния основных регистров микропроцессора с тем, чтобы обеспечить возможность возобновления прерванной программы;

собственное выполнение программы обработки прерывания;

восстановление запомненного состояния основных регистров микропроцессора;

возврат к выполнению основной программы.

Данная последовательность действий может реализоваться в двух вариантах : с опросом периферийных устройств и по вектору прерывания. Наиболее распространенным является второй способ. В этом случае в ответ на сигнал подтверждения прерывания периферийное устройство посылает в микропроцессор параллельный двоичный код, вектор прерывания по которому управление передается соответствующей подпрограмме обслуживания прерываний. При наличии нескольких периферийных устройств возможна ситуация при которой во время обслуживания запроса прерывания от одного периферийного устройства поступает запрос от другого. Если оно более приоритетно, то происходит вложение прерываний ( т.е. прерывание прерывания). Для создания систем приоритетных прерываний используются контроллеры прерываний. С помощью специальных команд запрещающих прием запроса прерывания можно управлять способностью микропроцессора реагировать на запрос прерывания, например для защиты определенных критичных по времени частей программы, некоторые прерывания, например связанные с аварией питания замаскировать нельзя.