- •Курс лекций по дисциплине: «цифровая электроника »

- •Минск бгуир 2010 Введение

- •1. Математический аппарат цифровых систем

- •1.1 Основы булевой алгебры

- •1.1.1 Основные положения и законы булевой алгебры

- •Примеры алгебраического метода доказательства теорем:

- •Табличный метод доказательства теоремы де-Моргана

- •1.1.2 Формы представления функций булевой алгебры

- •Булевы функции от двух переменных. Полнота и базис булевых функций.

- •1.2 Логические функции

- •Формы представления логических функции

- •1.3 Минимизация логических функций

- •1.3.1. Минимизация логических функций с помощью карт Карно

- •2. Элементная база цифровых устройств

- •2.1. Особенности структуры и элементной базы цифровых бис и сбис.

- •2.2. Логические элементы и их характеристики

- •2.3. Элементы ттл, ттлш

- •2.3.1. Элемент ттл с простым инвертором.

- •2.3.2. Элемент ттлш с простым инвертором.

- •2.3.3. Схемы ттл/ттлш логики со сложным инвертором

- •Серия к531

- •Серия к1533(als)

- •2.4. Элементы кмоп логики

- •2.4.1. Инвертор на комплементарных транзисторах

- •2.4.2. Логические элементы на комплементарных транзисторах (кмоп).

- •2.4.3. Буферированные кмоп

- •2.4.4. Схема кмоп логики с тремя состояниями выхода

- •2.4.5. Двунаправленный ключ

- •2.5. БиКмоп логика

- •3. Цифровые функциональные узлы комбинационного типа

- •3.3 Основные типы комбинационных узлов

- •3.3.1 Преобразователи кодов

- •3.3.2 Шифраторы и дешифраторы

- •3.3.3 Мультиплексоры и демультиплексоры

- •3.3.4 Комбинационные сумматоры

- •3.3.5 Мажоритарные элементы

- •4. Интегральнье триггеры

- •4.1 Классификация триггеров

- •4.2 Основные типы триггеров

- •4.2.1. Асинхронные и синхронные триггеры.

- •4.2.2. Способы управления триггерами.

- •4.3 Словари переходов

- •5. Функциональные узлы последовательностного типа

- •5.1 Последовательностные устройства

- •5.2 Проектирование последователъно-стных устройств

- •5.3 Счетчики

- •5.3.1. Классификация счетчиков.

- •5.4 Регистры

- •5.4.1. Регистры с параллельным приёмом и выдачей.

- •5.4.2. Регистры с последовательным приёмом или выдачей информации.

- •5.5 Генераторы кодов

Серия к1533(als)

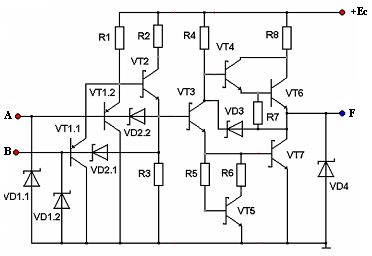

На рисунке 2.9 представлена схема логического элемента серии К1533. Схема имеет следующие преимущества по сравнению со схемой серии К555: полное ограничение диодом Шотки всех насыщающихся транзисторов, что способствует исключению накопления излишнего базового заряда и значительно уменьшает время выключения транзисторов; устранение излишнего накопления заряда, что позволяет получить более стабильное время переключения в диапазоне температур; обеспечение улучшения динамической помехоустойчивости при высоком логическом уровне за счет активного выключения выходного транзистора.

Рис. 2.9. Схема базового логического элемента серии К1533

Схема имеет следующие преимущества по сравнению со схемой серии К555: полное ограничение диодом Шотки всех насыщающихся транзисторов, что способствует исключению накопления излишнего базового заряда и значительно уменьшает время выключения транзисторов; устранение излишнего накопления заряда, что позволяет получить более стабильное время переключения в диапазоне температур; обеспечение улучшения динамической помехоустойчивости при высоком логическом уровне за счет активного выключения выходного транзистора.

Входной порог переключения устанавливается транзисторами при следующем соотношении: Uпор=UбэVT2+UбэVT3+UбэVT7–UбэVT1= 1,3 В. В схеме серии К555 в отличие от приведенной выше отсутствует транзисторVT2. Когда открывается выходная схема Дарлингтона (транзисторыVT4,VT6), позволяющая осуществить формирование сигнала на выходе с сохранением низкого выходного сопротивления при высоком и низком логических уровнях, на выходе устанавливается напряжение высокого уровняU1выхпри выходном сопротивлении, равном 10 Ом.

При небольших токах нагрузки схема Дарлингтона находится в ненасыщенном состоянии. При увеличении тока нагрузки она насыщается и выходное сопротивление возрастает до 58 Ом, определяясь в основном сопротивлением R8 = 50Ом. Это сопротивление обеспечивает защиту каскада от короткого замыкания. Стабильность выходного напряжения высокого уровня U1выхосуществляется благодаря активному выключению транзистораVT7 транзисторомVT5. Выходное напряжение определяется как

U1вых = Ес– (IбVT4R3+UбэVT4+UбэVT6)

Выходное напряжение низкого уровня U0вых устанавливается транзистором VT7, когда он включен. Этот транзистор включается цепью VT3, R4, когда на входе схемы высокий логический уровень, а транзистор VT2 включен.

2.4. Элементы кмоп логики

2.4.1. Инвертор на комплементарных транзисторах

Схема инвертора (рис.2.10) содержит транзисторы VTnиVTp с каналами соответственноn- и р-типа. В структуре на кремниевой подложке последняя соединяется с общей шиной. Дляp-канального транзистора «подложкой» служитn-область кармана, соединяемая с плюсом источника питания.

При UBX= U1= UИПтранзистор VTn открыт, a VTpзакрыт. На выходе получаем UBЫХ= U0≈ 0. Если UBХ= U0= 0, то, наоборот, транзистор VTnзакрыт, a VTPоткрыт и UBЫХ= U1= UИП.В обоих состояниях ток, потребляемый от источника питания, практически равен нулю. Предполагается, что выход инвертора соединен со входами аналогичных инверторов-нагрузок. Таким образом, мощность, потребляемая в статическом режиме, практически равна нулю, что является важнейшим преимуществом по сравнению с любыми другими микросхемами.

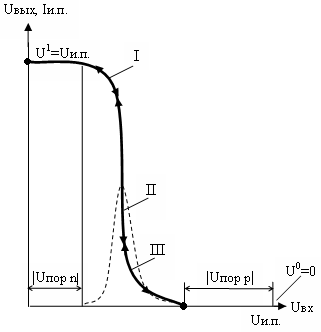

На рис. 2.11, а показана передаточная характеристика инвертора (сплошная линия). С помощью рис. 2.11, б можно пояснить графический метод ее построения. На нем сплошными линиями изображены стоковые характеристики n-канального транзистораICn(UВЫХ), а штриховыми – стоковые характеристикиp-канального транзистораICp(UВЫХ) при одних и тех же входных напряжениях UBX3> UBX2> UВХ1> UПОР. Пороговые напряжения для простоты предполагаются одинаковыми для обоих транзисторов. При малых UВХточки пересечения ВАХ лежат в областиI, гдеn-канальный транзистор работает в режиме насыщения, аp-канальный не насыщен. Это соответствует областиIпередаточной характеристики на рис. 2.11, а. Когда входное напряжение достигает UВХ2= U’BX, оба транзистора находятся в режиме насыщения, а выходное напряжение изменяется скачкообразно в пределах областиIIна рис. 2.11, а, б. При UВХ> U’BXp-канальный транзистор работает в режиме насыщения, аn-канальный не насыщен, чему соответствует областьIIIна передаточной характеристике.

Рис. 2.10. Схема инвертораРис. 2.11 а. Передаточная характеристика

КМОП-инвертора

Рис. 2.11 б. Передаточная характеристика КМОП-инвертора

Оптимальная форма передаточной характеристики достигается при одинаковых параметрах транзисторов (bn=bp,UПОРn= |UПОРp|). ТогдаU’ВХ=UИП/2, помехоустойчивость максимальна и близка кUИП/2, а коэффициент помехоустойчивостиUП/UЛ= 0,4 ... 0,5. Столь высокие значения не достигаются в инверторах других типов, в том числе на биполярных транзисторах. Это обусловлено минимальным значениемU0= 0, максимальным значением U1=UИПи оптимальной (симметричной) передаточной характеристикой. К тому же она практически не зависит от температуры. Высокая помехоустойчивость в широком интервале температур – также важное преимущество.

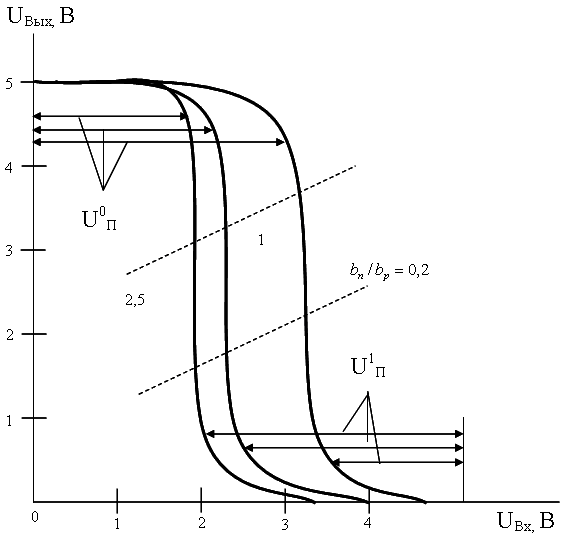

На рис. 2.12 показано влияние параметра bn/bp, зависящего от геометрических размеров транзисторов, на передаточную характеристику (UИП= 5 В, |UПОР| =UПОРn= 0,7 В). Между параллельными штриховыми линиями находится областьII, проходящая практически вертикально, где оба транзистора работают в режиме насыщения. С ростомbn/bpхарактеристика смещается влево, помехоустойчивостьU0Пуменьшается, аU1Пувеличивается.

Из-за разной подвижности электронов и дырок (µn/µp= 2,5) для выполнения условияbn/bp= 1 требуется разная ширина каналов транзисторов (Wp/Wn= µn/µp), длина каналов обычно выбирается одинаковой. При этом площадь инвертора не получается минимальной. При одинаковых геометрических размерах транзисторов, обеспечивающих минимальную площадь, получаемbn/bp= µn/µp, что ухудшает форму передаточной характеристики (см. рис. 2.12) и снижает помехоустойчивостьU0П(на 20%).

На рис. 2.13 показано изменение передаточной характеристики в зависимости от напряжения питания. Напряжение U’ВХ, соответствующее вертикальному участку (между штриховыми линиями), снижается пропорционально UИП, в то же время протяженность этого участка (ΔUВЫХ) не изменяется вплоть доUИ.П.МИН=UПОРn+ |UПОРp|, когда характеристика близка к прямоугольной. ПомехоустойчивостьU0П,U1Пизменяется пропорционально UИП; при UИП=UИ.П.МИНпомехоустойчивостьU0П=U1П=UПОР(если UПОРn= |UПОРp| =UПОР) независимо от значенияbn/bp. Коэффициенты помехоустойчивостиUП/UЛпостоянны вплоть доUИ.П.МИН. Таким образом инвертор может работать в широком интервале напряжений питания (практически UИП=2...15 В) без ухудшения относительной помехоустойчивости, что является существенным достоинством, которым не обладают другие микросхемы. Работоспособность сохраняется и при UИП<UИ.П.МИН(пунктирная линия), пока напряжение питания превышает большую из величин UПОРnили |UПОРp|, но помехоустойчивость мала и работать при таких напряжениях не рекомендуется.

Быстродействие инвертора оценивается средней задержкой tзд.ср.= 0,5(t1,0 +t0,1), где времена переходовt1,0,t0,1при подаче прямоугольного импульса на вход определяются процессами разряда нагрузочной емкости черезn-канальный и заряда ее через р-канальный транзистор.

.

.

где токи насыщения определяются выражениями

,

,

а временные коэффициенты – формой ВАХ транзисторов.

Если пороговые напряжения составляют

(0,l…0,5)UИП, тоkT= 1,2...1,6; для грубых оценок можно полагать

t1,0T= t0,1T= 1,4. Нагрузочная емкость складывается

из суммарной входной емкости нагрузокn(СЗИn+ СЗИp), емкости

соединительных проводников и выходной емкости инвертора, равной

сумме емкостей р-nпереходов

сток – подложка обоих транзисторов:

и выходной емкости инвертора, равной

сумме емкостей р-nпереходов

сток – подложка обоих транзисторов:

В случае bn=bp,

оптимальном с точки зрения помехоустойчивости,

получаем t0,1T= t1,0T(при UПОРn= |UПОРp|). Однако значение tзд.срне является минимальным, так как большая

ширина канала транзистора VTp,

обусловливает большие емкости СЗИр,ССПри общую емкость СН.

Минимальное значение tзд.ср(т. е.

максимальное быстродействие) достигается

при ,

тогда

,

тогда .

.

Рис. 2.12. Влияние параметра bn/bp на передаточную

характеристику.

Рис. 2.13 Передаточная характеристика при различных напряжениях питания

В результате быстродействие инвертора на комплементарных транзисторах выше, чем на n-канальных, несмотря на большую нагрузочную емкость и большее вследствие этого значение t1,0. Оценка tзд.срдает СН= 0,34 пФ (вместо 0,17 пФ) и tзд.ср= 1,5 нс (вместо 13 нс) при UИП= 5 В. Быстродействие увеличивается с ростом напряжения питания, так как токи насыщения в формулах (2.13) пропорциональны (UИП- UПОР)2. В пределах UИП= 2...15 В величина tзд.сризменяется от 6 до 0,4 нс. Типичное значение tзд.ср= 1 нс.

В импульсном режиме основная часть потребляемой мощности расходуется на перезаряд нагрузочной емкости. За период Т поступающих на вход прямоугольных импульсов емкость перезаряжается дважды, на что необходима энергия CHU2ИП, поэтому мощность

где f– частота следования импульсов. На низких частотах (порядка 1 кГц) мощность составляет единицы нановатт. На максимальной частоте 1/10 tзд.ср(десятки мегагерц) мощность составляет десятые доли или единицы милливатт, что все же меньше, чем для инверторов наn-канальных транзисторах. Реальная потребляемая мощность на 10...20% выше рассчитанной, из-за кратковременного протекания «сквозного тока» через оба транзистора при переключении.