- •Курс лекций по дисциплине: «цифровая электроника »

- •Минск бгуир 2010 Введение

- •1. Математический аппарат цифровых систем

- •1.1 Основы булевой алгебры

- •1.1.1 Основные положения и законы булевой алгебры

- •Примеры алгебраического метода доказательства теорем:

- •Табличный метод доказательства теоремы де-Моргана

- •1.1.2 Формы представления функций булевой алгебры

- •Булевы функции от двух переменных. Полнота и базис булевых функций.

- •1.2 Логические функции

- •Формы представления логических функции

- •1.3 Минимизация логических функций

- •1.3.1. Минимизация логических функций с помощью карт Карно

- •2. Элементная база цифровых устройств

- •2.1. Особенности структуры и элементной базы цифровых бис и сбис.

- •2.2. Логические элементы и их характеристики

- •2.3. Элементы ттл, ттлш

- •2.3.1. Элемент ттл с простым инвертором.

- •2.3.2. Элемент ттлш с простым инвертором.

- •2.3.3. Схемы ттл/ттлш логики со сложным инвертором

- •Серия к531

- •Серия к1533(als)

- •2.4. Элементы кмоп логики

- •2.4.1. Инвертор на комплементарных транзисторах

- •2.4.2. Логические элементы на комплементарных транзисторах (кмоп).

- •2.4.3. Буферированные кмоп

- •2.4.4. Схема кмоп логики с тремя состояниями выхода

- •2.4.5. Двунаправленный ключ

- •2.5. БиКмоп логика

- •3. Цифровые функциональные узлы комбинационного типа

- •3.3 Основные типы комбинационных узлов

- •3.3.1 Преобразователи кодов

- •3.3.2 Шифраторы и дешифраторы

- •3.3.3 Мультиплексоры и демультиплексоры

- •3.3.4 Комбинационные сумматоры

- •3.3.5 Мажоритарные элементы

- •4. Интегральнье триггеры

- •4.1 Классификация триггеров

- •4.2 Основные типы триггеров

- •4.2.1. Асинхронные и синхронные триггеры.

- •4.2.2. Способы управления триггерами.

- •4.3 Словари переходов

- •5. Функциональные узлы последовательностного типа

- •5.1 Последовательностные устройства

- •5.2 Проектирование последователъно-стных устройств

- •5.3 Счетчики

- •5.3.1. Классификация счетчиков.

- •5.4 Регистры

- •5.4.1. Регистры с параллельным приёмом и выдачей.

- •5.4.2. Регистры с последовательным приёмом или выдачей информации.

- •5.5 Генераторы кодов

5.4 Регистры

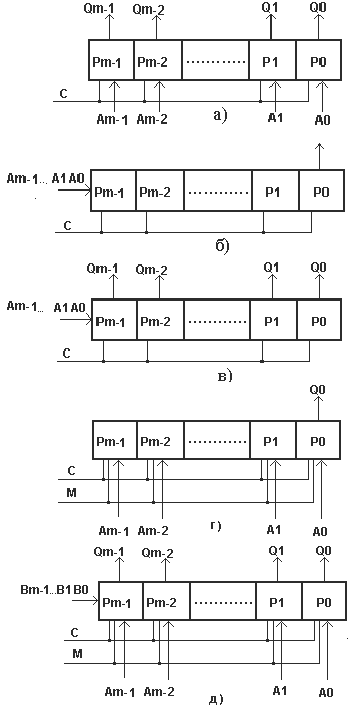

Регистры являются наиболее распространённым типом последовательностных узлов в современных цифровых системах. По способу приёма и выдачи информации регистры делятся на следующие группы: с параллельными приёмом и выдачей (рис. 5.1,а), с последовательным приёмом и последовательной выдачей (рис.5.1,б), с последовательным приёмом и параллельной выдачей (рис.5.1,в), с параллельным приёмом и последовательной выдачей (рис.5.1,г), комбинированные с различными способами приёма и выдачи (рис.5.1,д)

Рис. 5.1. Основные типы регистров.

5.4.1. Регистры с параллельным приёмом и выдачей.

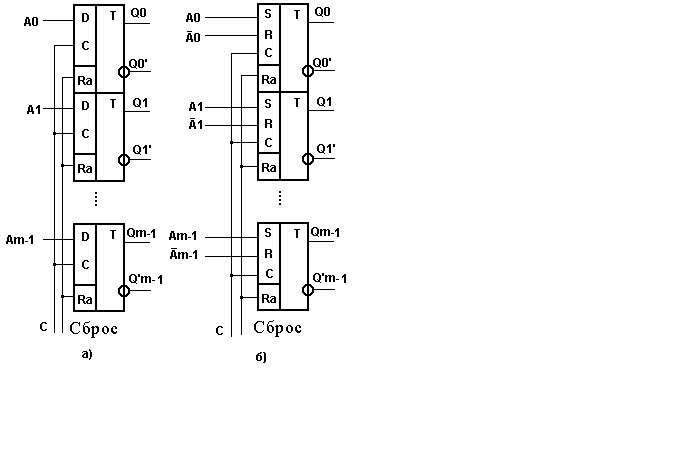

Эти регистры (рис.5.1,а) служат для хранения информации и называются регистрами памяти. Изменение хранящейся информации (ввод новой информации) происходит после соответствующего изменения сигналов на входах А при поступлении определённого уровня (С = 0 или С = 1) или фронта синхросигналов. В качестве разрядов регистра памяти используются синхронизируемые уровнем или фронтом триггеры: D-триггеры (рис. 5.2,а), если информация поступает в виде однофазных сигналов, или RS-триггеры (рис.5.2,б), если информация поступает в виде парафазных сигналов. Предварительная очистка регистра, т. е. установка всех выходов в состояния Q=1, производится с помощью асинхронных входов сброса триггеров Ra.

Рис. 5.2. Регистры хранения на D-триггерах (а)

и RS-триггерах (б)

5.4.2. Регистры с последовательным приёмом или выдачей информации.

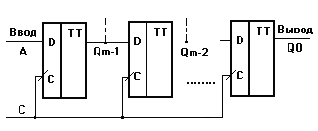

Такие регистры называются сдвиговыми регистрами. В регистре с последовательными приёмом и выдачей (Рис. 5.1,б) первый разряд вводимого числа А0 подаётся на вход одного, крайнего слева, разряда регистра Pm-1 и вводится в него при поступлении первого синхроимпульса Qm-1=А0. При поступлении следующего синхроимпульса значение А0, поступающее с выхода разряда Pm-1, вводится в разряд Pm-2, т. е. устанавливается Qm-2 =А0, а в разряд Pm-1 поступает следующий разряд числа А1: устанавливается Qm-1=А1 и т. д. Таким образом производится последовательный сдвиг поступающей на вход информации на один разряд вправо в каждом такте синхросигналов. После поступления m синхроимпульсов весь регистр оказывается заполненным разрядами числа А и первый разряд числа (А0) появляется на выходе Q0 регистра. В течение последующих m синхроимпульсов производится последовательный поразрядный вывод из регистра записанного числа, после чего регистр оказывается полностью очищенным.

Сдвиговые регистры обычно реализуются на D- триггерах (рис. 5.3) или RS-триггерах (рис. 5.4), где для ввода информации в первый разряд включается инвертор: S0=A, R0=A’.

Параллельный вывод информации из сдвигового регистра (рис. 5.1, в) осуществляется при подключении выходов всех разрядов регистра к отдельным выводам.

Рис. 5.3. Регистр сдвига на D-триггерах

Рис. 5.4. Регистр сдвига на RS-триггерах

При проектировании сдвиговых регистров обязательным является применение триггеров, синхронизируемых фронтом. Ведь во время действия синхросигнала изменяются состояния выходов триггеров, которые подключены ко входам последующих триггеров. Таким образом изменяется состояние входов последующих триггеров, и если синхроимпульс ещё не кончился, то триггеры, синхронизируемые уровнем, переключаются в новое состояние. В результате за время действия одного синхроимпульса (один такт) информация в регистре продвигается более чем на один разряд, т. е. нормальное функционирование регистра – сдвиг на один разряд за один такт - нарушается. Использование триггеров, синхронизируемых положительным или отрицательным фронтом, обеспечивает нормальную работу регистра.

Сдвиговые регистры, показанные на рис. 5.1,г,д, могут работать в двух режимах: параллельного ввода информации и сдвига (последовательного ввода). На рис. 5.5 схема комбинированного регистра на синхронизируемых фронтом D-триггерах. Здесь при X0 = 0 будет производиться ввод, а при X0=1 – сдвиг вправо, т. е. приём информации с выхода предыдущего разряда и передача в следующий. Следовательно, управляющий сигнал X0 определяет режим работы регистра. Можно спроектировать аналогичные регистры на триггерах другого типа.

Рис.5.5. Комбинированный регистр.

Сдвиговые регистры могут быть реверсивными, т. е. выполняющими сдвиг в любом направлении: слева направо или наоборот (рис. 5.5). Направление сдвига определяется значением управляющего сигнала X0. Реверсивный регистр можно получить, если в схеме комбинированного регистра (рис.5.5) вместо внешнего сигнала А подключить выход последующего разряда Q’, как указано в скобках. Сдвиг вправо выполняется при значении сигнала X0 = 1, сдвиг влево – при X0 = 0.

Как видно из выше написанного, регистры могут выполнять хранение и преобразование информации. Сдвиг числа влево или вправо на один разряд соответствует его умножению или делению на два. Поэтому регистры сдвига используются для построения умножителей или делителей. Регистры выполняют также различные преобразования информации: последовательное накопление с последующей одновременной выдачей или одновременный приём с последующей последовательной (развёрнутой во времени) выдачей. Регистры с последовательным вводом и выводом осуществляют задержку передачи информации на m тактов машинного времени. Таким образом, регистры являются многофункциональными узлами цифровых схем.