- •Курс лекций по дисциплине: «цифровая электроника »

- •Минск бгуир 2010 Введение

- •1. Математический аппарат цифровых систем

- •1.1 Основы булевой алгебры

- •1.1.1 Основные положения и законы булевой алгебры

- •Примеры алгебраического метода доказательства теорем:

- •Табличный метод доказательства теоремы де-Моргана

- •1.1.2 Формы представления функций булевой алгебры

- •Булевы функции от двух переменных. Полнота и базис булевых функций.

- •1.2 Логические функции

- •Формы представления логических функции

- •1.3 Минимизация логических функций

- •1.3.1. Минимизация логических функций с помощью карт Карно

- •2. Элементная база цифровых устройств

- •2.1. Особенности структуры и элементной базы цифровых бис и сбис.

- •2.2. Логические элементы и их характеристики

- •2.3. Элементы ттл, ттлш

- •2.3.1. Элемент ттл с простым инвертором.

- •2.3.2. Элемент ттлш с простым инвертором.

- •2.3.3. Схемы ттл/ттлш логики со сложным инвертором

- •Серия к531

- •Серия к1533(als)

- •2.4. Элементы кмоп логики

- •2.4.1. Инвертор на комплементарных транзисторах

- •2.4.2. Логические элементы на комплементарных транзисторах (кмоп).

- •2.4.3. Буферированные кмоп

- •2.4.4. Схема кмоп логики с тремя состояниями выхода

- •2.4.5. Двунаправленный ключ

- •2.5. БиКмоп логика

- •3. Цифровые функциональные узлы комбинационного типа

- •3.3 Основные типы комбинационных узлов

- •3.3.1 Преобразователи кодов

- •3.3.2 Шифраторы и дешифраторы

- •3.3.3 Мультиплексоры и демультиплексоры

- •3.3.4 Комбинационные сумматоры

- •3.3.5 Мажоритарные элементы

- •4. Интегральнье триггеры

- •4.1 Классификация триггеров

- •4.2 Основные типы триггеров

- •4.2.1. Асинхронные и синхронные триггеры.

- •4.2.2. Способы управления триггерами.

- •4.3 Словари переходов

- •5. Функциональные узлы последовательностного типа

- •5.1 Последовательностные устройства

- •5.2 Проектирование последователъно-стных устройств

- •5.3 Счетчики

- •5.3.1. Классификация счетчиков.

- •5.4 Регистры

- •5.4.1. Регистры с параллельным приёмом и выдачей.

- •5.4.2. Регистры с последовательным приёмом или выдачей информации.

- •5.5 Генераторы кодов

2. Элементная база цифровых устройств

2.1. Особенности структуры и элементной базы цифровых бис и сбис.

Базовые логические элементы (ЛЭ) предназначены для: логического преобразования информации, представленной в двоичном коде; формирования потенциальных (токовых) уровней сигналов с электрическими характеристиками, соответствующими кодируемой информации на выходе элемента. Для реализации функциональных блоков цифровых БИС обычно используют маломощные базовые ЛЭ, имеющие невысокую нагрузочную способность, содержащие небольшое количество компонентов (транзисторов, диодов, резисторов) и занимающих на кристалле возможно меньшую площадь.

Входные элементы согласования (ЭС) БИС (входные трансляторы) предназначены для:

а) защиты внутренних цепей БИС от внешних электрических нагрузок;

б) формирования внутренних для микросхем логических уровней;

в) хранения информации в процессе ее обработки в БИС;

г) согласования уровней внешних сигналов, подаваемых на входы БИС, с внутренними;

д) усиления входных сигналов;

е) повышения чувствительности, быстродействия и помехоустойчивости БИС.

Выходные ЭС БИС предназначены для:

а) формирования внешних логических уровней напряжения (тока); зашиты внутренних цепей БИС от внешних электрических перегрузок и помех;

б) усиления внутренних сигналов БИС;

в) формирования необходимых длительностей фронтов выходных сигналов.

г) обеспечения возможности работы нескольких устройств на одну линию связи.

2.2. Логические элементы и их характеристики

Основные параметры и характеристики логических элементов.

Логическое состояние элементов определяется значениями электрического потенциала на их входах и выходах. Элементы характеризуются следующей системой параметров: потенциалы, соответствующие 0 и 1; U0,U1, порог переключенияUп, число входов (коэффициент объединения по входу) М; входные токиI0вхприUвх=U0 иI1вхприUвх=U1 коэффициент разветвления по выходу N (нагрузочная способность); устойчивость к помехам положительной и отрицательной полярностиUп+,Uп- ; мощность Рэ или токIп , потребляемые от источника питания; задержки переключенияt013 из состояния 0 на выходе в состояние 1 иt103из состояния 1 в состояние 0. Параметры определяются по статическим и переходным характеристикам элементов.

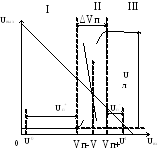

Основной статической характеристикой логических элементов является передаточная характеристика Uвых=f(Uвх) — зависимость потенциала на выходе от потенциала на одном из входов при постоянных значениях потенциала (U0 илиU1) на остальных входах. По типу передаточной характеристики элементы делятся на инвертирующие, на выходе которых образуется инверсия входных сигналов (элементы НЕ, И—НЕ, ИЛИ—НЕ и др.), и неинвертирующие, сигналы на выходе которых не инвертируются элементы И, ИЛИ и др.).

а) б)

Рис. 2.1. Передаточные характеристики инвертирующего (а) и неинвертирующего

(б) логических элементов

Типичная передаточная характеристика инвертирующего элемента показана на рис. 2.1,а, неинвертирующего — на рисунке 2.1,б.Так как в цифровом устройстве должно быть обеспечено четкое разделение (квантование) уровней логических 0 и 1, то передаточная характеристика имеет три явно выраженных участка:I— соответствующий состояниюUвых=U0, II— состояниюUвых=U1,III— промежуточному состоянию. Значения потенциалаUвх, соответствующие границам участков, называются порогами переключенияV0п иV1побласть между порогами — зоной неопределенности.

Максимально допустимая величина потенциальной помехи, не вызывающая сбоя в цифровой схеме, называется помехоустойчивостью и определяется выражениями (рис. 2.1)

U+п =Vп0–U0;U-п =U1–Vп1

U+п–U-п=Uл– ΔVп ,

где Uл=U1 –U0— логический перепад: ΔVп=Vп0 -Vп1— ширина зоны неопределенности.

Таким образом, для повышения помехоустойчивости надо увеличивать Uл и уменьшать ΔVп . Поэтому в цифровых схемах обеспечивают ΔVп<Uли приближенно можно считатьVп0 ≈Vп1 ≈Vп, гдеVп— средний порог переключения.

Максимальная величина логического перепада ограничивается напряжением питания Uл <=Uип , вследствие чего получаем (U+п+U-п)<=Uип. Таким образом, сумма помехоустойчивостейU+п,U-пне превышает напряжения питания.

Чтобы одновременно получить достаточно высокие значения U+п,U-п, следует использовать такие схемы, в которых средний порог переключенияVпрасполагается приблизительно посередине междуU0 иU1. В этом случае значенияU+пиU-правны и составляют

U+п≈U-п≈Uп=0,5(Uл- ΔVп)≈ 0,5Uл<= 0,5Uип

Передаточные характеристики реальных схем имеют определенный разброс, обусловленный различием внешних условий, разбросом параметров компонентов и другими факторами. При этом значения уровней U0,U1 и пороговVп0,Vп1заключены в диапазонах

U0min<=U0<=U0max, V0п min<=V0п<=V0п max ,

U1min<=U1<=U1max, V1п min<=V1п<=V1п max .

Значения U+пиU-попределяются для наихудшего сочетания факторов

U+п=V0п max-U0min,U-п =U1min-V1п max.

Передаточная характеристика зависит от потенциалов шин питания (Uип) и земли (Uз=0). Действие помехVш, возникающих на этих шинах, можно представить как изменение потенциаловU`ип=Uип±Vш,U`з=±Vши определить получающуюся при этом передаточную характеристику. Помехоустойчивость находится с помощью этой передаточной характеристики как максимальная величинаVш, при которой сохраняются значенияU+п,U-п>0.

Если на входы схемы или шины питания и земли поступают импульсные помехи амплитудой Vии длительностьюtи, то при достаточно больших значенияхtиих действие аналогично действию потенциальной помехи такой же величины. Импульсные помехи малой длительности, сравнимой с временем переключения схемы (tи<=t013,t103), не успевают произвести ложное переключение схемы даже при значительной их амплитудеVи. Таким образом, при уменьшении длительности помехиtидля создания сбоя требуется увеличение ее амплитуды, т. е. импульсная помехоустойчивость для большинства логических схем повышается при уменьшении длительности помехи.

Входная характеристика ТТЛ элементов Iвх=f(Uвх), представленная на рис. 2.2, служит для определения входных токов:I0вх=>0, вытекающего из схемы приUвх=U0,I1вх<=0 и втекающего в схему приUвх=U1.

Iвх

Uвх

Рисунок 2.2. Входная характеристика ТТЛ-схемы.

Выходные характеристики логических

элементов U0вых=f(I0н)

иU1вых=f(I1н)

показаны на рис 2.3.

Рис 2.3. Выходные характеристики логического элемента

Динамические параметры определяются с помощью переходных характеристик.

Одним из важнейших динамических параметров является средняя задержка

которая определяет среднее значение

время выполнения логических операций.

Параметр

обычно рассчитывают по измеренным

значениям

обычно рассчитывают по измеренным

значениям и

и .

.