- •Курс лекций по дисциплине: «цифровая электроника »

- •Минск бгуир 2010 Введение

- •1. Математический аппарат цифровых систем

- •1.1 Основы булевой алгебры

- •1.1.1 Основные положения и законы булевой алгебры

- •Примеры алгебраического метода доказательства теорем:

- •Табличный метод доказательства теоремы де-Моргана

- •1.1.2 Формы представления функций булевой алгебры

- •Булевы функции от двух переменных. Полнота и базис булевых функций.

- •1.2 Логические функции

- •Формы представления логических функции

- •1.3 Минимизация логических функций

- •1.3.1. Минимизация логических функций с помощью карт Карно

- •2. Элементная база цифровых устройств

- •2.1. Особенности структуры и элементной базы цифровых бис и сбис.

- •2.2. Логические элементы и их характеристики

- •2.3. Элементы ттл, ттлш

- •2.3.1. Элемент ттл с простым инвертором.

- •2.3.2. Элемент ттлш с простым инвертором.

- •2.3.3. Схемы ттл/ттлш логики со сложным инвертором

- •Серия к531

- •Серия к1533(als)

- •2.4. Элементы кмоп логики

- •2.4.1. Инвертор на комплементарных транзисторах

- •2.4.2. Логические элементы на комплементарных транзисторах (кмоп).

- •2.4.3. Буферированные кмоп

- •2.4.4. Схема кмоп логики с тремя состояниями выхода

- •2.4.5. Двунаправленный ключ

- •2.5. БиКмоп логика

- •3. Цифровые функциональные узлы комбинационного типа

- •3.3 Основные типы комбинационных узлов

- •3.3.1 Преобразователи кодов

- •3.3.2 Шифраторы и дешифраторы

- •3.3.3 Мультиплексоры и демультиплексоры

- •3.3.4 Комбинационные сумматоры

- •3.3.5 Мажоритарные элементы

- •4. Интегральнье триггеры

- •4.1 Классификация триггеров

- •4.2 Основные типы триггеров

- •4.2.1. Асинхронные и синхронные триггеры.

- •4.2.2. Способы управления триггерами.

- •4.3 Словари переходов

- •5. Функциональные узлы последовательностного типа

- •5.1 Последовательностные устройства

- •5.2 Проектирование последователъно-стных устройств

- •5.3 Счетчики

- •5.3.1. Классификация счетчиков.

- •5.4 Регистры

- •5.4.1. Регистры с параллельным приёмом и выдачей.

- •5.4.2. Регистры с последовательным приёмом или выдачей информации.

- •5.5 Генераторы кодов

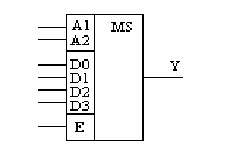

3.3.3 Мультиплексоры и демультиплексоры

Мультиплексором

называется функциональный узел,

обеспечивающий передачу информации,

поступающей по нескольким входным

линиям связи, на одну выходную линию

(рис. 3.7). При наличии n адресных входов

можно реализовать М=2nкомбинаций

адресных сигналов, каждая из которых

обеспечивает выбор одной из М входных

линий. Вход Е - разрешающий: при Е=1

мультиплексор работает как обычно, при

Е=0 выход узла находится в неактивном

состоянии, мультиплексор заперт. Входы

D0 - D3 информационные входы, А1 и А2 -

адресные.

Рис.3.7. Условное обозначение мультиплексора

В общем виде выходная функция мультиплексора "из М в 1" записывается в виде:

,

,

Выбор той или иной входной линии осуществляется в соответствии с поступающим адресным кодом.

Один из способов увеличения числа коммутируемых каналов в схемах построенных на мультиплексорах со стробированием показан на рис 3.8. Приведенная схема представляет собой мультиплексор из 16 в 1.

Рис 3.8. Мультиплексор со стробированием

Второй способ увеличения числа коммутируемых каналов показан на рис 3.9. Вместо элемента И-НЕ на выходе используется дополнительный мультиплексор, производящий выбор одного из мультиплексоров с помощью адресных сигналов А4, A5, A6. Такое соединение называют мультиплексорное дерево. Мультиплексоры MS1 и MS2 являются мультиплексорами первого уровня, а MS3 второго. На первом и втором уровнях можно использовать мультиплексоры с разным числом входов. Если на первом уровне используются мультиплексоры с числом адресных входов n1, на втором – с числом n2 то общее количество входов мультиплексорного дерева составит n = 2n1+ 2n2, а число мультиплексоров 2n2+ 1.

Рис 3.9. Мультиплексорное дерево

Применение мультиплексоров не ограничивается операцией мультиплексирования. Мультиплексоры применяют для сдвига информации, для реализации логических функций заданных какой-либо таблицей функционирования, для передачи слова прямым или обратным кодом в зависимости от управляющего уровня. Мультиплексор можно использовать в качестве универсального логического элемента для реализации любой функции от числа переменных, равного числу адресных входов. Мультиплексор показанный на рисунке реализует функцию согласно таблице. Если бы эта функция реализовывалась на базисе И-НЕ то понадобилось бы четыре элемента 3И-НЕ и три инвертора.

При коммутации многоразрядных слов в каждом разряде используется свой мультиплексор.

Для восстановления мультиплексированной информации используют демультиплексоры, которые в соответствии с принятым адресом направляют информацию в одну из выходных линий. При этом на остальных выходных линиях поддерживается логический 0.

В роли демультиплексора успешно выступает декодер, если к его разрешающему входу Е подключить мультиплексированную магистраль данных, а на адресные входы подавать друг за другом коды адресов приемника.

3.3.4 Комбинационные сумматоры

Основной операцией при выполнении арифметических действий в современных цифровых системах является сложение. Поэтому основным блоком операционных устройств обычно является сумматор (рис. 3.10), который используется также для вычитания, умножения, деления, преобразования чисел в дополнительный код, код «с избытком 3» и в ряде других операций.

Рис.3.10. Сумматор

Сумматор имеет nвходов разрядов слагаемого А,nвходов разрядов слагаемогоBи вход переносаcr. Выходами сумматора являютсяnвыходов разрядов суммыSи выход переноса (переполнения)cr.

Суммирование многоразрядных чисел производится путем их поразрядного сложения с переносом между разрядами. Поэтому многоразрядные сумматоры состоят из комбинационных одноразрядных сумматоров. Такой сумматор выполняет сложение одноразрядных двоичных чисел Ai, Bi и переноса из младшего разряда Ci, образуя на выходах значение суммы Si и перенос в старший разряд Ci+1.

Многоразрядные сумматоры в зависимости от способа ввода кодов слагаемых делятся на последовательного и параллельного действия.

В сумматоры первого типа коды чисел вводятся в последовательной форме, т.е. разряд за разрядом (младшим разрядом вперед), в сумматоры второго типа каждое слагаемое подается в параллельной форме, т.е. одновременно всеми разрядами.

Сумматор последовательного действия (рис 3.11) состоит из одноразрядного сумматора, выход Рi+1 которого соединен с входом Pi через D –триггер. С первым тактовым импульсом на входы сумматора поступают с выходов регистров (1,2) цифры первого разряда слагаемых aiи bi, а из D –триггера на вход Pi подается логический 0. Суммируя поданные на входы цифры, сумматор формирует на выходе первый разряд суммы S1 и перенос Рi+1 принимаемый в D –триггер. Со следующим тактовым импульсом на входы подаются цифры второго разряда и перенос Рi+1 и т.д.

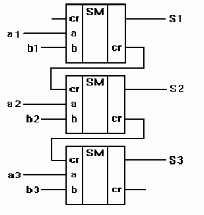

Рис 3.11. Сумматор с последовательным переносом

Достоинство такого сумматора заключается в небольших аппаратных затратах. Однако он обладает малым быстродействием.

Сумматоры параллельного действия строятся с использованием нескольких одноразрядных сумматоров. В зависимости от способа организации переноса между ними сумматоры параллельного действия бывают с последовательным, параллельным и комбинированным переносом.

В сумматорах с последовательным переносом выход переноса cr каждого разряда подключен ко входу переноса cr самого младшего разряда. Таким образом, задача построения сумматора с последовательным переносом сводится к построению схемы одноразрядного сумматора. В сумматоре с последовательным переносом тракты переносов всех одноразрядных сумматоров соединены последовательно. Поэтому даже при минимальной задержке тракта переноса в 1tззадержка n – разрядного сумматора будет не менее ntз.

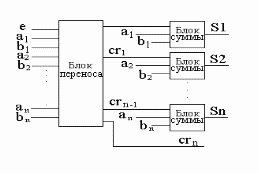

Для уменьшения задержки используется принцип параллельного переноса, когда входной перенос каждого разряда вырабатывается независимо от переноса соседнего младшего разряда. Для всех разрядов сигналы переноса формируются параллельно. Общая структурная схема многоразрядного сумматора с параллельным переносом представлена на рис 3.12

Рис 3.12. Сумматор с параллельным переносом

В этой схеме блоки суммы одинаковы для всех разрядов и реализуют функцию суммы. Блок переноса вырабатывает сигнал переноса одновременно для всех блоков суммы. Однако аппаратурные затраты такого сумматора превышают затраты сумматора с последовательным переносом и быстро растут с ростом разрядности. Поэтому разрядность реально используемых сумматоров с параллельным переносом редко превышает восьми.

Для ускорения переноса в сумматорах с большой разрядностью используется принцип группового переноса. Сумматор разбивается на группы, представляющие собой сумматоры с разрядностью от 2 до 8. Каждый такой мини сумматор имеет свой вход переноса. При разбиении сумматора на группы соблюдают условие n=ml, где n-общее число разрядов сумматора; l-число выделенных групп; m-число одноразрядных сумматоров.

Суть группового переноса заключается в том, что в дополнение к тракту переноса внутри группы строят тракт переноса между группами, который вырабатывает сигналы групповых переносов. При этом как в каждой группе, так и между группами возможны различные виды переноса. Среди таких структур наибольшее распространение получили схемы с цепным и параллельно-параллельным переносом.

Сумматоры с цепным переносом реализуют внутри выделенных групп параллельный перенос, в то время как между группами используется последовательный перенос. Такой подход позволяет повысить быстродействие по сравнению с последовательными сумматорами большой разрядности.

Сумматоры с параллельно-параллельным переносом реализуют как внутри группы, так и между ними принцип параллельного переноса. Такие сумматоры большой разрядности обладают наибольшим быстродействием.

Полусумматор - это комбинационное устройство выполняющее сложение разрядов двоичных чисел. В отличии от сумматора полусумматор воспринимает только два сигнала: сигнал разряда числа А и сигнал разряда числа В. Сигнал переноса полусумматор не воспринимает.