- •Курс лекций по дисциплине: «цифровая электроника »

- •Минск бгуир 2010 Введение

- •1. Математический аппарат цифровых систем

- •1.1 Основы булевой алгебры

- •1.1.1 Основные положения и законы булевой алгебры

- •Примеры алгебраического метода доказательства теорем:

- •Табличный метод доказательства теоремы де-Моргана

- •1.1.2 Формы представления функций булевой алгебры

- •Булевы функции от двух переменных. Полнота и базис булевых функций.

- •1.2 Логические функции

- •Формы представления логических функции

- •1.3 Минимизация логических функций

- •1.3.1. Минимизация логических функций с помощью карт Карно

- •2. Элементная база цифровых устройств

- •2.1. Особенности структуры и элементной базы цифровых бис и сбис.

- •2.2. Логические элементы и их характеристики

- •2.3. Элементы ттл, ттлш

- •2.3.1. Элемент ттл с простым инвертором.

- •2.3.2. Элемент ттлш с простым инвертором.

- •2.3.3. Схемы ттл/ттлш логики со сложным инвертором

- •Серия к531

- •Серия к1533(als)

- •2.4. Элементы кмоп логики

- •2.4.1. Инвертор на комплементарных транзисторах

- •2.4.2. Логические элементы на комплементарных транзисторах (кмоп).

- •2.4.3. Буферированные кмоп

- •2.4.4. Схема кмоп логики с тремя состояниями выхода

- •2.4.5. Двунаправленный ключ

- •2.5. БиКмоп логика

- •3. Цифровые функциональные узлы комбинационного типа

- •3.3 Основные типы комбинационных узлов

- •3.3.1 Преобразователи кодов

- •3.3.2 Шифраторы и дешифраторы

- •3.3.3 Мультиплексоры и демультиплексоры

- •3.3.4 Комбинационные сумматоры

- •3.3.5 Мажоритарные элементы

- •4. Интегральнье триггеры

- •4.1 Классификация триггеров

- •4.2 Основные типы триггеров

- •4.2.1. Асинхронные и синхронные триггеры.

- •4.2.2. Способы управления триггерами.

- •4.3 Словари переходов

- •5. Функциональные узлы последовательностного типа

- •5.1 Последовательностные устройства

- •5.2 Проектирование последователъно-стных устройств

- •5.3 Счетчики

- •5.3.1. Классификация счетчиков.

- •5.4 Регистры

- •5.4.1. Регистры с параллельным приёмом и выдачей.

- •5.4.2. Регистры с последовательным приёмом или выдачей информации.

- •5.5 Генераторы кодов

2.4.2. Логические элементы на комплементарных транзисторах (кмоп).

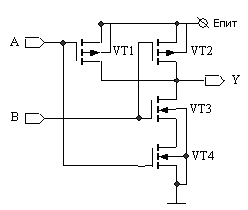

Для реализации функции И-НЕ применяется последовательное включение n-канальных и параллельное включениеp-канальных транзисторов (рис. 2.14, а). При тех же геометрических размерах транзисторов, что и в инверторе, ток, задаваемыйn-канальными транзисторами и открытом состоянии, уменьшается в т раз, а ток, задаваемый р-канальными транзисторами, увеличивается вmраз. Поэтому ЛЭ И-НЕ имеет характеристики и параметры, близкие к инвертору, эффективная удельная крутизна транзисторов которогоbnЭФ=bn/m,bpЭФ=mbp. С ростомmпараметрbnЭФ/bpЭФуменьшается, передаточная характеристика сдвигается вправо и уменьшается помехоустойчивостьU1П(см. рис. 2.12). Приm≥ 5 помехоустойчивостьU1Пстремится к |UПОРp|. Если этого недостаточно, надо увеличивать ширину канала транзисторов VTn(Wn>Wp) для повышенияbn/bp.

С увеличением mвремя t1,0линейно возрастает, a t0,1во столько же раз убывает, поэтому средняя задержка изменяется сравнительно медленно. При одинаковых размерах транзисторов (Wn=Wp) величина tзд.срдляm= 1 иm= 4 отличается только в 1,3 раза. Таким образом, элемент И-НЕ на комплементарных транзисторах характеризуется гораздо более слабой зависимостью быстродействия от m по сравнению с элементом наn-канальных транзисторах. Для больших m (более 4...5)t0,1« t0,1и средняя задержка возрастает пропорциональноm.

Рис. 2.14, а. Элемент И-НЕ

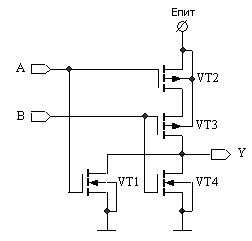

Для реализации функции ИЛИ-НЕ применяется параллельное включение n-канальных и последовательное включение р-канальных транзисторов (рис. 2.14,6). Логический элемент ИЛИ-НЕ имеет характеристики и параметры, близкие к характеристикам и параметрам инвертора с эффективной удельной крутизной транзисторовbnЭФ=mbn,bpЭФ=bp/m. С ростом m передаточная характеристика сдвигается влево и уменьшается помехоустойчивость U0П, стремящаяся в пределе (приm> 4...5) к UПОРn. Время t0,1 линейно возрастает, а время t1,0 убывает. При одинаковых геометрических размерах транзисторов t0,1значительно больше t1,0, даже еслиm= 1. Поэтому средняя задержка увеличивается примерно пропорциональноm, т.е. гораздо сильнее, чем в элементе И-НЕ.

Оптимальным с точки зрения быстродействия

является соотношение

.

Дляm= 2...4 получаемWp/Wn= 2...3, т. е. размеры р-канальных

транзисторов должны быть существенно

больше, чем n-канальных. Это ведет к росту

площади, занимаемой ЛЭ на кристалле, и

повышению нагрузочной емкости (по

сравнению с элементом И-НЕ). Поэтому

даже в оптимальном случае быстродействие

элементов ИЛИ-НЕ (в предположении, что

они нагружены на подобные ЛЭ) примерно

в 2 раза хуже, чем элементов И-НЕ. Таким

образом, в КМОП-микросхемах предпочтительнее

использовать элементы И-НЕ.

.

Дляm= 2...4 получаемWp/Wn= 2...3, т. е. размеры р-канальных

транзисторов должны быть существенно

больше, чем n-канальных. Это ведет к росту

площади, занимаемой ЛЭ на кристалле, и

повышению нагрузочной емкости (по

сравнению с элементом И-НЕ). Поэтому

даже в оптимальном случае быстродействие

элементов ИЛИ-НЕ (в предположении, что

они нагружены на подобные ЛЭ) примерно

в 2 раза хуже, чем элементов И-НЕ. Таким

образом, в КМОП-микросхемах предпочтительнее

использовать элементы И-НЕ.

Рис. 2.14, б. Элемент ИЛИ-НЕ

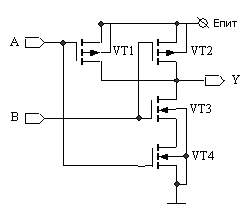

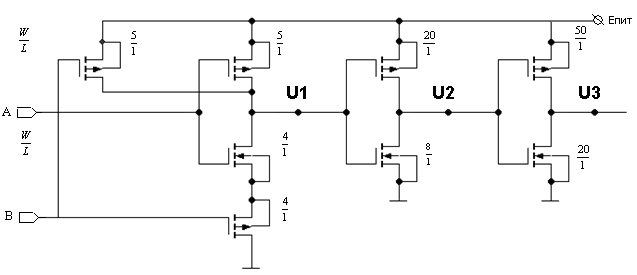

2.4.3. Буферированные кмоп

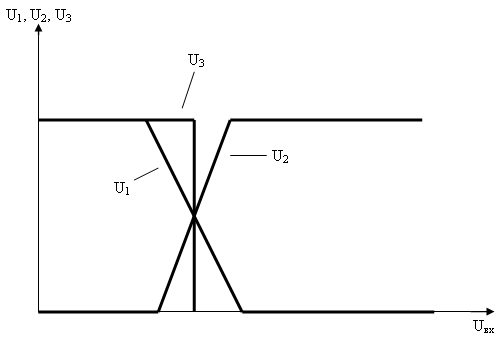

Благодаря уменьшению размеров становится возможным выпускать буферированные КМОП с улучшенными характеристиками. Это реализуется путем добавления двух инверторов без существенного изменения размеров ячейки. Например, на рис. 2.16, а показан результат буферирования ячейки И-НЕ, исходная схема которой дана на рис. 2.15. Времена нарастания и спада выходного сигнала в схеме на рис. 2.15,а зависят от сочетания входных сигналов, что показано тонкими линиями на рис. 2.16,б. В буферированной КМОП-схеме благодаря усилению сигналов парой инверторов (рис.2.16, а) этот недостаток удалось устранить (см. утолщенную линию на рис. 2.16,б). Улучшаются и передаточные характеристики (рис. 2.16, в), что ведет к повышению помехоустойчивости схем.

Рис. 2.15. Ячейка И-НЕ с двумя входами

Рис. 2.16,а. Буферированная ячейка И-НЕ

Рис. 2.16,б. Временная задержка

Рис. 2.16, в. Передаточная характеристика