- •146 Цифровая схемотехника Конспект цифровая схемотехника

- •2. Формирователи прямоугольных импульсов

- •10. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы.

- •1.2 Прохождение импульсов через rc-цепи.

- •1.2.1 Напряжение и ток в rc-цепях под воздействием единичного скачка.

- •1.2.2 Дифференцирующая (укорачивающая) и разделительная rc-цепи.

- •1.2.3 Реальные rc-цепи при импульсном воздействии.

- •1.3 Фиксаторы уровня в дифференцирующих rc-цепях.

- •1.4 Интегрирующие rc-цепи.

- •Погрешности интегрирующей цепи:

- •2. Формирователи прямоугольных импульсов

- •2.1 Диодные ограничители последовательного и параллельного типа.

- •2.2 Линейные модели транзистора в режиме большого сигнала.

- •2.3 Расчет транзисторных ключей.

- •2.4 Транзисторный усилитель ограничитель.

- •2.5 Динамические характеристики транзисторных ключей.

- •3. Мультивибраторы

- •3.2 Транзисторный мультивибратор. Принцип действия, осциллограм-мы работы мультивибратора

- •3.3 Расчет периода колебаний мультивибратора

- •3.4 Регулировка частоты, термостабилизация и улучшение формы выходного напряжения мультивибратора.

- •3.5 Транзисторный одновибратор. Принцип действия, осциллограммы.

- •4. Потенциальные логичекие элементы

- •4.2 Диодная логика. Логика «и»

- •Логика «или»

- •Недостатки диодной логики: схемы критичны к внутреннему сопротивлению источников эдс (), обладают нестабильными уровнями логического «0» и «1».

- •4.3 Диодно-транзисторная логика (дтл)

- •4.4 Транзистор-транзисторная логика (ттл)

- •4.5 Логические элементы на моп и кмоп-структурах.

- •5.1 Мультивибраторы на потенциальных логических элементах.

- •5.2 Одновибраторы на потенциальных логических элементах.

- •5.2 Одновибраторы на потенциальных логических элементах.

- •Расчет длительности импульса одновибратора.

- •6.1 Кодирование временных интервалов.

- •6.2 Кодирование напряжение.

- •6.3 Аналогово-цифровые преобразователи (ацп). Основные характеристики и параметры.

- •6.3.1 Ацп на параллельных компараторах;

- •6.3.2 Ацп поразрядного кодирования.

- •6.4 Цифро-аналоговые преобразователи (цап). Структура, основные характеристики и параметры.

- •6.4.1 Взвешенная схема, управляющая напряжением.

- •6.5 Устройство выборки хранения.

- •7.1 Общая характеристика и принципы построения глин.

- •7.2 Автоколебательные глин на транзисторах.

- •7.3 Ждущие глин на транзисторах.

- •7.4 Глин на оупт.

- •8.2 Автоколебательный блокинг-генератор.

- •8.3 Ждущий блокинг-генератор.

- •8.4 Синхронизация блокинг-генератора.

- •9.1 Оперативные запоминающие устройства (озу) с произвольным доступом.

- •9.2 Статические и динамические зу.

- •9.3 Построение плат памяти.

- •9.4 Программируемые запоминающие устройства (пзу).

- •10. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы.

- •10.2 Программируемые логические матрицы (плм).

- •10.2.1 Схемотехника плм

- •10.2.2 Подготовка задачи к решению с помощью плм

- •10.2.3 Программирование плм

- •10.2.4 Упрощенное изображение схем плм

- •10.2.5 Воспроизведение скобочных форм переключательных функций

- •10.2.6 Наращивание (расширение) плм

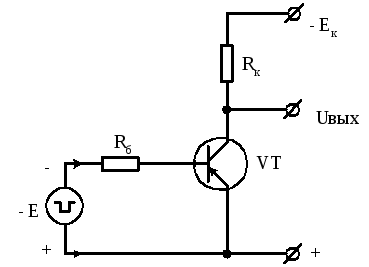

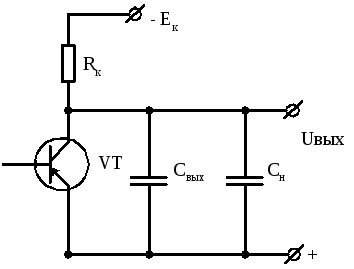

2.4 Транзисторный усилитель ограничитель.

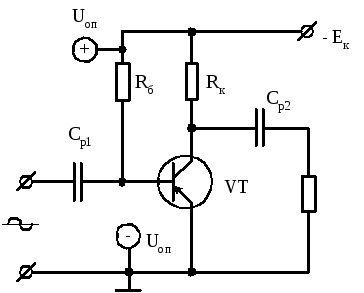

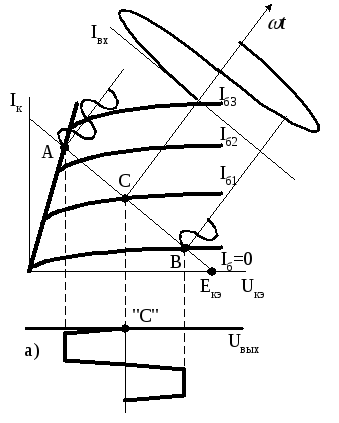

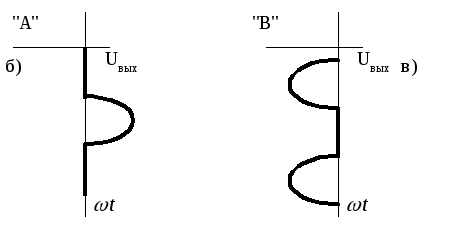

Принципиальная схема усилителя-ограничителя приведена на рис.2.29. Усилитель-ограничитель представляет транзисторный ключ, который из активного режима переключается в режим отсечки и насыщения, ограничивая сигнал снизу и сверху (двухсторонний ограничитель, режим работы по постоянному току в точке С) рис.2.30 а. Для ограничителя сверху рабочая точка выбирается в режиме насыщения («А»), снизу – в режиме отсечки (точка «В») (см. рис.2.30 б,в).

Рис. 2.29 Транзисторный усилитель ограничитель

Рис. 2.30 Ограничение двухсторонние (а), сверху (б), снизу (в)

Преимущества транзисторного усилителя-ограничителя:

Коэффициент передачи

,

что требует относительно малых входных

сигналов (сотни милливольт);

,

что требует относительно малых входных

сигналов (сотни милливольт);Низкое выходное сопротивление, что обеспечивает согласование ограничителя с нагрузкой;

Высокий коэффициент прямоугольности выходного сигнала;

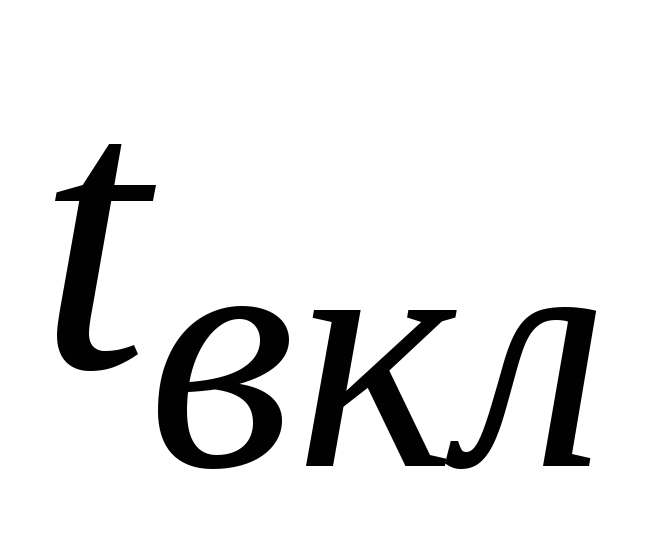

2.5 Динамические характеристики транзисторных ключей.

Для безыскаженной передачи информации транзисторными ключами необходимо, чтобы все гармоники спектра прямоугольных импульсов или импульсной последовательности усиливались с одинаковым коэффициентом усиления и начальные фазовые сдвиги между гармониками не изменялись.

Это обеспечивается равномерной амплитудно-частотной характеристикой (АЧХ) в рабочем диапазоне частот и линейно-возрастающей фазо-частотной характеристикой ФЧХ.

Искажения частотных характеристик

обусловлено реактивными элементами

схемы (снизу оказывает влияние

![]() ,

сверху –

,

сверху –![]() ).

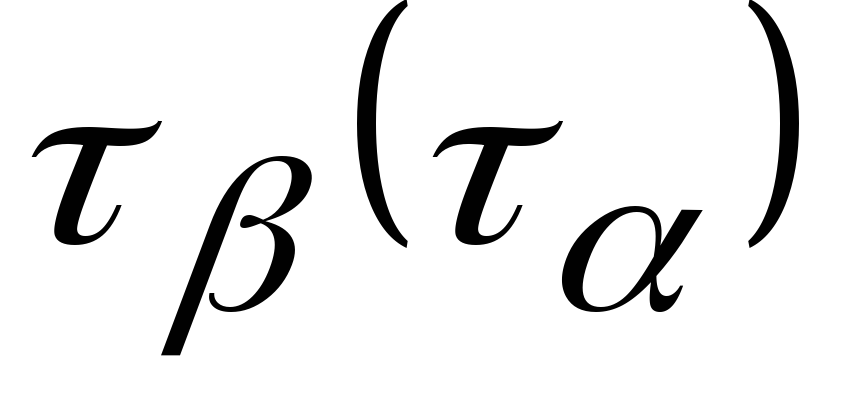

Кроме того в области верхних частот,

сказывается влияние инерционных свойств

самого транзистора. Эти свойства

оцениваются его постоянной времени

).

Кроме того в области верхних частот,

сказывается влияние инерционных свойств

самого транзистора. Эти свойства

оцениваются его постоянной времени![]() .

Постоянная времени определяет граничную

частоту усиления транзистора

.

Постоянная времени определяет граничную

частоту усиления транзистора![]() .

Граничная частота усиления зависит от

схемы включения транзистора:

.

Граничная частота усиления зависит от

схемы включения транзистора:

![]() (в

(в![]() раз).

раз).

Постоянные времени транзистора включенного по схеме с ОЭ и ОБ определяется выражениями:

![]() ;

;![]() .

.

Соотношение между постоянными времени транзистора:

![]() в (

в (![]() раз),

что обуславливает лучшие частотные

свойства схемы с ОБ.

раз),

что обуславливает лучшие частотные

свойства схемы с ОБ.

Если на вход ключа подать идеальные

прямоугольные импульсы, то выходные

импульсы будут искажены даже при

отсутствии

![]() ,

эти искажения будут обусловлены

инерционными свойствами транзистора.

,

эти искажения будут обусловлены

инерционными свойствами транзистора.

Рассмотрим искажения импульсов транзисторным ключом, схема которого приведена на рис.2.31. Источник входных импульсов обеспечивает идеальную прямоугольную форму.

Рис. 2.31 Транзисторный ключ

Осциллограммы иллюстрирующие работу

ключа, приведены на рис.2.32. Входная

импульсная последовательность

![]() приведена на рис.2.32 (а). На интервале

приведена на рис.2.32 (а). На интервале![]() имеет место положительная амплитуда

импульса (

имеет место положительная амплитуда

импульса (![]() ),

величина которой больше

),

величина которой больше![]() ,

что обеспечивает режим отсечки (запирания)

транзистора. При этом ток базы

,

что обеспечивает режим отсечки (запирания)

транзистора. При этом ток базы![]() (рис.2.32 б), ток коллектора

(рис.2.32 б), ток коллектора![]() (рис.2.32 в) и напряжение коллектор-эмиттер

(рис.2.32 в) и напряжение коллектор-эмиттер![]() .

.

В момент времени

![]()

![]() переключается на

переключается на![]() .

Отрицательное напряжение открывает

транзистор и через эмиттерно-базовый

переход протекает ток

.

Отрицательное напряжение открывает

транзистор и через эмиттерно-базовый

переход протекает ток![]() ,

который должен ввести транзистор в

режим насыщения

,

который должен ввести транзистор в

режим насыщения![]() .

В силу малой ёмкости

.

В силу малой ёмкости![]() и шунтирующего действия открытого Э-Б

перехода с малым сопротивлением ток

базы изменяется по закону входной Э.Д.С.E(см. рис.2.32 б). В силу

инерционности транзистора, за счёт его

постоянной времени

и шунтирующего действия открытого Э-Б

перехода с малым сопротивлением ток

базы изменяется по закону входной Э.Д.С.E(см. рис.2.32 б). В силу

инерционности транзистора, за счёт его

постоянной времени![]() (схема с ОЭ), ток коллектора будет

возрастать по экспоненциальному закону

от начального значения

(схема с ОЭ), ток коллектора будет

возрастать по экспоненциальному закону

от начального значения![]() (момент

(момент![]() )

до

)

до

Рис. 2.32 Осциллограммы работы транзисторного ключа

некоторого

кажущегося значения

![]() .

Так бы происходило, если бы транзистор

всё время работал в активной области,

но спустя некоторое время он перейдёт

в режим насыщения и ток коллектора

достигнув значения

.

Так бы происходило, если бы транзистор

всё время работал в активной области,

но спустя некоторое время он перейдёт

в режим насыщения и ток коллектора

достигнув значения![]() (см. рис.2.32 в) не будет больше возрастать.

Напряжение на выходе ключа

(см. рис.2.32 в) не будет больше возрастать.

Напряжение на выходе ключа![]() ,

начиная с момента

,

начиная с момента![]() будет изменяться от

будет изменяться от![]() до

до![]() ,

повторяя закон изменения тока

,

повторяя закон изменения тока![]() ,

т.к.

,

т.к.![]() .

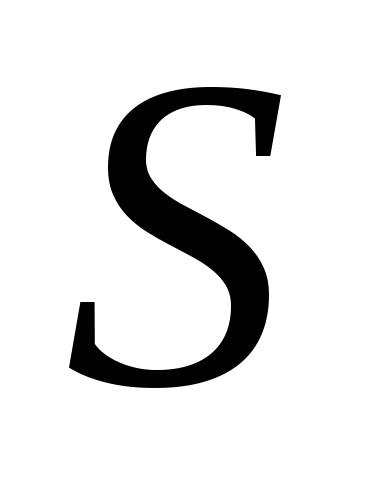

При этом время выключения транзистора,

это время за которое транзистор переходит

из режима отсечки в режим насыщения,

одинаково для тока

.

При этом время выключения транзистора,

это время за которое транзистор переходит

из режима отсечки в режим насыщения,

одинаково для тока![]() и напряжения

и напряжения![]() (см. рис.2.32 г). Для уменьшения времени

выключения увеличивают коэффициент

насыщенияS, что

увеличивает

(см. рис.2.32 г). Для уменьшения времени

выключения увеличивают коэффициент

насыщенияS, что

увеличивает ![]() значит

значит![]() .

Однако, на увеличениеSесть ограничения.

.

Однако, на увеличениеSесть ограничения.

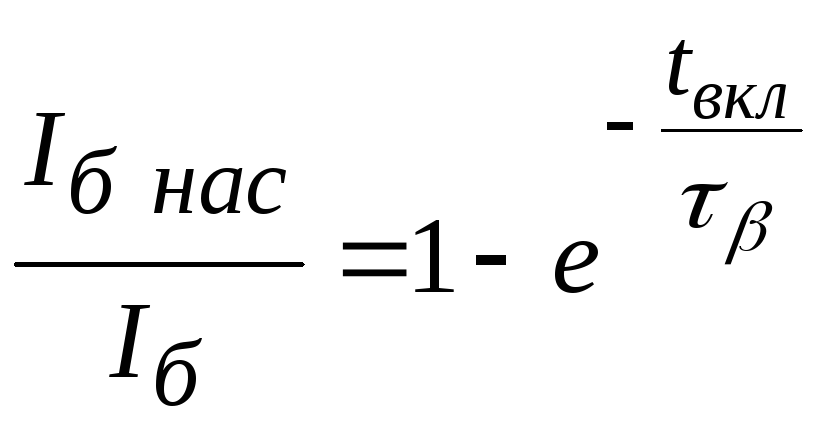

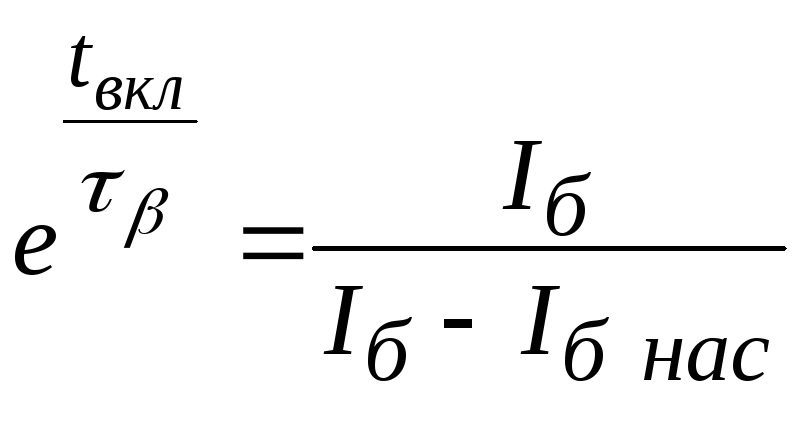

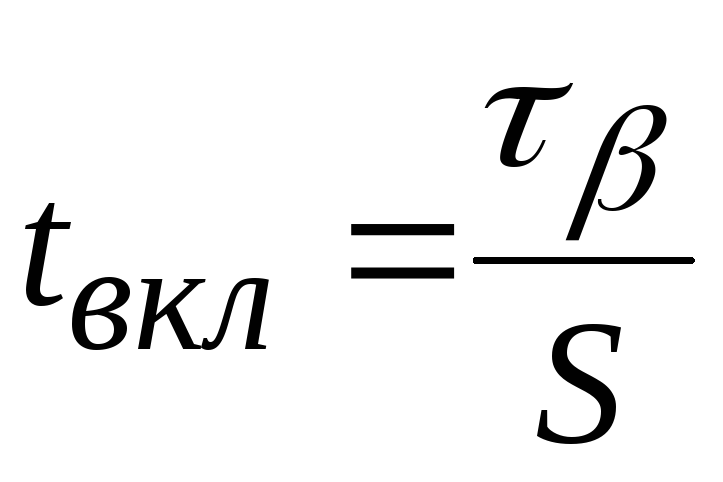

Рассчитаем время включения транзистора

![]() .

.

Текущее значение тока коллектора определяется выражением:

![]() ; где

; где![]() - постоянная времени транзистора с ОЭ;

- постоянная времени транзистора с ОЭ;

![]() .

.

![]() ; где

; где![]() ;

;

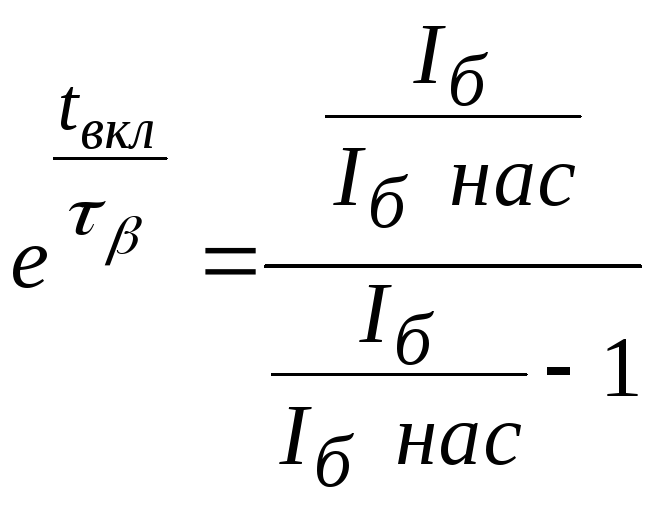

Подставив значение

![]() ,

получим:

,

получим:

![]() ;

;

За время

![]() ,

ток коллектора достигает значения

,

ток коллектора достигает значения![]() .

.

После подстановки

![]() ;

;![]() ,

получим:

,

получим:

![]() .

.

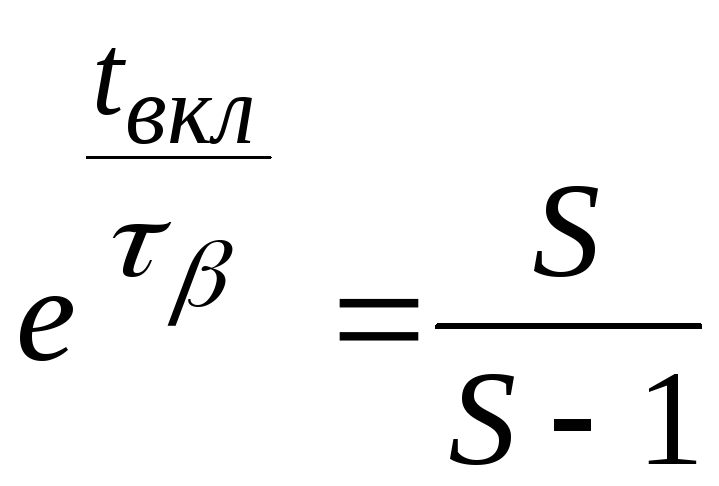

С учётом того, что

![]() ,

получим

,

получим

![]() ;

;

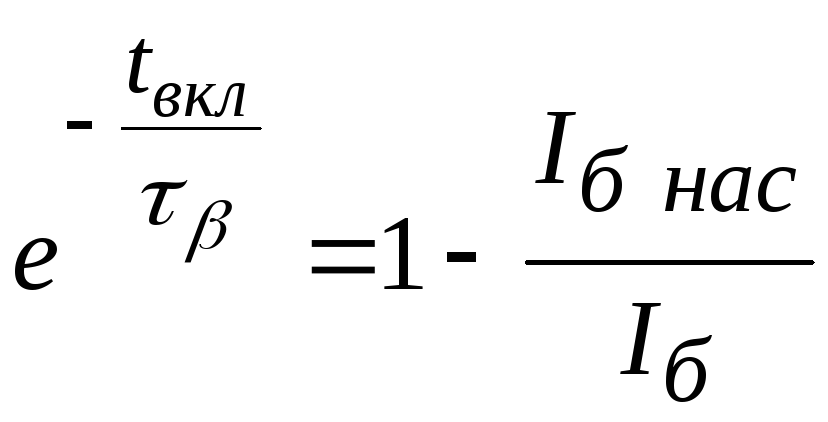

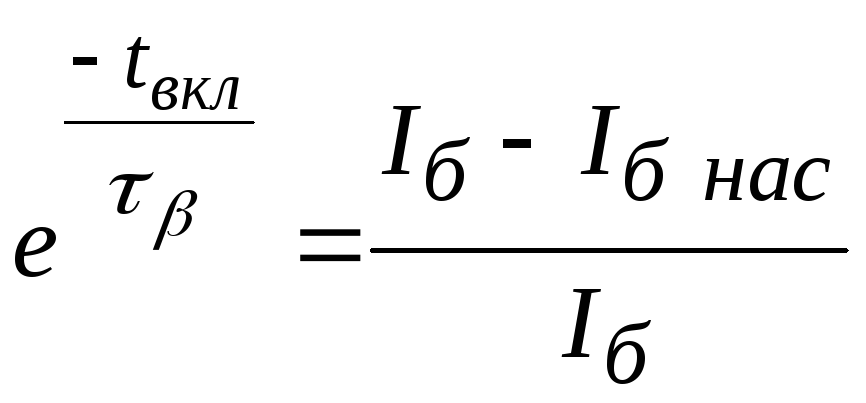

После преобразований, получим

,

откуда

,

откуда

;

; ;

;

;

; ;

;

.

.

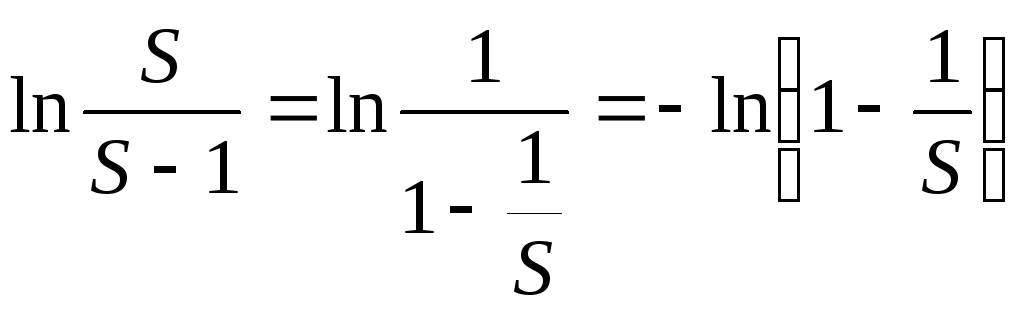

Отсюда определим время включения.

![]() .

.

поскольку

,

т.к. (

,

т.к. (![]() );

);

Следовательно, при больших Sобратная величина![]() ,

,

тогда:

![]() ;

(приближённая формула).

;

(приближённая формула).

После

![]() изменяется постоянная времени транзистора

и становится равной

изменяется постоянная времени транзистора

и становится равной![]() насыщения при этом

насыщения при этом![]() .

.

После момента времени

![]()

![]() ,

транзистор вновь запирается, однако

происходит задержка транзистора в

режиме насыщения на время, определяемое

временем рассасывания дырок в базе. Ток

базы достигает значения

,

транзистор вновь запирается, однако

происходит задержка транзистора в

режиме насыщения на время, определяемое

временем рассасывания дырок в базе. Ток

базы достигает значения![]() (см. рис.2.32 б) и уменьшается до

(см. рис.2.32 б) и уменьшается до![]() за время рассасывания. На такое же время

задерживается ток коллектора

за время рассасывания. На такое же время

задерживается ток коллектора![]() и напряжение на коллекторе

и напряжение на коллекторе![]() (рис.2.32 в,г).

(рис.2.32 в,г).

Время рассасывания можно рассчитать теоретически.

После

![]()

![]() должен изменятся от величины

должен изменятся от величины![]() до

до![]() .

.

![]() ,

,

где

![]() .

.

Время

![]() можно определить аналогично времени

можно определить аналогично времени![]() .

.

За

![]()

![]() изменяется от

изменяется от![]() до

до![]() ,

тогда

,

тогда

![]() ,

,

![]() ;

;

Отсюда следует, что с увеличением Sуменьшается![]() ,

однако возрастает

,

однако возрастает![]()

(![]()

![]() ),

поэтому рекомендуют брать

),

поэтому рекомендуют брать![]() .

.

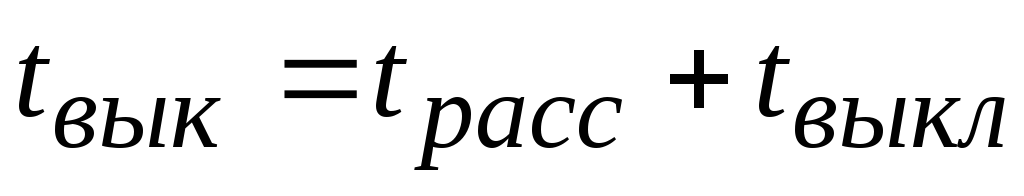

Определим время выключения

![]() .

За это время ток коллектора спадаетот

.

За это время ток коллектора спадаетот

![]() до

до![]() .

.

![]() ;

тогда суммарное время выключения по

току коллектора

;

тогда суммарное время выключения по

току коллектора![]() .

.

Установим время выключения

![]() по напряжению

по напряжению![]() .

Оно существенно отличается от

.

Оно существенно отличается от![]() .

На

.

На![]() существенное влияние оказывает ёмкость

существенное влияние оказывает ёмкость![]() ;

;

![]() ,

где

,

где![]() – выходная ёмкость транзистора

– выходная ёмкость транзистора![]() ,

,![]() – ёмкость монтажа,

– ёмкость монтажа,![]() – ёмкость нагрузки (см. рис.2.33).

– ёмкость нагрузки (см. рис.2.33).

Как правило

![]() порядка 10100пф.

порядка 10100пф.

Постоянная времени заряда конденсатора

![]() равна

равна![]() ,

следовательно задержка заднего фронта

,

следовательно задержка заднего фронта![]() определяет время выключения

определяет время выключения![]() .

.

Поскольку

![]() ,

то время выключения по напряжению

,

то время выключения по напряжению![]()

![]() ,

,![]() .

Для проектирования более быстродействующих

схем необходимо использовать в качестве

переключающей функции

.

Для проектирования более быстродействующих

схем необходимо использовать в качестве

переключающей функции![]() .

.

Рис. 2.33

ВЫВОДЫ:

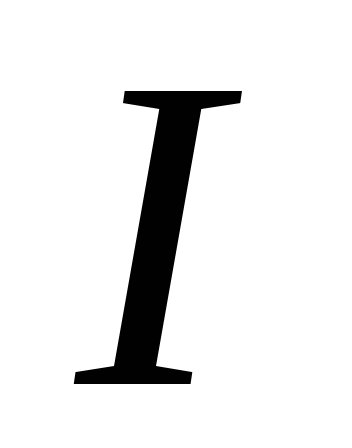

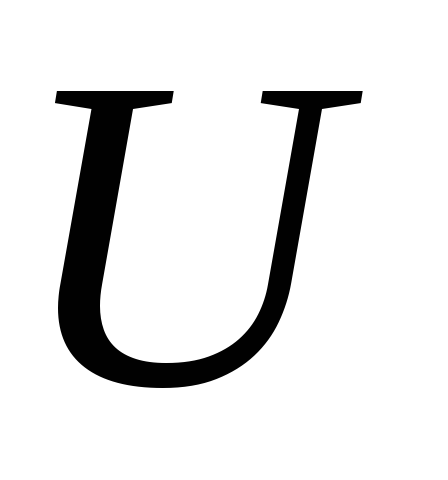

В схемах транзисторных ключей выходные импульсы UиI являются задержанными по отношению к входным импульсам.

Время задержки переднего фронта

пропорционально

пропорционально и обратно пропорционально

и обратно пропорционально ,

, .

Время включения по

.

Время включения по и

и одинаково.

одинаково.Время выключения

;

; пропорционально

пропорционально транзистора и коэффициенту насыщения

транзистора и коэффициенту насыщения ,

поэтому его принимают менее

,

поэтому его принимают менее .

. ,

т.к.

,

т.к. определяется

определяется .

Для его уменьшения рекомендуют ставить

.

Для его уменьшения рекомендуют ставить .

.