- •146 Цифровая схемотехника Конспект цифровая схемотехника

- •2. Формирователи прямоугольных импульсов

- •10. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы.

- •1.2 Прохождение импульсов через rc-цепи.

- •1.2.1 Напряжение и ток в rc-цепях под воздействием единичного скачка.

- •1.2.2 Дифференцирующая (укорачивающая) и разделительная rc-цепи.

- •1.2.3 Реальные rc-цепи при импульсном воздействии.

- •1.3 Фиксаторы уровня в дифференцирующих rc-цепях.

- •1.4 Интегрирующие rc-цепи.

- •Погрешности интегрирующей цепи:

- •2. Формирователи прямоугольных импульсов

- •2.1 Диодные ограничители последовательного и параллельного типа.

- •2.2 Линейные модели транзистора в режиме большого сигнала.

- •2.3 Расчет транзисторных ключей.

- •2.4 Транзисторный усилитель ограничитель.

- •2.5 Динамические характеристики транзисторных ключей.

- •3. Мультивибраторы

- •3.2 Транзисторный мультивибратор. Принцип действия, осциллограм-мы работы мультивибратора

- •3.3 Расчет периода колебаний мультивибратора

- •3.4 Регулировка частоты, термостабилизация и улучшение формы выходного напряжения мультивибратора.

- •3.5 Транзисторный одновибратор. Принцип действия, осциллограммы.

- •4. Потенциальные логичекие элементы

- •4.2 Диодная логика. Логика «и»

- •Логика «или»

- •Недостатки диодной логики: схемы критичны к внутреннему сопротивлению источников эдс (), обладают нестабильными уровнями логического «0» и «1».

- •4.3 Диодно-транзисторная логика (дтл)

- •4.4 Транзистор-транзисторная логика (ттл)

- •4.5 Логические элементы на моп и кмоп-структурах.

- •5.1 Мультивибраторы на потенциальных логических элементах.

- •5.2 Одновибраторы на потенциальных логических элементах.

- •5.2 Одновибраторы на потенциальных логических элементах.

- •Расчет длительности импульса одновибратора.

- •6.1 Кодирование временных интервалов.

- •6.2 Кодирование напряжение.

- •6.3 Аналогово-цифровые преобразователи (ацп). Основные характеристики и параметры.

- •6.3.1 Ацп на параллельных компараторах;

- •6.3.2 Ацп поразрядного кодирования.

- •6.4 Цифро-аналоговые преобразователи (цап). Структура, основные характеристики и параметры.

- •6.4.1 Взвешенная схема, управляющая напряжением.

- •6.5 Устройство выборки хранения.

- •7.1 Общая характеристика и принципы построения глин.

- •7.2 Автоколебательные глин на транзисторах.

- •7.3 Ждущие глин на транзисторах.

- •7.4 Глин на оупт.

- •8.2 Автоколебательный блокинг-генератор.

- •8.3 Ждущий блокинг-генератор.

- •8.4 Синхронизация блокинг-генератора.

- •9.1 Оперативные запоминающие устройства (озу) с произвольным доступом.

- •9.2 Статические и динамические зу.

- •9.3 Построение плат памяти.

- •9.4 Программируемые запоминающие устройства (пзу).

- •10. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы.

- •10.2 Программируемые логические матрицы (плм).

- •10.2.1 Схемотехника плм

- •10.2.2 Подготовка задачи к решению с помощью плм

- •10.2.3 Программирование плм

- •10.2.4 Упрощенное изображение схем плм

- •10.2.5 Воспроизведение скобочных форм переключательных функций

- •10.2.6 Наращивание (расширение) плм

2. Формирователи прямоугольных импульсов

2.1 Диодные ограничители последовательного и параллельного типа.

2.2 Линейные модели транзистора в режиме большого сигнала.

2.3 Расчет транзисторных ключей.

2.4 Транзисторный усилитель ограничитель.

2.5 Динамические характеристики транзисторных ключей.

2.1 Диодные ограничители последовательного и параллельного типа.

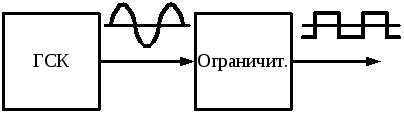

Формирование прямоугольных импульсов можно получить с помощью генератора синусоидальных колебаний и ограничителя (см. рис.2.1).

Рис. 2.1

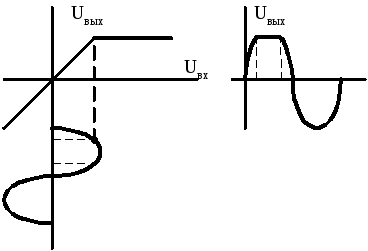

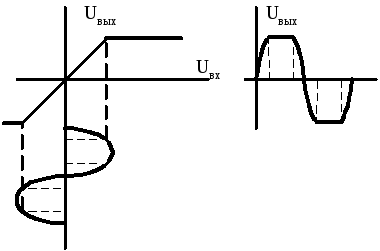

Различают ограничители сверху,снизуидвухсторонниеограничители. Амплитудные характеристики ограничителей и осциллограммы, иллюстрирующие их работу приведены на рис.2.2, 2.3 и 2.4.

Рис. 2.2 Ограничитель сверху

Рис. 2.3 Ограничитель снизу

Рис. 2.4 Двустороннийограничитель

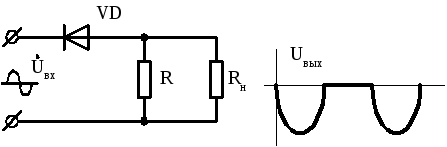

Последовательные диодные ограничители.

Принципиальная схема последовательного

ограничителя снизу на нулевом уровне

приведена на рис.2.5 вместе с осциллограммой,

иллюстрирующей её работу. Сопротивление

нагрузки должно быть намного больше

сопротивления ограничителя

![]() (

(![]() ),

а внутреннее сопротивление источника

синусоидального сигнала

),

а внутреннее сопротивление источника

синусоидального сигнала![]() .

Для обеспечения протекания тока на

интервале от 0 до

.

Для обеспечения протекания тока на

интервале от 0 до![]()

![]() ,

где

,

где![]() - напряжение на диоде включённом в

проводящем направлении, величина

которого порядка 0,5В.

- напряжение на диоде включённом в

проводящем направлении, величина

которого порядка 0,5В.

Рис. 2.5 Последовательный диодный ограничитель

Схема ограничителя сверхуна нулевом

уровне и осциллограммы её работы имеют

вид, приведенный на рис.2.6. Для обеспечения

нормальной работы схемы необходимо

выполнение тех же условий:![]() ,

,![]() ,

,![]() .

.

Рис. 2.6 Ограничитель сверхуна нулевом уровне

Для того чтобы схемы ограничителей были универсальными, они должны обеспечивать ограничения на произвольном уровне.

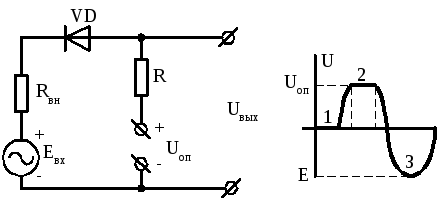

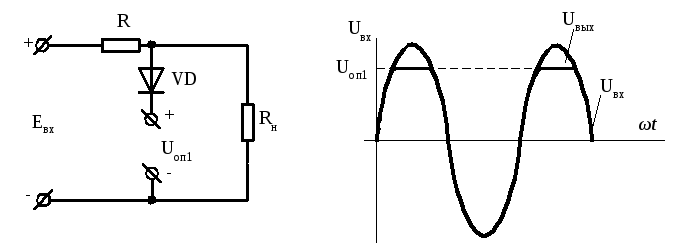

Схема ограничителя сверху на произвольном уровне приведена на рис.2.7.

Полярность источника Э.Д.С.

![]() выбирают так, чтобы диодVDбыл открыт при

выбирают так, чтобы диодVDбыл открыт при![]() .

Поскольку

.

Поскольку![]() и

и![]() немного меньше величины резистораR,

можно сделать допущения, что

немного меньше величины резистораR,

можно сделать допущения, что![]() ;

;![]() .

.

Рис. 2.7 Ограничитель произвольного уровня

![]() может изменяться в пределах

может изменяться в пределах![]()

При выполнении условия

![]() диодVDоткрыт и можно

сделать допущение

диодVDоткрыт и можно

сделать допущение![]() .

.

Если

![]() ,

тоVD-закрыт: ток в

контуре (и через резисторR)

равен нулю, следовательно

,

тоVD-закрыт: ток в

контуре (и через резисторR)

равен нулю, следовательно![]() (интервал времени

(интервал времени![]() ).

На интервале от 0 до

).

На интервале от 0 до![]() ,

когда

,

когда![]() ,

то и

,

то и![]() .

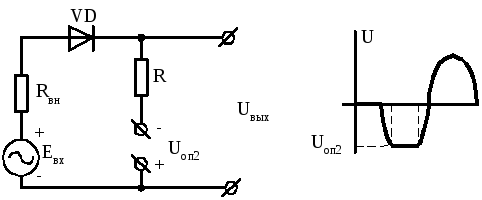

Схема ограничителяснизуна

произвольном уровне приведена на рис.2.8

.

Схема ограничителяснизуна

произвольном уровне приведена на рис.2.8

ωt ωt1 ωt2 ωt3

Рис. 2.8 Ограничитель снизуна произвольном уровне

Работа схемы, осциллограмма и допущения аналогичны рассмотренным выше.

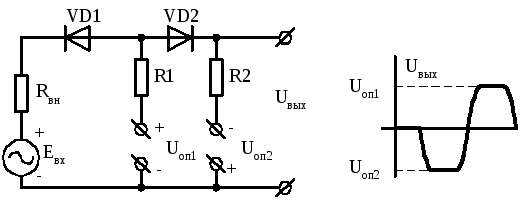

Схема ограничителя уровня сверхуиснизуна произвольных уровнях представляют собой комбинацию двух рассмотренных схем включённых последовательно, см.рис.2.9. Ограничения, работа и осциллограммы аналогичны.

ωt

Рис. 2.9 Ограничитель сверхуиснизуна произвольных уровнях

К недостаткам последовательных диодных ограничителей относят:

Ограничители требуют идеальных источников Э.Д.С. входного сигнала (

);

);Схемы пассивны и имеют коэффициент передачи К<1;

Величина Э.Д.С.

должна быть большой (десятки вольт),

т.е. должно выполнятся условие

должна быть большой (десятки вольт),

т.е. должно выполнятся условие .

.

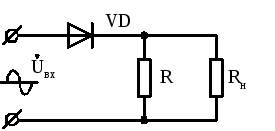

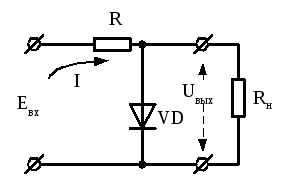

Параллельные диодные ограничители.

Основным недостатком последовательных диодных ограничителей является требование низкого внутреннего сопротивления Э.Д.С. источника сигнала. Для ликвидации этого недостатка разработаны параллельные диодные ограничители. Такие схемы ограничителей не требуют очень низкого выходного сопротивления источника Э.Д.С.

![]() ;

;![]() ;

;

Схема диодного ограничителя сверху, примерно на нулевом уровне и осциллограммы, иллюстрирующие её работу приведены на рис.2.10.

Приняв аналогичные допущения

![]() и

и![]() ,

опишем схему системой уравнений (1,2):

,

опишем схему системой уравнений (1,2):

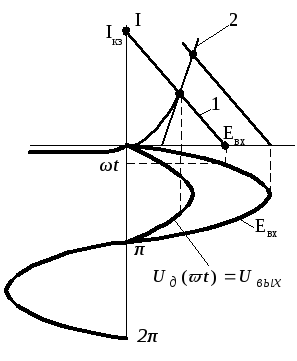

Рис. 2.10 Параллельный диодный ограничитель

![]() ;

(1)

;

(1)

![]() ; (2)

; (2)

Уравнение (1) – нагрузочная прямая, (2) –

вольт-амперная характеристика диода.

Построив нагрузочную прямую по точкам

Х.Х. и К.З. (![]() ,

,![]() ;

;![]() ,

,![]() )

строим осциллограмму

)

строим осциллограмму![]() .

Получим ограничение сверху на уровне

.

Получим ограничение сверху на уровне![]() .

.

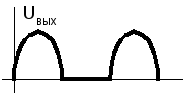

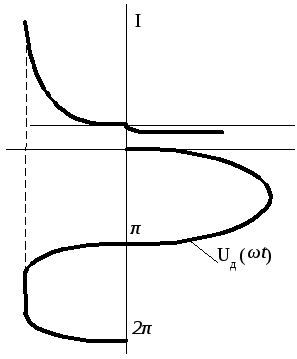

Параллельный диодный ограничитель снизу на примерно нулевом уровне с осциллограммами приведён на рис.2.11.

Рис. 2.11 Параллельный диодный ограничитель снизу на нулевом уровне

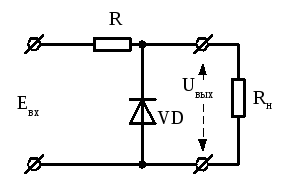

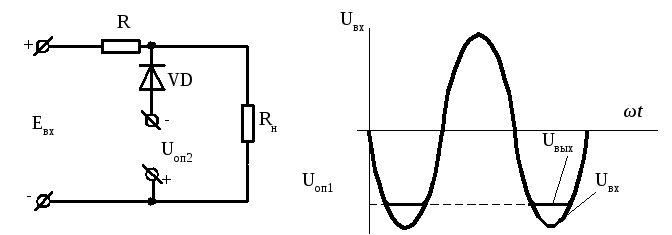

Ограничитель сверхуиснизуна произвольных уровнях приведены на рис.2.12 и 2.13 соответственно.

Рис. 2.12 Параллельный диодный ограничитель сверхуна произвольном уровне

Рис. 2.13 Параллельный диодный ограничитель снизуна произвольном уровне

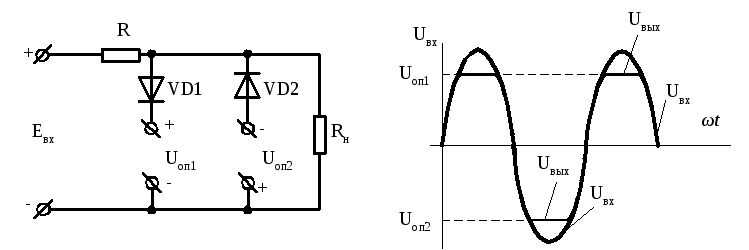

Схема двухстороннего ограничителя на произвольных уровнях приведена на рис.2.14.

Рис. 2.14 Двухсторонний диодный ограничитель на произвольном уровне

ВЫВОДЫ:

Параллельные диодные ограничители не

критичны к

![]() источника входного сигнала, однако

обладают теми же остальными недостатками

последовательных диодных ограничителей

– имеют низкий коэффициент передачи,

требуют большие входные сигналы

источника входного сигнала, однако

обладают теми же остальными недостатками

последовательных диодных ограничителей

– имеют низкий коэффициент передачи,

требуют большие входные сигналы![]() и буферный каскад для согласования с

и буферный каскад для согласования с![]() .

.

Для ликвидации общих недостатков диодных ограничителей разработаны транзисторные усилители-ограничители, у которых существенно более низкие входные сигналы (сотни милливольт), относительно высокое входное , и низкое выходное сопротивления и лучшая форма (коэффициент прямоугольности) выходного напряжения.