- •146 Цифровая схемотехника Конспект цифровая схемотехника

- •2. Формирователи прямоугольных импульсов

- •10. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы.

- •1.2 Прохождение импульсов через rc-цепи.

- •1.2.1 Напряжение и ток в rc-цепях под воздействием единичного скачка.

- •1.2.2 Дифференцирующая (укорачивающая) и разделительная rc-цепи.

- •1.2.3 Реальные rc-цепи при импульсном воздействии.

- •1.3 Фиксаторы уровня в дифференцирующих rc-цепях.

- •1.4 Интегрирующие rc-цепи.

- •Погрешности интегрирующей цепи:

- •2. Формирователи прямоугольных импульсов

- •2.1 Диодные ограничители последовательного и параллельного типа.

- •2.2 Линейные модели транзистора в режиме большого сигнала.

- •2.3 Расчет транзисторных ключей.

- •2.4 Транзисторный усилитель ограничитель.

- •2.5 Динамические характеристики транзисторных ключей.

- •3. Мультивибраторы

- •3.2 Транзисторный мультивибратор. Принцип действия, осциллограм-мы работы мультивибратора

- •3.3 Расчет периода колебаний мультивибратора

- •3.4 Регулировка частоты, термостабилизация и улучшение формы выходного напряжения мультивибратора.

- •3.5 Транзисторный одновибратор. Принцип действия, осциллограммы.

- •4. Потенциальные логичекие элементы

- •4.2 Диодная логика. Логика «и»

- •Логика «или»

- •Недостатки диодной логики: схемы критичны к внутреннему сопротивлению источников эдс (), обладают нестабильными уровнями логического «0» и «1».

- •4.3 Диодно-транзисторная логика (дтл)

- •4.4 Транзистор-транзисторная логика (ттл)

- •4.5 Логические элементы на моп и кмоп-структурах.

- •5.1 Мультивибраторы на потенциальных логических элементах.

- •5.2 Одновибраторы на потенциальных логических элементах.

- •5.2 Одновибраторы на потенциальных логических элементах.

- •Расчет длительности импульса одновибратора.

- •6.1 Кодирование временных интервалов.

- •6.2 Кодирование напряжение.

- •6.3 Аналогово-цифровые преобразователи (ацп). Основные характеристики и параметры.

- •6.3.1 Ацп на параллельных компараторах;

- •6.3.2 Ацп поразрядного кодирования.

- •6.4 Цифро-аналоговые преобразователи (цап). Структура, основные характеристики и параметры.

- •6.4.1 Взвешенная схема, управляющая напряжением.

- •6.5 Устройство выборки хранения.

- •7.1 Общая характеристика и принципы построения глин.

- •7.2 Автоколебательные глин на транзисторах.

- •7.3 Ждущие глин на транзисторах.

- •7.4 Глин на оупт.

- •8.2 Автоколебательный блокинг-генератор.

- •8.3 Ждущий блокинг-генератор.

- •8.4 Синхронизация блокинг-генератора.

- •9.1 Оперативные запоминающие устройства (озу) с произвольным доступом.

- •9.2 Статические и динамические зу.

- •9.3 Построение плат памяти.

- •9.4 Программируемые запоминающие устройства (пзу).

- •10. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы.

- •10.2 Программируемые логические матрицы (плм).

- •10.2.1 Схемотехника плм

- •10.2.2 Подготовка задачи к решению с помощью плм

- •10.2.3 Программирование плм

- •10.2.4 Упрощенное изображение схем плм

- •10.2.5 Воспроизведение скобочных форм переключательных функций

- •10.2.6 Наращивание (расширение) плм

10.2 Программируемые логические матрицы (плм).

Программируемые логические матрицы появились в середине 70-х годов. Основой их служит последовательность программируемых матриц элементов И и ИЛИ. В структуру входят также блоки входных и выходных буферных каскадов (БВх и БВых). Входные буферы, если они не выполняют более сложных действий, преобразуют однофазные входные сигналы в парафазные и формируют сигналы необходимой мощности для питания матрицы элементов И. Выходные буферы обеспечивают необходимую нагрузочную способность выходов, разрешают или запрещают выход ПЛМ на внешние шины с помощью сигнала ОЕ, а иногда выполняют и более сложные действия.

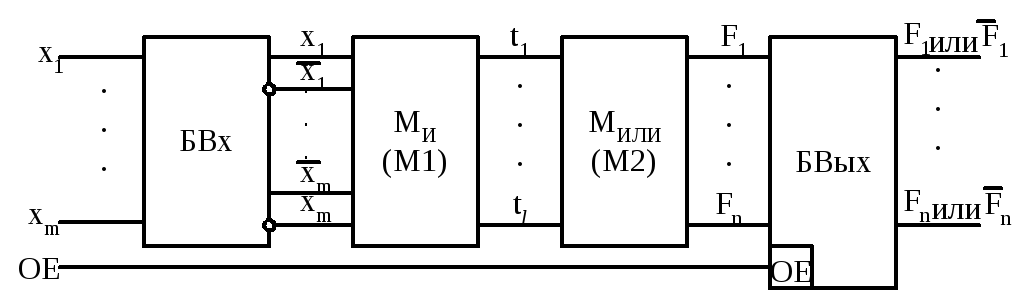

Основными параметрами ПЛМ (рис. 10.1) являются число входов m, число термов l и число выходов n.

Рис.10.1. Базовая структура ПЛМ

Переменные x1...хm подаются через БВх на входы элементов И (конъюнкторов), и в матрице И образуются l термов t. Под термом здесь понимается конъюнкция, связывающая входные переменные, представленные в прямой или инверсной форме. Число формируемых термов равно числу конъюнкторов или, что то же самое, числу выходов матрицы И. Термы подаются далее на входы матрицы ИЛИ, т. е. на входы дизъюнкторов, формирующих выходные функции. Число дизъюнкторов равно числу вырабатываемых функций n.

Таким образом, ПЛМ реализует дизъюнктивную нормальную форму (ДНФ) воспроизводимых функций (двухуровневую логику). ПЛМ способна реализовать систему п логических функций от m аргументов, содержащую не более l термов. Воспроизводимые функции являются комбинациями из любого числа термов, формируемых матрицей И. Какие именно термы будут выработаны и какие комбинации этих термов составят выходные функции, определяется программированием ПЛМ.

10.2.1 Схемотехника плм

Выпускаются ПЛМ как на основе биполярной технологии, так и на МОП-транзисторах. В матрицах имеются системы горизонтальных и вертикальных связей, в узлах пересечения которых при программировании создаются или ликвидируются элементы связи.

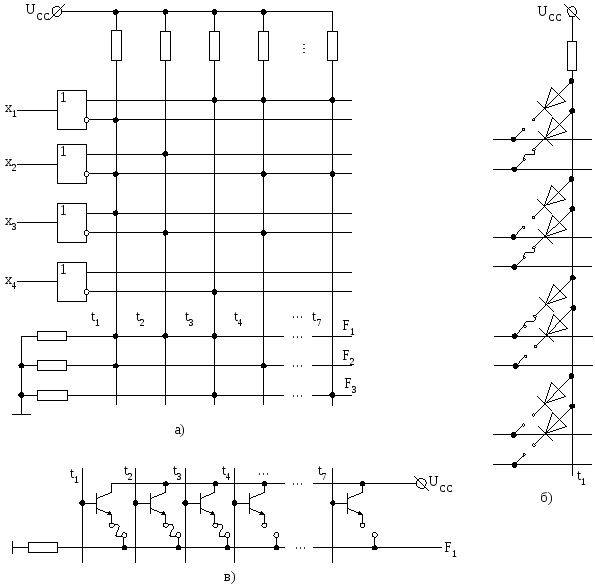

На рис. 10.2, а в упрощенном виде (без буферных элементов) показана схемотехника биполярной ПЛМ К556РТ1 с программированием пережиганием перемычек. Показан фрагмент для воспроизведения системы функций размерностью 4, 7, 3: параметры микросхемы К556РТ1 обеспечивают размерность 16, 48, 8, что достаточно для ее использования при решении указанной системы.

![]() ;

;

![]() ;

;

![]() .

.

Элементами связей в матрице И служат диоды, соединяющие горизонтальные и вертикальные шины, как показано на рис. 10.2,б, изображающем цепи выработки терма t1. Совместно с резистором и источником питания цепи выработки термов образуют обычные диодные схемы И.

До

программирования все перемычки целы,

и диоды связи размещены во всех узлах

координатной сетки. При любой

комбинации аргументов на выходе будет

ноль, т. к. на вход схемы подаются

одновременно прямые и инверсные значения

аргументов, а

![]() .

При программировании в схеме оставляются

только необходимые элементы связи, а

ненужные устраняются пережиганием

перемычек. В данном случае на вход

конъюнктора поданы

.

При программировании в схеме оставляются

только необходимые элементы связи, а

ненужные устраняются пережиганием

перемычек. В данном случае на вход

конъюнктора поданы![]() ,

,![]() и

и![]() .

Высокий уровень выходного напряжения

(логическая единица) появится только

при наличии высоких напряжений на всех

входах. Низкое напряжение хотя бына

одном из входов фиксирует выходное

напряжение на низком уровне, т. к.

открывается диод этого входа. Таким

образом выполняется операция И, в данном

случае вырабатывается терм

.

Высокий уровень выходного напряжения

(логическая единица) появится только

при наличии высоких напряжений на всех

входах. Низкое напряжение хотя бына

одном из входов фиксирует выходное

напряжение на низком уровне, т. к.

открывается диод этого входа. Таким

образом выполняется операция И, в данном

случае вырабатывается терм

![]() .

.

Рис. 10.2. Схемотехника ПЛМ, реализованной в биполярной технологии(а). Элементы связей в матрицах И (б) и ИЛИ (в)

Элементами связи в матрице ИЛИ служат транзисторы (рис. 10.2, в), включенные по схеме эмиттерного повторителя относительно линий термов и образующие схему ИЛИ относительно выхода (горизонтальной линии). На рис.10.2, в показана выработка функции F1. Работа схемы ИЛИ, реализована в виде параллельного соединения эмиттерных повторителей. При изображении запрограммированных матриц наличие элементов связей (целые перемычки) отмечается точкой в соответствующем узле.

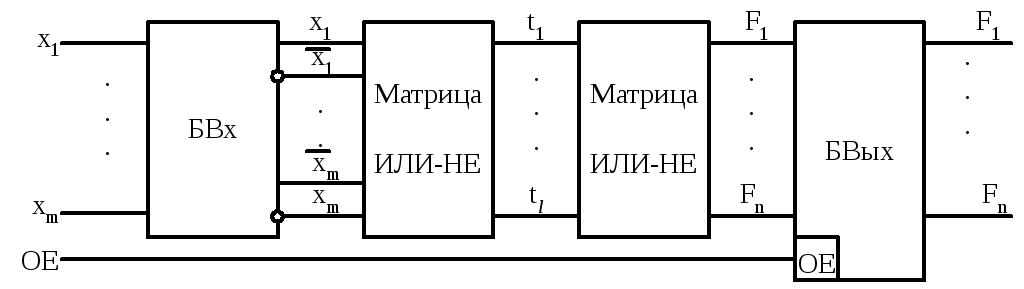

В схемах на МОП-транзисторах в качестве базовой логической ячейки используют инвертирующие элементы (ИЛИ-НЕ, И-НЕ). Соответственно этому изменяются и операции, реализуемые в первой и второй матрицах ПЛМ. В частности, в схемотехнике п-МОП базовой ячейкой обычно служит ячейка ИЛИ-НЕ, а структура ПЛМ имеет вид (рис. 10.3). Такая ПЛМ является последовательностью двух матриц ИЛИ-НЕ, одна из которых служит для выработки термов, другая — для выработки выходных функций.

Терм

![]() в данном случае равен:

в данном случае равен:

![]() ,

,

а функция:

![]() .

.

Рис. 10.3. Схемотехника ПЛМ, реализованной на n-МОП-транзисторах

На основании этих выражений можно заключить, что известная связь между, операциями, выражаемая правилами де Моргана, говорит о фактическом совпадении функциональных характеристик биполярной ПЛМ и ПЛМ на МОП-транзисторах: если на входы последней подавать аргументы, инвертированные относительно аргументов биполярной ПЛМ, то на выходе получим результат, отличающийся от выхода биполярной ПЛМ только инверсией.