- •146 Цифровая схемотехника Конспект цифровая схемотехника

- •2. Формирователи прямоугольных импульсов

- •10. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы.

- •1.2 Прохождение импульсов через rc-цепи.

- •1.2.1 Напряжение и ток в rc-цепях под воздействием единичного скачка.

- •1.2.2 Дифференцирующая (укорачивающая) и разделительная rc-цепи.

- •1.2.3 Реальные rc-цепи при импульсном воздействии.

- •1.3 Фиксаторы уровня в дифференцирующих rc-цепях.

- •1.4 Интегрирующие rc-цепи.

- •Погрешности интегрирующей цепи:

- •2. Формирователи прямоугольных импульсов

- •2.1 Диодные ограничители последовательного и параллельного типа.

- •2.2 Линейные модели транзистора в режиме большого сигнала.

- •2.3 Расчет транзисторных ключей.

- •2.4 Транзисторный усилитель ограничитель.

- •2.5 Динамические характеристики транзисторных ключей.

- •3. Мультивибраторы

- •3.2 Транзисторный мультивибратор. Принцип действия, осциллограм-мы работы мультивибратора

- •3.3 Расчет периода колебаний мультивибратора

- •3.4 Регулировка частоты, термостабилизация и улучшение формы выходного напряжения мультивибратора.

- •3.5 Транзисторный одновибратор. Принцип действия, осциллограммы.

- •4. Потенциальные логичекие элементы

- •4.2 Диодная логика. Логика «и»

- •Логика «или»

- •Недостатки диодной логики: схемы критичны к внутреннему сопротивлению источников эдс (), обладают нестабильными уровнями логического «0» и «1».

- •4.3 Диодно-транзисторная логика (дтл)

- •4.4 Транзистор-транзисторная логика (ттл)

- •4.5 Логические элементы на моп и кмоп-структурах.

- •5.1 Мультивибраторы на потенциальных логических элементах.

- •5.2 Одновибраторы на потенциальных логических элементах.

- •5.2 Одновибраторы на потенциальных логических элементах.

- •Расчет длительности импульса одновибратора.

- •6.1 Кодирование временных интервалов.

- •6.2 Кодирование напряжение.

- •6.3 Аналогово-цифровые преобразователи (ацп). Основные характеристики и параметры.

- •6.3.1 Ацп на параллельных компараторах;

- •6.3.2 Ацп поразрядного кодирования.

- •6.4 Цифро-аналоговые преобразователи (цап). Структура, основные характеристики и параметры.

- •6.4.1 Взвешенная схема, управляющая напряжением.

- •6.5 Устройство выборки хранения.

- •7.1 Общая характеристика и принципы построения глин.

- •7.2 Автоколебательные глин на транзисторах.

- •7.3 Ждущие глин на транзисторах.

- •7.4 Глин на оупт.

- •8.2 Автоколебательный блокинг-генератор.

- •8.3 Ждущий блокинг-генератор.

- •8.4 Синхронизация блокинг-генератора.

- •9.1 Оперативные запоминающие устройства (озу) с произвольным доступом.

- •9.2 Статические и динамические зу.

- •9.3 Построение плат памяти.

- •9.4 Программируемые запоминающие устройства (пзу).

- •10. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы.

- •10.2 Программируемые логические матрицы (плм).

- •10.2.1 Схемотехника плм

- •10.2.2 Подготовка задачи к решению с помощью плм

- •10.2.3 Программирование плм

- •10.2.4 Упрощенное изображение схем плм

- •10.2.5 Воспроизведение скобочных форм переключательных функций

- •10.2.6 Наращивание (расширение) плм

9.4 Программируемые запоминающие устройства (пзу).

ПЗУ — память, информация в которой, будучи однажды записанной, изменению не подлежит. Например, программа загрузки в ОЗУ МП системы из внешней памяти.

Существуют 4 типа ПЗУ:

Простые ПЗУ — информация записана один раз и навсегда в процессе ее изготовления (ПЗУ с масочным программированием).

Программируемые ПЗУ (ППЗУ) — комбинация битов, вводимое в ППЗУ может быть задана пользователем. ППЗУ программируется в виде однократно выполненной операции, т.е. информация, записанная в ППЗУ, не может быть изменена.

Стираемое ППЗУ (СППЗУ) — пользователь может запрограммировать ПЗУ, работать с этим ПЗУ, затем стереть и записать новую информацию (СППЗУ с ультрафиолетовым стиранием).

Электронно-изменяющееся ПЗУ (ЭИПЗУ) — программирование и изменение содержимого ПЗУ осуществляется с помощью электронных средств. В отличие от СППЗУ для стирания информации не требуется специальных внешних устройств.

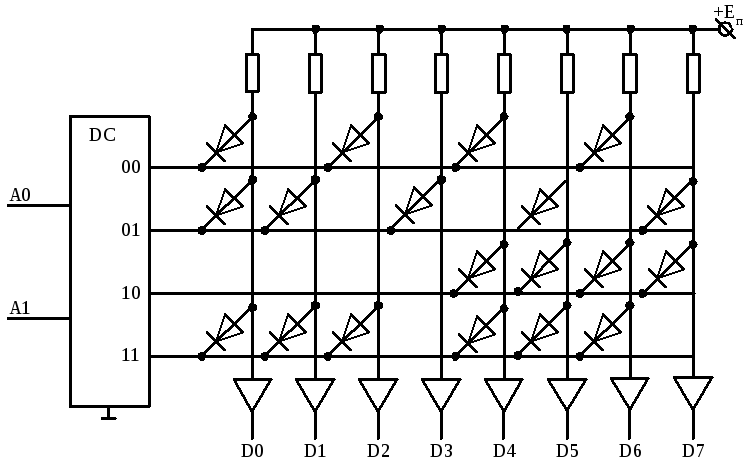

На рис. 9.8. приведено простое ПЗУ.

Для реализации ПЗУ достаточно использовать дешифратор, диоды, набор резисторов и шинные формирователи. Рассматриваемое ПЗУ содержит 4 8 разрядных слова, т.е. его общий объем составляет 32 бит. Количество столбцов определяет разрядность слова, а количество строк — количество 8 разрядных слов. Диоды устанавливаются в тех местах, где должны храниться биты, имеющие значение логического «0» (дешифратор подает 0 на выбранную строку). В настоящее время вместо диодов ставят МОП-транзисторы.

Рис. 9.8. Схема простого ПЗУ.

В таблице 9.1 приведено состояние простого ПЗУ, схема которого приведена на рисунке 9.8.

Таблица 9.1. Состояние простого ПЗУ.

|

Слово |

Двоичное представление | ||||||||

|

А0 |

А1 |

D1 |

D2 |

D3 |

D4 |

D5 |

D6 |

D7 |

D8 |

|

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

|

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

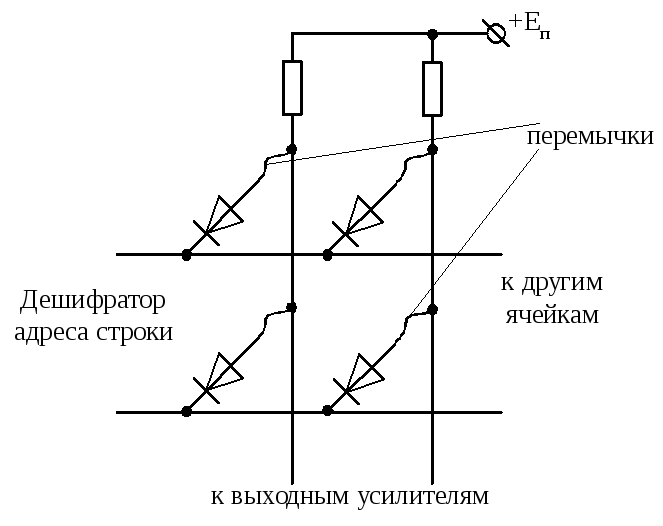

На рисунке 9.9 приведена схема ППЗУ, которое программируется пользователем и носит название ППЗУ с пережигаемыми перемычками. Оно изготавливается со всеми диодами и перемычками, т.е. в матрице все «0», а при программировании пережигаются те перемычки, в ячейках которых должны быть логические «1».

Рис. 9.9. Фрагмент схемы ППЗУ.

10. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы.

10.1 Общие понятия и определения.

10.2 Программируемые логические матрицы (ПЛМ).

10.2.1 Схемотехника ПЛМ;

10.2.2 Подготовка задачи к решению с помощью ПЛМ;

10.2.3 Программирование ПЛМ;

10.2.4 Упрощенное изображение схем ПЛМ;

10.2.5 Воспроизведение скобочных форм переключательных функций;

10.2.6 Наращивание (расширение) ПЛМ.

10.1 Общие понятия и определения.

В цифровые системы обработки информации входят процессор, память, периферийные устройства и интерфейсные схемы. Процессор является стандартным устройством — он не изготавливаются для конкретной системы по специальному заказу, а решает требуемую задачу путем последовательного выполнения определенных команд из присущей ему системы команд. Память также реализуется стандартными микросхемами — ее функции остаются одними и теми же для разных систем.

Стандартные БИС/СБИС лидируют по уровню интеграции, т. к. высокая стоимость проектирования оптимизированных по плотности БИС/СБИС, достигающая сотен миллионов долларов, оказывается в данном случае приемлемой, поскольку раскладывается на большое число производимых микросхем.

Наряду со стандартными в системе присутствуют и некоторые нестандартные части, специфичные для данной разработки. Это относится к схемам управления блоками, обеспечения их взаимодействия и др. Реализация нестандартной части системы исторически была связана с применением микросхем малого (МИС) и среднего (СИС) уровней интеграции. Применение МИС и СИС сопровождается резким ростом числа корпусов ИС на платах, усложнением монтажа, снижением надежности системы и ее быстродействия. В то же время заказать для системы специализированные ИС высокого уровня интеграции затруднительно, т. к. это связано с очень большими затратами средств и времени на их проектирование.

Возникшее противоречие нашло разрешение на путях разработки БИС/СБИС с программируемой и репрограммируемой структурами. Первыми представителями указанного направления явились программируемые логические матрицы ПЛМ (PLA, Programmable Logic Array), программируемая матричная логика ПМЛ (PAL, Programmable Array Logic) и базовые матричные кристаллы БМК, называемые также вентильными матрицами ВМ (GA, Gate Array). PLA и PAL в английской терминологии объединяются также термином PLD, Programmable Logic Devices. Развитие БИС/СБИС с программируемой и репрограммируемой структурой оказалось настолько перспективным направлением, что привело к созданию новых эффективных средств разработки цифровых систем, таких как CPLD (Complex PLD), FPGA (Field Programmable GA) и SPGA (System Programmable GA). В рамках современных БИС/СБИС с программируемой и репрограммируемой структурой стала решаться и задача создания целой системы на одном кристалле.