- •146 Цифровая схемотехника Конспект цифровая схемотехника

- •2. Формирователи прямоугольных импульсов

- •10. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы.

- •1.2 Прохождение импульсов через rc-цепи.

- •1.2.1 Напряжение и ток в rc-цепях под воздействием единичного скачка.

- •1.2.2 Дифференцирующая (укорачивающая) и разделительная rc-цепи.

- •1.2.3 Реальные rc-цепи при импульсном воздействии.

- •1.3 Фиксаторы уровня в дифференцирующих rc-цепях.

- •1.4 Интегрирующие rc-цепи.

- •Погрешности интегрирующей цепи:

- •2. Формирователи прямоугольных импульсов

- •2.1 Диодные ограничители последовательного и параллельного типа.

- •2.2 Линейные модели транзистора в режиме большого сигнала.

- •2.3 Расчет транзисторных ключей.

- •2.4 Транзисторный усилитель ограничитель.

- •2.5 Динамические характеристики транзисторных ключей.

- •3. Мультивибраторы

- •3.2 Транзисторный мультивибратор. Принцип действия, осциллограм-мы работы мультивибратора

- •3.3 Расчет периода колебаний мультивибратора

- •3.4 Регулировка частоты, термостабилизация и улучшение формы выходного напряжения мультивибратора.

- •3.5 Транзисторный одновибратор. Принцип действия, осциллограммы.

- •4. Потенциальные логичекие элементы

- •4.2 Диодная логика. Логика «и»

- •Логика «или»

- •Недостатки диодной логики: схемы критичны к внутреннему сопротивлению источников эдс (), обладают нестабильными уровнями логического «0» и «1».

- •4.3 Диодно-транзисторная логика (дтл)

- •4.4 Транзистор-транзисторная логика (ттл)

- •4.5 Логические элементы на моп и кмоп-структурах.

- •5.1 Мультивибраторы на потенциальных логических элементах.

- •5.2 Одновибраторы на потенциальных логических элементах.

- •5.2 Одновибраторы на потенциальных логических элементах.

- •Расчет длительности импульса одновибратора.

- •6.1 Кодирование временных интервалов.

- •6.2 Кодирование напряжение.

- •6.3 Аналогово-цифровые преобразователи (ацп). Основные характеристики и параметры.

- •6.3.1 Ацп на параллельных компараторах;

- •6.3.2 Ацп поразрядного кодирования.

- •6.4 Цифро-аналоговые преобразователи (цап). Структура, основные характеристики и параметры.

- •6.4.1 Взвешенная схема, управляющая напряжением.

- •6.5 Устройство выборки хранения.

- •7.1 Общая характеристика и принципы построения глин.

- •7.2 Автоколебательные глин на транзисторах.

- •7.3 Ждущие глин на транзисторах.

- •7.4 Глин на оупт.

- •8.2 Автоколебательный блокинг-генератор.

- •8.3 Ждущий блокинг-генератор.

- •8.4 Синхронизация блокинг-генератора.

- •9.1 Оперативные запоминающие устройства (озу) с произвольным доступом.

- •9.2 Статические и динамические зу.

- •9.3 Построение плат памяти.

- •9.4 Программируемые запоминающие устройства (пзу).

- •10. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы.

- •10.2 Программируемые логические матрицы (плм).

- •10.2.1 Схемотехника плм

- •10.2.2 Подготовка задачи к решению с помощью плм

- •10.2.3 Программирование плм

- •10.2.4 Упрощенное изображение схем плм

- •10.2.5 Воспроизведение скобочных форм переключательных функций

- •10.2.6 Наращивание (расширение) плм

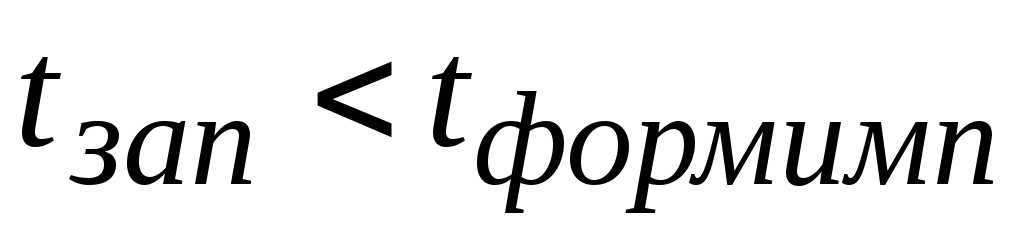

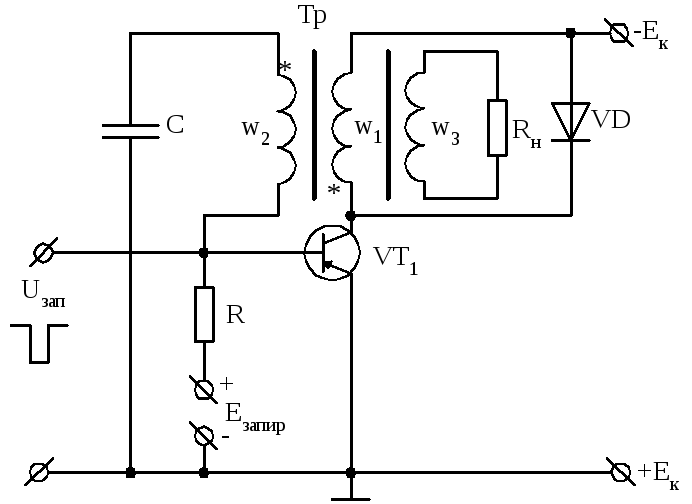

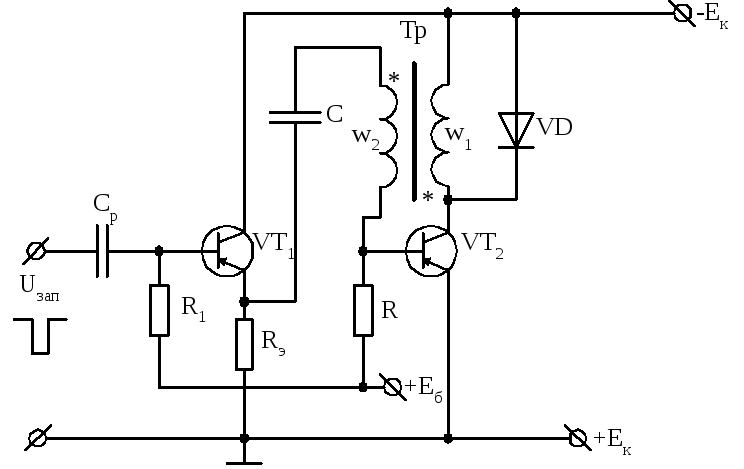

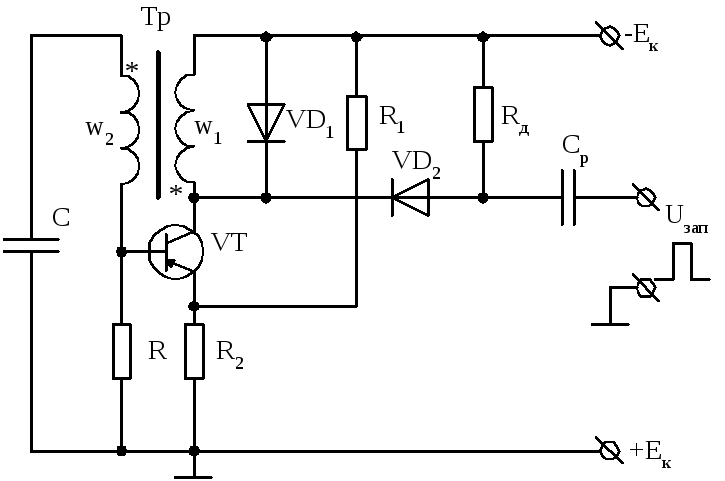

8.3 Ждущий блокинг-генератор.

Для перевода выше рассмотренной схемы блокинг-генератора в ждущий режим необходимо транзистор VT1 запереть, а для запуска подавать отпирающее напряжение на базу транзистора. На рис. 8.4.а,б приведены схемы ждущих блокинг-генераторов.

В

обеих схемах транзистор запирается

положительным напряжением

![]() и

блокинг-генератор находится в состоянии

равновесия. Времязадающий конденсатор

C

разряжен

и

блокинг-генератор находится в состоянии

равновесия. Времязадающий конденсатор

C

разряжен

![]() .

Запирание можно обеспечить с помощью

источника смещения (схема а) и делителя

напряжения (схема б). Положительное

напряжение, подаваемое на базы относительно

эмиттера должно обеспечить запирание

транзисторов. При этом напряжение

.

Запирание можно обеспечить с помощью

источника смещения (схема а) и делителя

напряжения (схема б). Положительное

напряжение, подаваемое на базы относительно

эмиттера должно обеспечить запирание

транзисторов. При этом напряжение

![]() для схемы

а):

для схемы

а):

![]() ;

;

![]() .

.

Рекомендуют

![]() .

.

Для

схемы б):![]() ;

;

![]() ;

;

Рекомендуют

![]() .

Это обеспечивается напряжением делителя

.

Это обеспечивается напряжением делителя![]() .

При таком напряжении базо-эмиттерного

перехода транзистор будет полностью

закрыт. Значение емкости конденсатора

.

При таком напряжении базо-эмиттерного

перехода транзистор будет полностью

закрыт. Значение емкости конденсатора

![]() определяется из выражения:

определяется из выражения:

![]() .

.

Параметры запускающего импульса, обеспечивающие надежное отпирание транзистора VT1, должны быть отрицательными, по модулю в 2-2,5 раза больше напряжения запирания транзисторов по длительности короче формируемых импульсов, следовательно:

;

; .

.

После прихода запускающего импульса начинается регенеративный процесс опрокидывания генератора, формируется передний фронт, крыша и задний фронт импульса в соответствии с ранее рассмотренными осциллограммами. После этого схема переходит в ждущий режим. Существуют два способа запуска заторможенных блокинг-генератора (см. рис. 8.5. а,б): а) последовательный; б) параллельный.

а)

б)

Рис. 8.4. Схемы запуска ждущего блокинг-генератор

При последовательном способе запуска запускающий импульс включается последовательно в цепь базы транзистора. При этом источник запускающих импульсов должен иметь низкое внутренне сопротивление. Поэтому схема дополнена эмиттерным повторителем на транзисторе VT1, который имеет низкое выходное сопротивление и включен в цепь базы транзистораVT2. Если источник запускающих импульсов имеет высокое внутреннее сопротивление, применяют схему параллельного запуска.

а) последовательный запуск

б) параллельный запуск

Рис. 8.5. Схемы последовательного и параллельного запуска блокинг-генератора

Запускающий импульс должен открыть

транзистор и вывести его из отсечки в

активную область, поэтому напряжение

на коллекторе должно получить положительное

приращение порядка (1-2)В следовательно,

рекомендуют

![]()

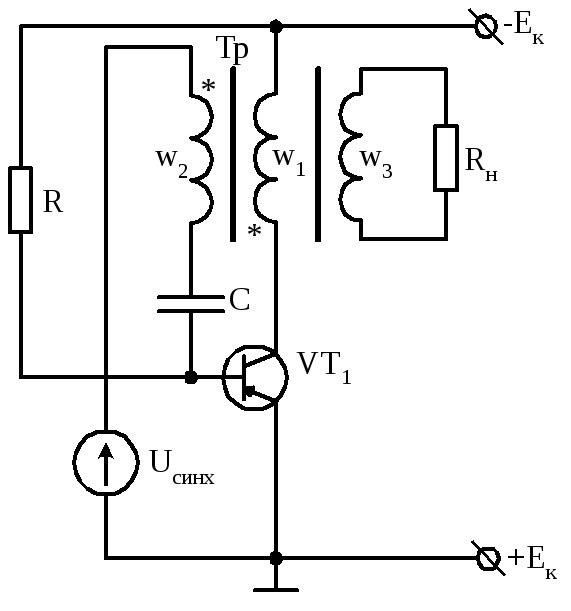

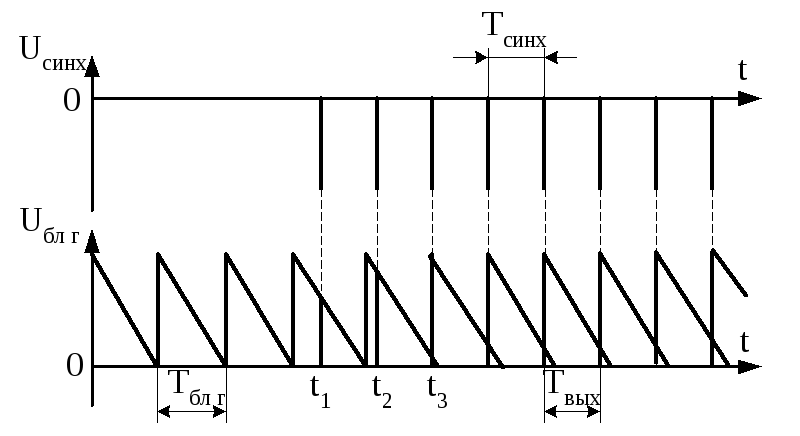

8.4 Синхронизация блокинг-генератора.

Режим синхронизации блокинг-генератора заключается в генерации выходных импульсов с частотой синхронизации, которая задается внешним высокостабильным генератором. Для этого в базу транзистора VT1 подаются периодические синхроимпульсы требуемой амплитуды. Последовательность этих импульсов может иметь различную форму, однако оптимальными считают остроконечные импульсы. Частота синхронизации внешнего генератора должна быть больше частоты блокинг-генератора:

![]() .

.

Пусть на базу транзистора блокинг-генератора

в режиме синхронизации (см. рис. 8.6)

воздействует синхронизирующий импульс

![]() с

периодом следования

с

периодом следования

![]() ,

где

,

где

![]() —период собственных колебаний

блокинг-генератора (при отсутствии

синхронизирующих импульсов). В момент

включения синхронизирующего автогенератора

временное расположение синхронизирующих

импульсов относительно собственных

импульсов блокинг-генератора может

быть любым (см. рис. 8.7). Первый

синхронизирующий импульс (приt=t1),

уменьшающий напряжение

—период собственных колебаний

блокинг-генератора (при отсутствии

синхронизирующих импульсов). В момент

включения синхронизирующего автогенератора

временное расположение синхронизирующих

импульсов относительно собственных

импульсов блокинг-генератора может

быть любым (см. рис. 8.7). Первый

синхронизирующий импульс (приt=t1),

уменьшающий напряжение

![]() на базе транзистораVT1 в

период разряда времязадающего конденсатора

С, не опрокидывает блокинг-генератор,

так как при заданной амплитуде импульса

остаточное напряжение на базе больше

нуля. Поскольку

на базе транзистораVT1 в

период разряда времязадающего конденсатора

С, не опрокидывает блокинг-генератор,

так как при заданной амплитуде импульса

остаточное напряжение на базе больше

нуля. Поскольку

![]() ,

то в каждый следующий период импульсы

синхронизации смещаются относительно

моментов отпирания транзистораVT1,

пока один из импульсов (в данном случае

третий импульс (приt=t3))

не вызовет преждевременного отпирания

транзистораVT1, а

следовательно, принудительного развития

процесса опрокидывания блокинг-генератора.

Последующие синхронизирующие импульсы

будут вызывать опрокидывание блокинг

генератора каждый раз раньше, чем

произойдет разряд времязадающего

конденсатора С через резисторR.

В схеме устанавливается стационарный

режим, при котором период повторения

,

то в каждый следующий период импульсы

синхронизации смещаются относительно

моментов отпирания транзистораVT1,

пока один из импульсов (в данном случае

третий импульс (приt=t3))

не вызовет преждевременного отпирания

транзистораVT1, а

следовательно, принудительного развития

процесса опрокидывания блокинг-генератора.

Последующие синхронизирующие импульсы

будут вызывать опрокидывание блокинг

генератора каждый раз раньше, чем

произойдет разряд времязадающего

конденсатора С через резисторR.

В схеме устанавливается стационарный

режим, при котором период повторения

![]() выходных

импульсов блокинг генератора в режиме

синхронизации равен периоду повторения

синхронизирующих импульсов.

выходных

импульсов блокинг генератора в режиме

синхронизации равен периоду повторения

синхронизирующих импульсов.

Рис. 8.6. Схема синхронизированного блокинг-генератора.

Рис. 8.7. Осциллограммы работы синхронизированного блокинг-генератора

Если частота синхронизирующих импульсов

![]() ,

гдеn— заданное целое

число, называемое коэффициентом деления

частоты, то блокинг-генератор работает

в режиме деления частоты, т.е. в режиме

захватывания внешним синхронизирующим

напряжением. В случае, например,n=3,

принудительное опрокидывание

блокинг-генератора происходит при

воздействии каждого третьего

синхронизирующего импульса. Из рис. 8.7

видно, что кратность деления частоты

существенно зависит от амплитуды

,

гдеn— заданное целое

число, называемое коэффициентом деления

частоты, то блокинг-генератор работает

в режиме деления частоты, т.е. в режиме

захватывания внешним синхронизирующим

напряжением. В случае, например,n=3,

принудительное опрокидывание

блокинг-генератора происходит при

воздействии каждого третьего

синхронизирующего импульса. Из рис. 8.7

видно, что кратность деления частоты

существенно зависит от амплитуды

![]() синхронизирующих

импульсов. Задавая различные значения

параметров

синхронизирующих

импульсов. Задавая различные значения

параметров

![]() ,

,

![]() ,

,

![]() ,

можно получить любой режим деления

частоты.

,

можно получить любой режим деления

частоты.

9. ПАМЯТЬ МП СИСТЕМ И ЭВМ.