Добавил:

Upload

Опубликованный материал нарушает ваши авторские права? Сообщите нам.

Вуз:

Предмет:

Файл:

X

- •TABLE OF CONTENTS

- •GENERAL DESCRIPTION

- •Portable Low Power Architecture

- •System Integration

- •ADSP-BF535 Peripherals

- •Processor Core

- •Figure 1. Processor Core

- •Memory Architecture

- •Figure 2. Internal/External Memory Map

- •Internal (On-Chip) Memory

- •External (Off-Chip) Memory

- •I/O Memory Space

- •Booting

- •Event Handling

- •Core Event Controller (CEC)

- •System Interrupt Controller (SIC)

- •Event Control

- •DMA Controllers

- •External Memory Control

- •PC133 SDRAM Controller

- •Asynchronous Controller

- •PCI Interface

- •PCI Host Function

- •PCI Target Function

- •USB Device

- •Real-Time Clock

- •Figure 3. External Components for RTC

- •Watchdog Timer

- •Timers

- •Serial Ports (Sports)

- •Serial Peripheral Interface (SPI) Ports

- •Figure 4. SPI Clock Rate Calculation

- •UART Port

- •Figure 5. UART Clock Rate Calculation

- •Programmable Flags (PFX)

- •Dynamic Power Management

- •Mode Transitions

- •Figure 6. Mode Transitions

- •Power Savings

- •Peripheral Power Control

- •Clock Signals

- •Figure 7. Clock Ratio Example

- •Booting Modes

- •Instruction Set Description

- •Development Tools

- •EZ-KIT Lite™ for ADSP-BF535 Blackfin Processor

- •Designing an Emulator Compatible Processor Board (Target)

- •Additional Information

- •PIN DESCRIPTIONS

- •Unused Pins

- •SPECIFICATIONS

- •Recommended Operating Conditions

- •ABSOLUTE MAXIMUM RATINGS

- •ESD SENSITIVITY

- •TIMING SPECIFICATIONS

- •Clock and Reset Timing

- •Figure 8. Clock and Reset Timing

- •Programmable Flags Cycle Timing

- •Figure 9. Programmable Flags Cycle Timing

- •Timer PWM_OUT Cycle Timing

- •Figure 10. Timer PWM_OUT Cycle Timing

- •Asynchronous Memory Write Cycle Timing

- •Figure 11. Asynchronous Memory Write Cycle Timing

- •Asynchronous Memory Read Cycle Timing

- •Figure 12. Asynchronous Memory Read Cycle Timing

- •SDRAM Interface Timing

- •Figure 13. SDRAM Interface Timing

- •Serial Ports

- •Figure 14. Serial Ports

- •Serial Peripheral Interface (SPI) Port —Master Timing

- •Figure 15. Serial Peripheral Interface (SPI) Port—Master Timing

- •Serial Peripheral Interface (SPI) Port —Slave Timing

- •Figure 16. Serial Peripheral Interface (SPI) Port—Slave Timing

- •Universal Asynchronous Receiver-Transmitter (UART) Port—Receive and Transmit Timing

- •Figure 17. UART Port—Receive and Transmit Timing

- •JTAG Test and Emulation Port Timing

- •Figure 18. JTAG Port Timing

- •Output Drive Currents

- •Figure 19. Output Drive Current

- •Figure 20. PCI 33 MHz Output Drive Current

- •Figure 21. PCI_REQ Output Drive Current

- •Power Dissipation

- •Test Conditions

- •Output Enable Time

- •Output Disable Time

- •Example System Hold Time Calculation

- •Figure 22. Output Enable/Disable

- •Figure 23. Equivalent Device Loading for AC Measurements (Includes All Fixtures)

- •Figure 24. Voltage Reference Levels for AC Measurements (Except Output Enable/Disable)

- •Environmental Conditions

- •260-Ball PBGA Pinout

- •Figure 25. 260-Ball Metric PBGA Pin Configuration (Top View)

- •Figure 26. 260-Ball Metric PBGA Pin Configuration (Bottom View)

- •OUTLINE DIMENSIONS

- •Figure 27. 260-Ball Metric Plastic Ball Grid Array (PBGA) (B-260)

- •ORDERING GUIDE

- •Revision History

ADSP-BF535

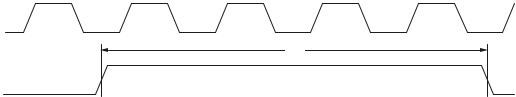

Timer PWM_OUT Cycle Timing

Table 13 and Figure 10 describe timer expired operations. The input signal is asynchronous in “width capture mode” and has an absolute maximum input frequency of fSCLK 2.

Table 13. Timer PWM_OUT Cycle Timing

Parameter |

|

Min |

Max |

Unit |

|

|

|

|

|

Switching Characteristics |

|

|

|

|

tHTO |

Timer Pulse Width Output1 |

7.5 |

(232–1) cycles |

ns |

1 The minimum time for tHTO is one cycle, and the maximum time for tHTO equals (232–1) cycles.

SCLK

tHTO

PWM_OUT

Figure 10. Timer PWM_OUT Cycle Timing

–26– |

REV. A |

Соседние файлы в папке MAZ-DOD-MAT-2012