- •Key Features

- •Key Benefits

- •Table Of Contents

- •Revision History

- •General Description

- •Dual Compute Blocks

- •Data Alignment Buffer (DAB)

- •Program Sequencer

- •Interrupt Controller

- •Flexible Instruction Set

- •DSP Memory

- •Host Interface

- •Multiprocessor Interface

- •SDRAM Controller

- •EPROM Interface

- •DMA Controller

- •Link Ports (LVDS)

- •Timer and General-Purpose I/O

- •Reset and Booting

- •Clock Domains

- •Power Domains

- •Filtering Reference Voltage and Clocks

- •Development Tools

- •Evaluation Kit

- •Additional Information

- •Pin Function Descriptions

- •Strap Pin Function Descriptions

- •ADSP-TS201S—Specifications

- •Recommended Operating Conditions

- •Electrical Characteristics

- •Absolute Maximum Ratings

- •ESD Sensitivity

- •Timing Specifications

- •General AC Timing

- •Link Port—Data Out Timing

- •Link Port—Data In Timing

- •Output Drive Currents

- •Test Conditions

- •Output Disable Time

- •Output Enable Time

- •Capacitive Loading

- •Environmental Conditions

- •Thermal Characteristics

- •576-Ball BGA_ED Pin Configurations

- •Outline Dimensions

- •Ordering Guide

a |

TigerSHARC® |

Embedded Processor |

|

|

|

|

ADSP-TS201S |

|

|

KEY FEATURES |

KEY BENEFITS |

Up to 600 MHz, 1.67 ns instruction cycle rate 24M bits of internal—on-chip—DRAM memory

25 mm × 25 mm (576-ball) thermally enhanced ball grid array package

Dual-computation blocks—each containing an ALU, a multiplier, a shifter, a register file, and a communications logic unit (CLU)

Dual-integer ALUs, providing data addressing and pointer manipulation

Integrated I/O includes 14-channel DMA controller, external port, four link ports, SDRAM controller, programmable flag pins, two timers, and timer expired pin for system integration

1149.1 IEEE compliant JTAG test access port for on-chip emulation

On-chip arbitration for glueless multiprocessing

Provides high-performance Static Superscalar DSP operations, optimized for telecommunications infrastructure and other large, demanding multiprocessor DSP applications

Performs exceptionally well on DSP algorithm and I/O benchmarks (see benchmarks in Table 1)

Supports low overhead DMA transfers between internal memory, external memory, memory-mapped peripherals, link ports, host processors, and other

(multiprocessor) DSPs

Eases DSP programming through extremely flexible instruction set and high-level-language friendly DSP architecture Enables scalable multiprocessing systems with low commu-

nications overhead

DATA ADDRESS GENERATION |

|

24M BITS INTERNAL MEMORY |

SOC BUS |

JTAG PORT |

||||||||||

|

|

32 |

32 |

|

|

|

|

|

|

|

|

6 |

|

|

INTEGER |

|

INTEGER |

|

MEMORY BLOCKS |

|

|

|

JTAG |

|

|||||

J ALU |

|

|

|

K ALU |

|

(PAGE CACHE) |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

32 × 32 |

|

32 × 32 |

|

|

4xCROSSBAR CONNECT |

|

EXTERNAL |

|||||||

PROGRAM |

|

|

|

|

|

|

|

PORT |

|

||||||||

SEQUENCER |

|

|

|

|

|

|

|

|

A D A |

D A |

D |

A D |

|

|

|

32 |

|

ADDR |

J-BUS ADDR |

|

|

|

|

|

32 |

|

|

HOST |

ADDR |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

64 |

|

|

FETCH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MULTI- |

DATA |

|

|

J-BUS DATA |

|

|

|

|

|

128 |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

PROC |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SDRAM |

8 |

CTRL |

|

K-BUS ADDR |

|

|

|

|

|

32 |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

CTRL |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BTB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C-BUS |

10 |

CTRL |

K-BUS DATA |

|

|

|

|

|

128 |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

ARB |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I-BUS ADDR |

|

|

|

|

|

32 |

|

|

|

|

SOC |

|

EXT DMA |

|||

|

|

|

|

|

|

|

|

|

|

I/F |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

128 |

|

|

|

|

|

|

REQ |

4 |

|

PC |

I-BUS DATA |

|

|

|

|

|

|

|

|

|

|

DMA |

|

|

|||

|

|

|

|

|

|

|

|

|

S-BUS ADDR |

|

21 |

|

LINK PORTS |

||||

|

T |

|

|

|

|

|

4 |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IN |

8 |

|

|

|

|

|

|

|

|

|

|

S-BUS DATA |

128 |

|

|

L0 |

4 |

|

||

IAB |

|

|

|

|

|

|

|

|

|

|

OUT |

8 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IN |

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L1 |

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OUT |

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IN |

8 |

|

|

|

|

|

|

|

128 |

|

128 |

|

|

|

|

|

|

L2 |

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OUT |

8 |

|

||

|

|

|

|

|

X |

|

|

|

Y |

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IN |

8 |

|

||

|

|

|

|

REGISTER |

128 |

|

128 |

REGISTER |

|

|

|

|

|

|

|||

CLU |

SHIFT |

ALU |

MUL |

|

MUL |

ALU |

SHIFT |

CLU |

L3 |

4 |

|

||||||

|

FILE |

DAB |

DAB |

|

FILE |

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

OUT |

8 |

|

||||

|

|

|

|

|

32 × 32 |

|

|

|

32 × 32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

COMPUTATIONAL BLOCKS |

|

|

|

|

|

|

|

|

|

||

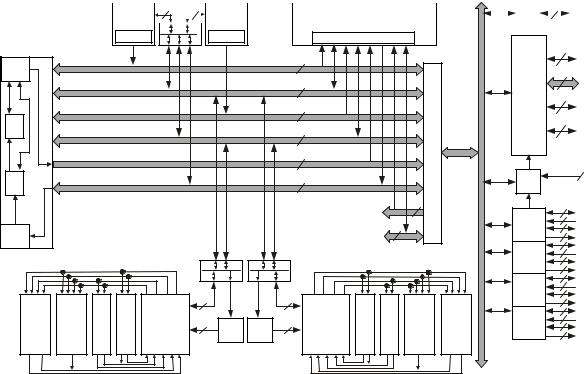

Figure 1. Functional Block Diagram

TigerSHARC and the TigerSHARC logo are registered trademarks of Analog Devices, Inc.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703 © 2004 Analog Devices, Inc. All rights reserved.

ADSP-TS201S

TABLE OF CONTENTS |

|

General Description ................................................. |

3 |

Dual Compute Blocks ............................................ |

4 |

Data Alignment Buffer (DAB) .................................. |

4 |

Dual Integer ALU (IALU) ....................................... |

4 |

Program Sequencer ............................................... |

5 |

Interrupt Controller ........................................... |

5 |

Flexible Instruction Set ........................................ |

5 |

DSP Memory ....................................................... |

5 |

External Port |

|

(Off-Chip Memory/Peripherals Interface) ................ |

6 |

Host Interface ................................................... |

6 |

Multiprocessor Interface ...................................... |

7 |

SDRAM Controller ............................................ |

7 |

EPROM Interface .............................................. |

7 |

DMA Controller ................................................... |

7 |

Link Ports (LVDS) ................................................ |

8 |

Timer and General-Purpose I/O ............................... |

9 |

Reset and Booting ................................................. |

9 |

Clock Domains .................................................... |

9 |

Power Domains .................................................... |

9 |

Filtering Reference Voltage and Clocks .................... |

10 |

Development Tools ............................................. |

10 |

Evaluation Kit .................................................... |

11 |

Designing an Emulator-Compatible |

|

DSP Board (Target) .......................................... |

11 |

Additional Information ........................................ |

11 |

Pin Function Descriptions ....................................... |

12 |

Strap Pin Function Descriptions ................................ |

20 |

ADSP-TS201S—Specifications .................................. |

21 |

Recommended Operating Conditions ...................... |

21 |

Electrical Characteristics ....................................... |

22 |

Absolute Maximum Ratings .................................. |

23 |

ESD Sensitivity ................................................... |

23 |

Timing Specifications .......................................... |

24 |

General AC Timing .......................................... |

24 |

Link Port Low-Voltage, Differential-Signal (LVDS) |

|

Electrical Characteristics and Timing ................. |

30 |

Link Port—Data Out Timing ........................... |

31 |

Link Port—Data In Timing ............................. |

34 |

Output Drive Currents ......................................... |

35 |

Test Conditions .................................................. |

36 |

Output Disable Time ......................................... |

36 |

Output Enable Time ......................................... |

37 |

Capacitive Loading ........................................... |

37 |

Environmental Conditions .................................... |

39 |

Thermal Characteristics ..................................... |

39 |

576-Ball BGA_ED Pin Configurations ......................... |

40 |

Outline Dimensions ................................................ |

44 |

Ordering Guide ..................................................... |

44 |

REVISION HISTORY

11/04—Rev. PrH to Rev. 0: Initial (Production) Version

Applies corrections and additional information (including more |

|

detail on differences between 500 MHz and 600 MHz parts) to: |

|

SCLK_VREF Filtering Scheme ................................ |

10 |

Pin Definitions—Link Ports ................................... |

18 |

Pin Definitions—Impedance Control, Drive Strength Con- |

|

trol, and Regulator Enable .................................. |

18 |

Recommended Operating Conditions ...................... |

21 |

Electrical Characteristics ....................................... |

22 |

Power-Up Timing ............................................... |

26 |

AC Signal Specifications ........................................ |

28 |

Ordering Guide .................................................. |

44 |

Provides a usable jitter specification in: |

|

Reference Clocks—System Clock (SCLK) Cycle Time .. |

25 |

Provides thermal information for wider temperature range in: |

|

Thermal Characteristics for 25 mm × 25 mm Package .. |

39 |

Rev. 0 | Page 2 of 44 | November 2004