- •Contents

- •Preface

- •Related Documents

- •Typographic and Syntax Conventions

- •Creating HDL Modules for CDBA Cellviews

- •Creating HDL Data as You Save CDBA Cellviews

- •Creating HDL Data from Pre-existing CDBA Cellviews

- •Quick-Start Tutorial

- •The Circuit

- •AMS Designer Tools

- •Setting Up the Tutorial

- •Running from a Script

- •Running within the AMS Environment

- •Opening the Command Interpreter Window

- •Netlisting and Compiling

- •Elaborating and Simulating the Design

- •Summary

- •Setting Up the AMS Environment

- •Overview

- •The hdl.var File

- •The ams.env Files

- •AMS Designer Supports Design Management

- •Specifying the Text Editor to Use

- •Specifying Fonts for the Cadence Hierarchy Editor

- •Preparing to Use AMS Designer from the Hierarchy Editor

- •Netlisting

- •Netlisting Modes Supported by the AMS Netlister

- •Automatic Netlisting of a Cellview

- •Netlist Updating and Netlisting of Entire Designs

- •Netlisting from the UNIX Command Line

- •Library Netlisting

- •Netlisting of Cells in Response to Changes in CDF

- •Preparing Existing Analog Primitive Libraries for Netlisting

- •Specifying the Behavior of the Netlister and Compilers

- •Opening the AMS Options Windows

- •Setting Netlister Options from the Hierarchy Editor

- •Opening the CIW AMS Options Window

- •Setting Compiler Options

- •Viewing the AMS Netlister Log

- •Understanding the Output from the AMS Netlister

- •How Inherited Connections Are Netlisted

- •Inherited Signal Connections

- •Inherited Terminal Connections

- •Instance Values for Inherited Connections

- •Third-Party Tools and Other Cadence Tools

- •How Aliased Signals Are Netlisted

- •How m-factors (Multiplicity Factors) Are Netlisted

- •How Iterated Instances Are Netlisted

- •Passing Model Names as Parameters

- •Effect of the modelname, model, and modelName Parameters

- •Handling of the model* and componentName Parameters

- •Precedence of the model* and componentName Parameters

- •Specifying Parameters to be Excluded from Netlisting

- •Ignoring Parameters for Entire Libraries

- •Example: Specifying Parameters to Ignore

- •Ensuring that Floating Point Parameters Netlist Correctly

- •Working with Schematic Designs

- •Setting Schematic Rules Checker Options for AMS Designer

- •Creating Cellviews Using the AMS Environment

- •Preparing a Library

- •Creating the Symbol View

- •Using Blocks

- •Descend Edit

- •Inherited Connections

- •Global Signals in the Schematic Editor

- •Inherited Connections in a Hierarchy

- •How Net Expressions Evaluate

- •Net and Pin Properties

- •groundSensitivity and supplySensitivity Properties

- •Making Connect Modules Sensitive to Inherited Connection Values

- •Using External Text Designs

- •Overview of Steps for Using External Text Designs

- •Bringing Modules into a Cadence Library

- •Specifying the Working Library

- •Compiling into Libraries

- •Compiling into Temporary Libraries

- •Listing Compiled Modules

- •Using Text Blocks in Schematics

- •Using Modules Located in a Cadence Library

- •Preparing for Simulation

- •Using Analog Primitives

- •Using SPICE and Spectre Netlists and Subcircuits

- •Preparing to Use SPICE and Spectre Netlists and Subcircuits

- •Placing SPICE and Spectre Netlists and Subcircuits in a Schematic

- •Using Test Fixtures

- •Creating and Using a Textual Test Fixture

- •Creating a Textual Test Fixture

- •Using a Test Fixture

- •Example: Creating and Using a Test Fixture

- •Using Design Configurations

- •Ensuring HDL Design Unit Information Is Current

- •Preparing a Design for Simulation

- •Overview of AMS Design Prep

- •What AMS Design Prep Does to Prepare a Design for Simulation

- •When to Use AMS Design Prep

- •Specifying the Behavior of AMS Design Prep

- •Setting Options for Global Design Data

- •Specifying Global Signals

- •Specifying Design Variables

- •Specifying Model Files to Use During Elaboration

- •Running AMS Design Prep

- •The cds_globals Module

- •Global Signals

- •Design Variables

- •Setting Elaborator Options

- •Setting Simulator Options

- •Setting Waveform Selection Options

- •Creating Probes

- •Selecting Instances from the Virtuoso Schematic Editing Window

- •Selecting Buses

- •Selecting Instances from the Scope Navigator

- •Copying and Pasting Within Tables

- •Elaborating and Simulating

- •Viewing Messages

- •Plotting Waveforms After Simulation Ends

- •Starting the SimVision Waveform Viewer

- •Plotting Waveforms Selected on a Schematic (Direct Plot)

- •Using the amsdesigner Command

- •Examples

- •Producing Customized Netlists

- •Producing Customized Netlists

- •Identifying the Sections of a Netlist

- •Using ams.env Variables to Customize Netlists

- •Using Netlisting Procedures to Customize Netlists

- •Examples: Problems Addressed by Customized Netlists

- •Example: Adjusting Parameter Values to Account for Number of Fingers

- •Example: Using Symbols that Represent Verilog Test Code

- •Data Objects Supported for Netlisting

- •Netlister Object

- •Formatter Object

- •Cellview Object

- •Parameter Object

- •Instance Object

- •SKILL Functions Supported for Netlisting

- •Default Netlisting Procedures

- •Netlisting Helper Functions

- •Variables for ams.env Files

- •How AMS Designer Determines the Set of Variables

- •Why AMS Designer Uses ams.env Files, Not .cdsenv Files

- •List of ams.env Variables

- •Detailed Descriptions of ams.env Variables

- •aliasInstFormat

- •allowDeviantBuses

- •allowNameCollisions

- •allowSparseBuses

- •allowUndefParams

- •amsCompMode

- •amsDefinitionViews

- •amsEligibleViewTypes

- •amsExcludeParams

- •amsExpScalingFactor

- •amsLSB_MSB

- •amsMaxErrors

- •amsScalarInstances

- •amsVerbose

- •analogControlFile

- •bindCdsAliasLib

- •bindCdsAliasView

- •cdsGlobalsLib

- •cdsGlobalsView

- •checkAndNetlist

- •checkOnly

- •checktasks

- •compileAsAMS

- •compileExcludeLibs

- •compileMode

- •connectRulesCell

- •connectRulesCell2

- •connectRulesLib

- •connectRulesView

- •detailedDisciplineRes

- •discipline

- •excludeViewNames

- •hdlVarFile

- •headerText

- •ieee1364

- •ifdefLanguageExtensions

- •incdir

- •includeFiles

- •includeInstCdfParams

- •initFile

- •instClashFormat

- •iterInstExpFormat

- •language

- •lexpragma

- •logFileAction

- •logFileName

- •macro

- •maxErrors

- •messages

- •modifyParamScope

- •ncelabAccess

- •ncelabAnnoSimtime

- •ncelabArguments

- •ncelabCoverage

- •ncelabDelayMode

- •ncelabDelayType through ncelabMessages

- •ncelabMixEsc

- •ncelabModelFilePaths

- •ncelabNeverwarn through ncelabVipdelay

- •ncsimArguments

- •ncsimEpulseNoMsg through ncsimExtassertmsg

- •ncsimGUI

- •ncsimLoadvpi through ncsimStatus

- •ncsimTcl

- •ncsimUnbuffered through ncsimUseAddArgs

- •ncvhdlArguments

- •ncvlogArguments

- •ncvlogUseAddArgs

- •netClashFormat

- •netlistAfterCdfChange

- •netlistMode

- •netlistUDFAsMacro

- •neverwarn

- •noline

- •nomempack

- •nopragmawarn

- •nostdout

- •nowarn

- •paramDefVals

- •paramGlobalDefVal

- •pragma

- •processViewNames

- •prohibitCompile

- •runNcelab

- •runNcsim

- •scaddlglblopts

- •scaddltranopts

- •scale

- •scalem

- •scannotate

- •scapprox

- •scaudit

- •sccheckstmt

- •sccmin

- •sccompatible

- •scdebug

- •scdiagnose

- •scdigits

- •scerror

- •scerrpreset

- •scfastbreak

- •scgmin

- •scgmincheck

- •schomotopy

- •sciabstol

- •scic

- •scicstmt

- •scignshorts

- •scinfo

- •scinventory

- •sclimit

- •sclteratio

- •scmacromod

- •scmaxiters

- •scmaxnotes

- •scmaxrsd

- •scmaxstep

- •scmaxwarn

- •scmethod

- •scmodelevaltype

- •scmosvres

- •scnarrate

- •scnotation

- •scnote

- •scopptcheck

- •scpivabs

- •scpivotdc

- •scpivrel

- •scquantities

- •screadic

- •screadns

- •screlref

- •screltol

- •scrforce

- •scscale

- •scscalem

- •scscftimestamp

- •scscfusefileflag

- •scskipcount

- •scskipdc

- •scskipstart

- •scskipstop

- •scspeed

- •scstats

- •scstep

- •scstop

- •scstrobedelay

- •scstrobeperiod

- •sctemp

- •sctempeffects

- •sctitle

- •sctnom

- •sctopcheck

- •sctransave

- •scusemodeleval

- •scvabstol

- •scwarn

- •scwrite

- •simRunDirLoc

- •simVisScriptFile

- •status

- •templateFile

- •templateScript

- •timescale

- •update

- •use5xForVHDL

- •useDefparam

- •useNcelabNowarn

- •useNcelabSdfCmdFile

- •useNcsimNowarn

- •useNowarn

- •useScaddlglblopts

- •useScaddltranopts

- •useScic

- •useScreadic

- •useScreadns

- •useScwrite

- •useSimVisScriptFile

- •useProcessViewNamesOnly

- •verboseUpdate

- •vlogGroundSigs

- •vloglinedebug

- •vlogSupply0Sigs

- •vlogSupply1Sigs

- •wfDefaultDatabase

- •wfDefInstCSaveAll

- •wfDefInstCSaveLvl

- •wfDefInstSaveCurrents

- •wfDefInstSaveVoltages

- •wfDefInstVSaveAll

- •wfDefInstVSaveLvl

- •wfDefInstVSaveObjects

- •Updating Legacy SimInfo for Analog Primitives

- •The ams Fields

- •Special Handling of model, modelName, modelname, and componentName

- •Converting an Existing Analog Primitive Library

- •Designing for Virtuoso AMS Compliance

- •Terminals

- •Buses

- •Component Description Format

- •Parameters

- •Using Inherited Parameters

- •Using Cell Parameters

- •Parameterized Cells

- •VHDL-AMS Component Declarations

- •Properties

- •Properties to Avoid Completely

- •Avoid the portOrder Property Unless Required by Special Circumstances

- •Properties to Use Only in AMS Compatibility Mode

- •Properties That Have No Special Meaning in the AMS Environment

- •Properties Fully Supported by the AMS Environment

- •SKILL Functions

- •amsCheckCV

- •amsIsPresent

- •amsNetlist

- •amsProcessCellViews

- •amsUIOptionsForm

- •amsUIRunNetlisterForm

- •ddsCvtAMSTranslateCell

- •ddsCvtAMSTranslateLib

- •ddsCvtToolBoxAMS

- •vmsUpdateCellViews

- •Customization Variables

- •schHdlNotCreateDB

- •schHdlUseVamsForVerilog

- •vmsAnalysisType

- •vmsCreateMissingMasters

- •vmsNcvlogExecutable

- •vmsPortProcessing

- •vmsRunningInUI

- •vmsTemplateScript

- •vmsVerboseMsgLevel

- •Compiling Cadence-Provided Libraries

- •Purpose of the amsLibCompile Tool

- •Running the amsLibCompile Tool Manually

- •Example

Virtuoso AMS Environment User Guide

Netlisting

Viewing the AMS Netlister Log

If you want to examine the log produced by the AMS netlister, choose AMS – Logfile

Viewer – Netlister Log File from the Cadence hierarchy editor menu. The log contains information about the blocks that are translated. For example, the following log describes where two netlists are written.

@(#)$CDS: amsdirect version 4.4.6 06/21/2000 19:28 (cds11607) $ Copyright (c) 1999 Cadence Design Systems. All Rights Reserved.

Run date: Thu Jun 22 15:40:42 2000 Run time options used:

-mpshost cds11752 -mpssession icms8457 -pid 8628

Info: Processing ("amslib" "top" "schematic") ...

Info: Verilog-AMS netlist successfully written to /opt/mnt4/lorenp/alpha2/alpha/AMS_lib/amsLib/top/schematic/verilog.vams.

Info: Found 0 errors and 0 warnings.

Info: Processing ("amslib" "comparator" "schematic") ...

Info: Verilog-AMS netlist successfully written to /opt/mnt4/lorenp/alpha2/

Understanding the Output from the AMS Netlister

The output of a successful netlisting run is one or more files namedverilog.vams, each containing a legal Verilog-AMS module that corresponds to a CDBA cellview. The netlister places each output file in the cellview directory.

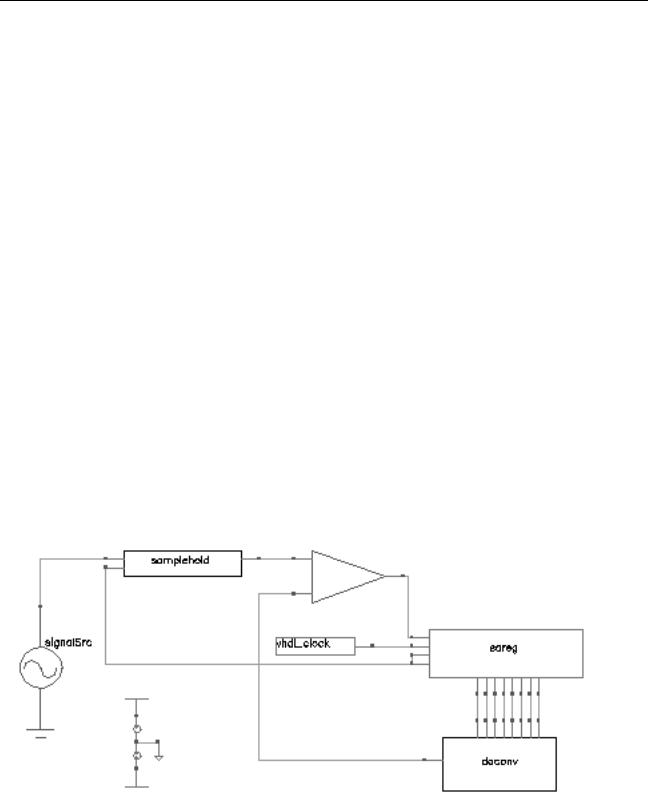

For example, consider the following schematic.

April 2004 |

126 |

Product Version 5.3 |