- •Введение

- •Общие сведения Технико-эксплуатационные характеристики эвм

- •История развития эвм

- •Классификация эвм

- •Классификация эвм по назначению

- •Классификация эвм по функциональным возможностям иразмерам

- •Функциональная и структурная организация эвм

- •Связь между функциональной и структурной организацией эвм

- •Обобщенная структура эвм и пути её развития

- •Обрабатывающая подсистема

- •Подсистема памяти

- •Подсистема ввода-вывода

- •Подсистема управления и обслуживания

- •Архитектуры эвм

- •Sisd-компьютеры

- •Компьютеры с cisc архитектурой

- •Компьютеры с risc архитектурой

- •Компьютеры с суперскалярной обработкой

- •Simd-компьютеры

- •Матричная архитектура

- •Векторно-конвейерная архитектура

- •Ммх технология

- •Misd компьютеры

- •Mimd компьютеры

- •Многопроцессорные вычислительные системы

- •Многопроцессорные вычислительные системы с общей шиной.

- •Многопроцессорные вычислительные системы с многовходовыми модулями оп.

- •Многомашинные вычислительные системы (ммвс)

- •Многомашинные комплексы

- •Ммр архитектура

- •Структура и форматы команд эвм

- •Форматы команд эвм

- •Способы адресации

- •Классификация способов адресации по наличию адресной информации в команде

- •Классификация способов адресации по кратности обращения в память

- •Классификация по способу формирования исполнительных адресов ячеек памяти

- •Относительная адресация

- •Стековая адресация

- •Теги и дескрипторы. Самоопределяемые данные

- •Процессоры. Центральный процессор

- •Логическая структура цп

- •Структурная схема процессора

- •Характеристики процессора

- •Регистровые структуры центрального процессора

- •Основные функциональные регистры

- •Регистры процессора обработки чисел с плавающей точкой

- •Системные регистры

- •Регистры отладки и тестирования

- •Назначение и Классификация цуу

- •Устройства управления цп

- •Цуу с жесткой логикой.

- •Цуу с микропрограммной логикой

- •Процедура выполнения команд

- •Язык микроопераций

- •Описание слов, регистров и шин

- •Описание массива данных и памяти.

- •Описание микроопераций

- •Условные микрооператоры.

- •Арифметико-логическое устройство

- •Структура алу

- •Сумматоры

- •Классификация алу

- •Методы повышения быстродействия алу

- •Память эвм

- •Организация внутренней памяти процессора.

- •Оперативная память и методы управления оп

- •Методы управления памятью без использования дискового пространства (без использования внешней памяти).

- •Распределение памяти фиксированными разделами.

- •Размещение памяти с перемещаемыми разделами.

- •Организация виртуальной памяти.

- •Страничное распределение.

- •Сегментное распределение.

- •Странично - сегментное распределение.

- •Свопинг

- •Методы повышения пропускной способности оп.

- •Выборка широким словом.

- •Расслоение сообщений.

- •Методы организации кэш-памяти

- •Типовая структура кэш-памяти

- •Способы размещения данных в кэш-памяти.

- •Прямое распределение.

- •Полностью ассоциативное распределение.

- •Частично ассоциативное распределение.

- •Распределение секторов.

- •Методы обновления строк в основной памяти

- •Системы внешней памяти

- •Общие принципы организации системы прерывания программ

- •Характеристики системы прерываний

- •Программно-управляемый приоритет прерывающих программ

- •Организация перехода к прерывающей программе

- •ПодСистема ввода/вывода Принципы организации подсистемы ввода/вывода

- •Каналы ввода-вывода

- •Интерфейсы ввода-вывода

- •Классификация интерфейсов

- •Типы и характеристики стандартных шин

- •Вычислительные системы

- •Общие положения

- •Классификация вс

- •Понятие открытой системы

- •Кластерные структуры

- •12. Библиографический список

- •Содержание

- •1. Общие сведения 5

- •2. Архитектуры эвм 22

- •3. Структура и форматы команд эвм 37

- •4. Типы данных 47

- •5. Процессоры. Центральный процессор 53

- •6. Язык микроопераций 72

- •7. Арифметико-логическое устройство 77

- •8. Память эвм 84

- •9. Общие принципы организации системы прерывания программ 118

- •10. ПодСистема ввода/вывода 125

- •11. Вычислительные системы 134

- •12. Библиографический список 140

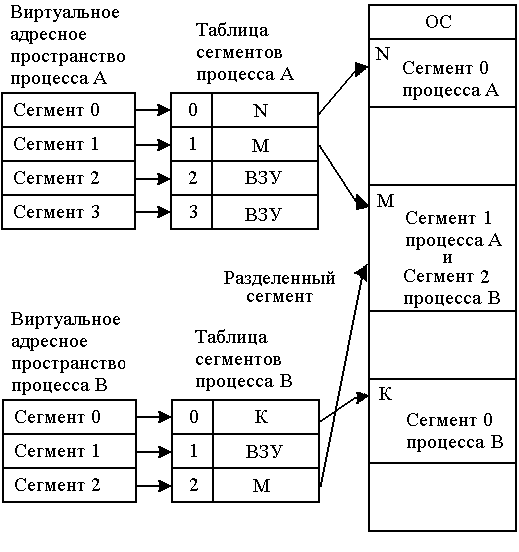

Сегментное распределение.

При страничной организации памяти ВА – пространство процесса делится на механически равные части. Это не позволяет дифференцировать способы доступа к разным частям программы (сегментам), а это свойство часто бывает полезным. Например, можно запретить обращаться с операцией записи и чтения в сегмент кода программы, а для сегмента данных разрешить только чтение. Кроме того, разбиение программы на сегменты, а не на страницы делает возможным разделение одного сегмента несколькими процессами.

Рассмотрим, каким образом сегментное распределение памяти реализует эти возможности (рис. 8.11.). Виртуальное адресное пространство процесса делится на сегменты, размер которых определяется программистом с учетом смыслового значения содержащейся в них информации. Отдельным сегментом м.б. подпрограммы, массив данных и др. Иногда сегментация программы может выполняться по умолчанию компилятором.

При загрузке процесса одни сегменты записываются в ОП, другие остаются на диске. Сегменты одной программы могут занимать несмежные участки ОП. Во время загрузки ОС создает для процесса таблицу сегментов (аналогичную таблице страниц), в которой для любого сегмента указывается начальный физический адрес сегмента в ОП, размер, правила доступа, признак модификации, признак обращения к данному сегменту за последний интервал времени и некоторая другая информация. Если ВАП нескольких процессов включают один и тот же сегмент, то в таблицах сегментов этих процессов делаются ссылки на один и тот же участок ОП, в который этот сегмент загружается в единственном экземпляре.

Рис.8.11. Распределение памяти сегментами

Система с сегментной организацией функционирует аналогично системе со страничной организацией.

При каждом обращении к ОП из таблицы сегментов считывается информация о сегменте, к которому производится обращение.

Если сегмент находится в ОП, то осуществляется преобразование виртуального адреса в физический. Если же сегмент находится на диске, то возникает случай страничного прерывания; процесс переводится в состояние ожидания, и активизируется другой процесс. Аналогичным образом при необходимости освобождения ОП некоторые сегменты выгружаются. Вместе с тем, при обращении к памяти проверяется, разрешен ли доступ требуемого типа к данному сегменту.

Виртуальный при сегментной организации представлен парой чисел (g, s), где первое – номер сегмента, второе – смещение внутри сегмента.

ФА получается путем сложения начального ФА сегмента, найденного в таблице сегментов по номеру g, и смещения s. Операция сложения является более медленной, что в целом оказывает отрицательное влияние на быстродействие машины. Еще одним недостатком сегментной организации также является фрагментация на уровне сегментов.

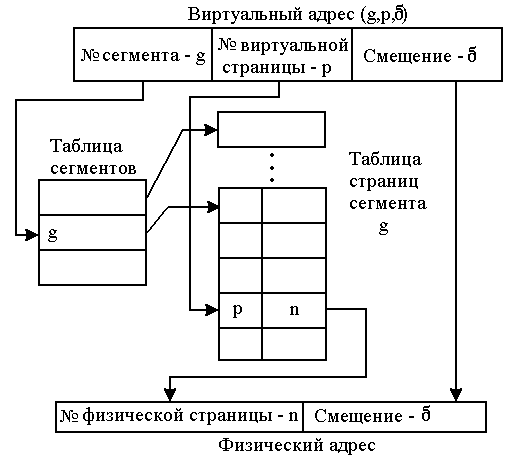

Странично - сегментное распределение.

Данный метод сочетает в себе достоинства обоих подходов, представляя собой их комбинацию. Всё виртуальное адресное пространство процесса делится на сегменты, а каждый сегмент – на страницы. ОП при этом делится на физические страницы. Загрузка процесса в ОП осуществляется постранично. ОС при загрузке процесса создает таблицу сегментов (TS) процесса. Для каждого сегмента создается своя таблица страниц (TP), структура которой полностью аналогична структуре таблицы страниц при страничном распределении. Адрес таблицы сегментов загружается в специальный регистр процессора, когда активизируется соответствующий процесс. В таблице страниц находятся адреса таблиц страниц для всех сегментов данного процесса. По схеме, приведенной на рисунке 8.12, виртуальный адрес преобразуется в физический.

Рис.8.12. Схема преобразования виртуального адреса в физический

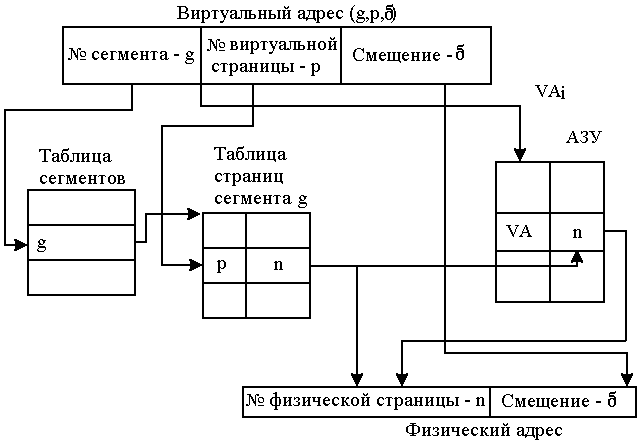

Процесс подобного преобразования является достаточно длительным. Чтобы его ускорить и тем самым повысить производительность ЭВМ, применяют быстродействующие ассоциативные ЗУ, т.е. устройства, в которых применяется принцип ассоциативности.

Если в системе реализовано такое устройство, то преобразование ВА в ФА осуществляется по такому принципу, называемому динамическим преобразованием адресов (см. рис. 8.13): ВА, представленный парой чисел (g,p) передается в качестве поискового признака в АЗУ, т.о. VAi первый появляется в ячейке А буфера. Вторым полем ячейки является ФА страницы в ОП. При обнаружении совпадения VAi с содержимым памяти из соответствующей ячейки Асс. Буфера, извлекается соответствующий ФА страницы, позволяющий сформировать полный ФА элемента данных в ОП. Если же VAi не совпадает ни с одной ячейкой АЗУ, то преобразование осуществляется обычным способом через таблицы сегментов и страниц. Эффективность применения динамического преобразования адресов определяется тем, насколько редко используются табличные преобразования. Как правило, при первом обращении к странице, расположенной в ОП, ФА определяется с помощью таблиц и загружается в соответствующую ячейку АЗУ, с тем чтобы последующие обращения к странице могли выполняться с использованием АЗУ.

Рис. 8.13. Механизм динамического преобразования адресов