- •Введение

- •Общие сведения Технико-эксплуатационные характеристики эвм

- •История развития эвм

- •Классификация эвм

- •Классификация эвм по назначению

- •Классификация эвм по функциональным возможностям иразмерам

- •Функциональная и структурная организация эвм

- •Связь между функциональной и структурной организацией эвм

- •Обобщенная структура эвм и пути её развития

- •Обрабатывающая подсистема

- •Подсистема памяти

- •Подсистема ввода-вывода

- •Подсистема управления и обслуживания

- •Архитектуры эвм

- •Sisd-компьютеры

- •Компьютеры с cisc архитектурой

- •Компьютеры с risc архитектурой

- •Компьютеры с суперскалярной обработкой

- •Simd-компьютеры

- •Матричная архитектура

- •Векторно-конвейерная архитектура

- •Ммх технология

- •Misd компьютеры

- •Mimd компьютеры

- •Многопроцессорные вычислительные системы

- •Многопроцессорные вычислительные системы с общей шиной.

- •Многопроцессорные вычислительные системы с многовходовыми модулями оп.

- •Многомашинные вычислительные системы (ммвс)

- •Многомашинные комплексы

- •Ммр архитектура

- •Структура и форматы команд эвм

- •Форматы команд эвм

- •Способы адресации

- •Классификация способов адресации по наличию адресной информации в команде

- •Классификация способов адресации по кратности обращения в память

- •Классификация по способу формирования исполнительных адресов ячеек памяти

- •Относительная адресация

- •Стековая адресация

- •Теги и дескрипторы. Самоопределяемые данные

- •Процессоры. Центральный процессор

- •Логическая структура цп

- •Структурная схема процессора

- •Характеристики процессора

- •Регистровые структуры центрального процессора

- •Основные функциональные регистры

- •Регистры процессора обработки чисел с плавающей точкой

- •Системные регистры

- •Регистры отладки и тестирования

- •Назначение и Классификация цуу

- •Устройства управления цп

- •Цуу с жесткой логикой.

- •Цуу с микропрограммной логикой

- •Процедура выполнения команд

- •Язык микроопераций

- •Описание слов, регистров и шин

- •Описание массива данных и памяти.

- •Описание микроопераций

- •Условные микрооператоры.

- •Арифметико-логическое устройство

- •Структура алу

- •Сумматоры

- •Классификация алу

- •Методы повышения быстродействия алу

- •Память эвм

- •Организация внутренней памяти процессора.

- •Оперативная память и методы управления оп

- •Методы управления памятью без использования дискового пространства (без использования внешней памяти).

- •Распределение памяти фиксированными разделами.

- •Размещение памяти с перемещаемыми разделами.

- •Организация виртуальной памяти.

- •Страничное распределение.

- •Сегментное распределение.

- •Странично - сегментное распределение.

- •Свопинг

- •Методы повышения пропускной способности оп.

- •Выборка широким словом.

- •Расслоение сообщений.

- •Методы организации кэш-памяти

- •Типовая структура кэш-памяти

- •Способы размещения данных в кэш-памяти.

- •Прямое распределение.

- •Полностью ассоциативное распределение.

- •Частично ассоциативное распределение.

- •Распределение секторов.

- •Методы обновления строк в основной памяти

- •Системы внешней памяти

- •Общие принципы организации системы прерывания программ

- •Характеристики системы прерываний

- •Программно-управляемый приоритет прерывающих программ

- •Организация перехода к прерывающей программе

- •ПодСистема ввода/вывода Принципы организации подсистемы ввода/вывода

- •Каналы ввода-вывода

- •Интерфейсы ввода-вывода

- •Классификация интерфейсов

- •Типы и характеристики стандартных шин

- •Вычислительные системы

- •Общие положения

- •Классификация вс

- •Понятие открытой системы

- •Кластерные структуры

- •12. Библиографический список

- •Содержание

- •1. Общие сведения 5

- •2. Архитектуры эвм 22

- •3. Структура и форматы команд эвм 37

- •4. Типы данных 47

- •5. Процессоры. Центральный процессор 53

- •6. Язык микроопераций 72

- •7. Арифметико-логическое устройство 77

- •8. Память эвм 84

- •9. Общие принципы организации системы прерывания программ 118

- •10. ПодСистема ввода/вывода 125

- •11. Вычислительные системы 134

- •12. Библиографический список 140

Классификация по способу формирования исполнительных адресов ячеек памяти

Способы формирования адресов ячеек памяти (Аи) можно разделить на абсолютные и относительные.

Абсолютные способы формированияпредполагают, что двоичный код адреса ячейки памяти - Аиможет быть извлечен целиком либо из адресного поля команды (в случае прямой адресации), или из какой-либо другой ячейки (в случае косвенной адресации), никаких преобразований кода адреса не производится.

Относительные способы формированияАипредполагают, что двоичный код адреса ячейки памяти образуется из нескольких составляющих: Б - код базы, И - код индекса, С - код смещения, используемых в сочетаниях (Б и С), (И и С), (Б, И и С). При относительной адресации применяются два способа вычисления адреса Аи:

суммирование кодов составляющих адреса

(Аи= Б + С; Аи- И + С; Аи= Б + И + С);

совмещение (конкатенация) кодов составляющих адреса

(например Аи= Б/С).

Относительная адресация

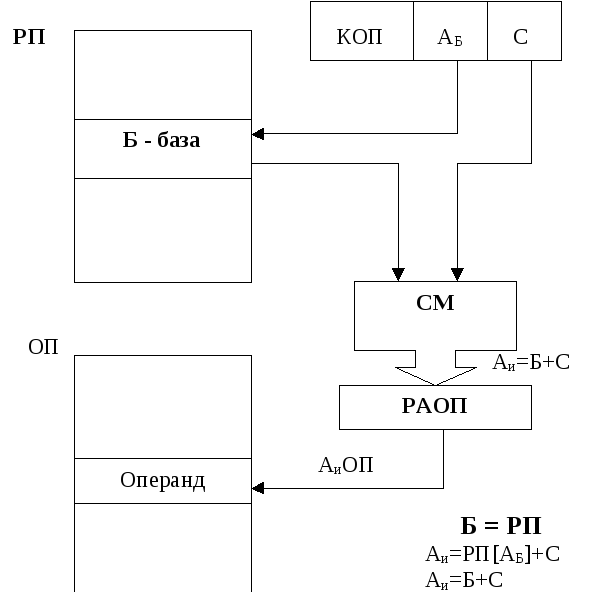

Базирование способом суммирования. В команде адресный код Акразделяется на две составляющие: Аб- адрес регистра в регистровой памяти , в котором хранится база Б (базовый адрес); С - код смещения относительно базового адреса (рис. 3.5).

С помощью метода относительной адресации удается получить так называемый перемещаемый программный модуль, который одинаково выполняется процессором независимо от адресов, в которых он расположен. Начальный адрес программного модуля (база) загружается, при входе в модуль, в базовый регистр. Все остальные адреса программного модуля формируются через смещение относительно начального адреса (базы) модуля. Таким образом, одна и та же программа может работать с данными, расположенными в любой области памяти, без перемещения данных и без изменения текста программы только за счет изменения содержания всего одного базового регистра. Однако время выполнения каждой операции при этом возрастает.

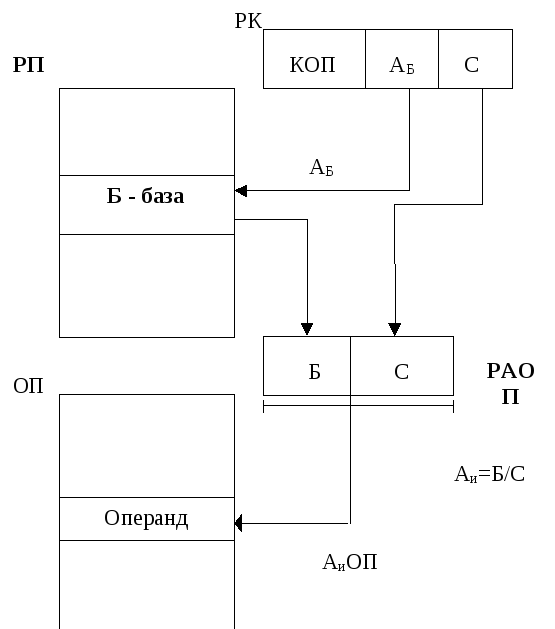

Базирование способом совмещения составляющих. Для увеличения емкости адресной ОП без увеличения длины адресного поля команды можно использовать для формирования исполнительного адреса совмещение (конкатенацию) кодов базы и смещения (рис. 3.6).

Рис. 3.5 Схема формирования относительного адреса способом суммирования кодов базы и смещения.

СМ – сумматор,

РАОП – регистр адреса ОП,

Б – база (базовый адрес),

С – смещение,

Аб – адрес регистра базы

Однако в данном случае начальныеадреса массивов не могут быть реализованы произвольно, а должны иметь в младших разрядахnнулей, гдеn– длина поля смещения.

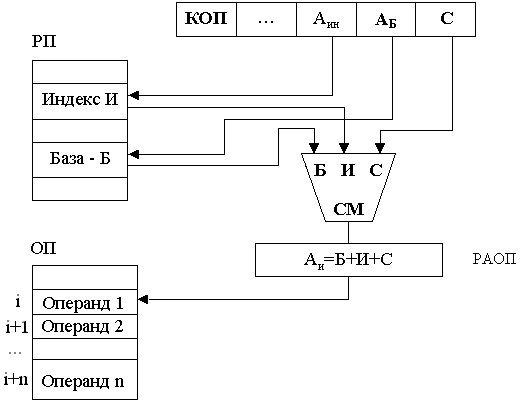

Индексная адресация. Для работы программ с массивами, требующими однотипных операций над элементами массива, удобно использовать индексную адресацию. Схема индексной адресации аналогична базированию путем суммирования (см. рис. 3.5).

В этом случае адрес i-гo операнда в массиве определяется как сумма начального адреса массива (задаваемого полем смещения С) и индекса И, записанного в одном из регистров РП, называемом теперь индексным регистром. Адрес индексного регистра задается в команде полем адреса индекса — Аин(аналогично Аб).

В каждом i-м цикле содержимое индексного регистра изменяется на величину постоянную (часто равную 1). Использование индексной адресации значительно упрощает программирование циклических алгоритмов.

Для эффективной работы при относительной адресации применяется комбинированная индексация с базированием, при которой адрес операнда вычисляется как сумма трех величин (рис. 3.7):

Аи= Б + И + С.

Рис. 3.6.Схема формирования относительного адреса способом совмещения кодов базы и смещения.

Рис. 3.7 Схема формирования дополнительного адреса при индексной адресации и базировании: АИН - адрес индексного регистра.