- •Введение

- •Общие сведения Технико-эксплуатационные характеристики эвм

- •История развития эвм

- •Классификация эвм

- •Классификация эвм по назначению

- •Классификация эвм по функциональным возможностям иразмерам

- •Функциональная и структурная организация эвм

- •Связь между функциональной и структурной организацией эвм

- •Обобщенная структура эвм и пути её развития

- •Обрабатывающая подсистема

- •Подсистема памяти

- •Подсистема ввода-вывода

- •Подсистема управления и обслуживания

- •Архитектуры эвм

- •Sisd-компьютеры

- •Компьютеры с cisc архитектурой

- •Компьютеры с risc архитектурой

- •Компьютеры с суперскалярной обработкой

- •Simd-компьютеры

- •Матричная архитектура

- •Векторно-конвейерная архитектура

- •Ммх технология

- •Misd компьютеры

- •Mimd компьютеры

- •Многопроцессорные вычислительные системы

- •Многопроцессорные вычислительные системы с общей шиной.

- •Многопроцессорные вычислительные системы с многовходовыми модулями оп.

- •Многомашинные вычислительные системы (ммвс)

- •Многомашинные комплексы

- •Ммр архитектура

- •Структура и форматы команд эвм

- •Форматы команд эвм

- •Способы адресации

- •Классификация способов адресации по наличию адресной информации в команде

- •Классификация способов адресации по кратности обращения в память

- •Классификация по способу формирования исполнительных адресов ячеек памяти

- •Относительная адресация

- •Стековая адресация

- •Теги и дескрипторы. Самоопределяемые данные

- •Процессоры. Центральный процессор

- •Логическая структура цп

- •Структурная схема процессора

- •Характеристики процессора

- •Регистровые структуры центрального процессора

- •Основные функциональные регистры

- •Регистры процессора обработки чисел с плавающей точкой

- •Системные регистры

- •Регистры отладки и тестирования

- •Назначение и Классификация цуу

- •Устройства управления цп

- •Цуу с жесткой логикой.

- •Цуу с микропрограммной логикой

- •Процедура выполнения команд

- •Язык микроопераций

- •Описание слов, регистров и шин

- •Описание массива данных и памяти.

- •Описание микроопераций

- •Условные микрооператоры.

- •Арифметико-логическое устройство

- •Структура алу

- •Сумматоры

- •Классификация алу

- •Методы повышения быстродействия алу

- •Память эвм

- •Организация внутренней памяти процессора.

- •Оперативная память и методы управления оп

- •Методы управления памятью без использования дискового пространства (без использования внешней памяти).

- •Распределение памяти фиксированными разделами.

- •Размещение памяти с перемещаемыми разделами.

- •Организация виртуальной памяти.

- •Страничное распределение.

- •Сегментное распределение.

- •Странично - сегментное распределение.

- •Свопинг

- •Методы повышения пропускной способности оп.

- •Выборка широким словом.

- •Расслоение сообщений.

- •Методы организации кэш-памяти

- •Типовая структура кэш-памяти

- •Способы размещения данных в кэш-памяти.

- •Прямое распределение.

- •Полностью ассоциативное распределение.

- •Частично ассоциативное распределение.

- •Распределение секторов.

- •Методы обновления строк в основной памяти

- •Системы внешней памяти

- •Общие принципы организации системы прерывания программ

- •Характеристики системы прерываний

- •Программно-управляемый приоритет прерывающих программ

- •Организация перехода к прерывающей программе

- •ПодСистема ввода/вывода Принципы организации подсистемы ввода/вывода

- •Каналы ввода-вывода

- •Интерфейсы ввода-вывода

- •Классификация интерфейсов

- •Типы и характеристики стандартных шин

- •Вычислительные системы

- •Общие положения

- •Классификация вс

- •Понятие открытой системы

- •Кластерные структуры

- •12. Библиографический список

- •Содержание

- •1. Общие сведения 5

- •2. Архитектуры эвм 22

- •3. Структура и форматы команд эвм 37

- •4. Типы данных 47

- •5. Процессоры. Центральный процессор 53

- •6. Язык микроопераций 72

- •7. Арифметико-логическое устройство 77

- •8. Память эвм 84

- •9. Общие принципы организации системы прерывания программ 118

- •10. ПодСистема ввода/вывода 125

- •11. Вычислительные системы 134

- •12. Библиографический список 140

Векторно-конвейерная архитектура

В отличие от матричной, векторно-конвейерная структуракомпьютера содержит конвейер операций, на котором обрабатываются параллельно элементы векторов и полученные результаты последовательно записываются в единую память. При этом отпадает необходимость в коммутаторе процессорных элементов, служащем камнем преткновения в матричных компьютерах.

Векторно-конвейерную структуру имеют однопроцессорные супер-ЭВМ серии VP фирмы Fujitsu; серии S компании Hitachi; C90, М90, Т90 фирмы Cray Research; Сгау-3, Сгау-4 фирмы Cray Computer и т.д. Общим для всех векторных суперкомпьютеров является наличие в системе команд векторных операций, допускающих работу с векторами определенной длины, допустим, 64 элемента по 8 байт. В таких компьютерах операции с векторами обычно выполняются над векторными регистрами.

Ммх технология

Еще одним примером SIMD-архитектуры является технология ММХ, которая существенно улучшила архитектуру микропроцессоров фирмы Intel. Технология MMX представляет собой компромиссное решение, объединяющее пути, используемые в классическом процессоре CISC-архитектуры (Pentium), в компьютерах с параллельной SIMD-архитектурой, с добавлением ряда простых (RISC) команд параллельной обработки данных. Она разработана для ускорения выполнения мультимедийных и коммуникационных программ с добавлением новых типов данных и новых инструкций. Технология в полной мере использует параллелизм SIMD-архитектуры и сохраняет полную совместимость с существующими операционными системами и приложениями для SISD.

Точно также, как однопроцессорные компьютеры, представлены архитектурами с одним потоком данных SISD и множеством потоков данных SIMD, так и многопроцессорные системы могут быть представлены двумя базовыми типами архитектур в зависимости от параллелизма данных:

Misd компьютеры

в

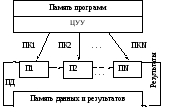

Рис.2.4. MISD-архитектура

MISD(Multiple Instruction Stream - Single Data Stream) или МКОД - множество потоков команд и один поток данных. MISD компьютеры представляет собой, как правило, регулярную структуру в виде цепочки последовательно соединенных процессоров П1, П2, ..., ПN, образующихпроцессорный конвейер(рис. 2.4). В такой системе реализуется принцип конвейерной (магистральной) обработки, который основан на разбиении всего процесса на последовательно выполняемые этапы, причем каждый этап выполняется на отдельном процессоре. Одинарный поток исходных данных для решения задачи поступает на вход процессорного конвейера. Каждый процессор решает свою часть задачи, и результаты решения в качестве исходных данных передает на вход последующего процессора. К каждому процессору подводится свой поток команд, т. е. наблюдается множественный поток команд ПК1, ПК2, ..., ПКN.

Вычислительных машин такого класса практически нет и трудно привести пример их успешной реализации. Один из немногих - систолический массив процессоров, в котором процессоры находятся в узлах регулярной решетки, роль ребер которой играют межпроцессорные соединения. Все процессорные элементы управляются общим тактовым генератором. В каждом цикле работы каждый процессорный элемент получает данные от своих соседей, выполняет одну команду и передает результат соседям.

В дальнейшем для MISD нашлась ещё одна адекватная организация вычислительной системы - распределенная мультипроцессорная система с общими данными. Наиболее простая и самая распространенная система этого класса - обычная локальная сеть персональных компьютеров, работающая с единой базой данных, когда много процессоров обрабатывают один поток данных. Впрочем, тут есть одна тонкость. Как только в такой сети все пользователи переключаются на обработку собственных данных, недоступных для других абонентов сети, MISD - система превращается в систему с множеством потоков команд и множеством потоков данных, соответствующую MIMD-архитектуре.