- •Введение

- •Общие сведения Технико-эксплуатационные характеристики эвм

- •История развития эвм

- •Классификация эвм

- •Классификация эвм по назначению

- •Классификация эвм по функциональным возможностям иразмерам

- •Функциональная и структурная организация эвм

- •Связь между функциональной и структурной организацией эвм

- •Обобщенная структура эвм и пути её развития

- •Обрабатывающая подсистема

- •Подсистема памяти

- •Подсистема ввода-вывода

- •Подсистема управления и обслуживания

- •Архитектуры эвм

- •Sisd-компьютеры

- •Компьютеры с cisc архитектурой

- •Компьютеры с risc архитектурой

- •Компьютеры с суперскалярной обработкой

- •Simd-компьютеры

- •Матричная архитектура

- •Векторно-конвейерная архитектура

- •Ммх технология

- •Misd компьютеры

- •Mimd компьютеры

- •Многопроцессорные вычислительные системы

- •Многопроцессорные вычислительные системы с общей шиной.

- •Многопроцессорные вычислительные системы с многовходовыми модулями оп.

- •Многомашинные вычислительные системы (ммвс)

- •Многомашинные комплексы

- •Ммр архитектура

- •Структура и форматы команд эвм

- •Форматы команд эвм

- •Способы адресации

- •Классификация способов адресации по наличию адресной информации в команде

- •Классификация способов адресации по кратности обращения в память

- •Классификация по способу формирования исполнительных адресов ячеек памяти

- •Относительная адресация

- •Стековая адресация

- •Теги и дескрипторы. Самоопределяемые данные

- •Процессоры. Центральный процессор

- •Логическая структура цп

- •Структурная схема процессора

- •Характеристики процессора

- •Регистровые структуры центрального процессора

- •Основные функциональные регистры

- •Регистры процессора обработки чисел с плавающей точкой

- •Системные регистры

- •Регистры отладки и тестирования

- •Назначение и Классификация цуу

- •Устройства управления цп

- •Цуу с жесткой логикой.

- •Цуу с микропрограммной логикой

- •Процедура выполнения команд

- •Язык микроопераций

- •Описание слов, регистров и шин

- •Описание массива данных и памяти.

- •Описание микроопераций

- •Условные микрооператоры.

- •Арифметико-логическое устройство

- •Структура алу

- •Сумматоры

- •Классификация алу

- •Методы повышения быстродействия алу

- •Память эвм

- •Организация внутренней памяти процессора.

- •Оперативная память и методы управления оп

- •Методы управления памятью без использования дискового пространства (без использования внешней памяти).

- •Распределение памяти фиксированными разделами.

- •Размещение памяти с перемещаемыми разделами.

- •Организация виртуальной памяти.

- •Страничное распределение.

- •Сегментное распределение.

- •Странично - сегментное распределение.

- •Свопинг

- •Методы повышения пропускной способности оп.

- •Выборка широким словом.

- •Расслоение сообщений.

- •Методы организации кэш-памяти

- •Типовая структура кэш-памяти

- •Способы размещения данных в кэш-памяти.

- •Прямое распределение.

- •Полностью ассоциативное распределение.

- •Частично ассоциативное распределение.

- •Распределение секторов.

- •Методы обновления строк в основной памяти

- •Системы внешней памяти

- •Общие принципы организации системы прерывания программ

- •Характеристики системы прерываний

- •Программно-управляемый приоритет прерывающих программ

- •Организация перехода к прерывающей программе

- •ПодСистема ввода/вывода Принципы организации подсистемы ввода/вывода

- •Каналы ввода-вывода

- •Интерфейсы ввода-вывода

- •Классификация интерфейсов

- •Типы и характеристики стандартных шин

- •Вычислительные системы

- •Общие положения

- •Классификация вс

- •Понятие открытой системы

- •Кластерные структуры

- •12. Библиографический список

- •Содержание

- •1. Общие сведения 5

- •2. Архитектуры эвм 22

- •3. Структура и форматы команд эвм 37

- •4. Типы данных 47

- •5. Процессоры. Центральный процессор 53

- •6. Язык микроопераций 72

- •7. Арифметико-логическое устройство 77

- •8. Память эвм 84

- •9. Общие принципы организации системы прерывания программ 118

- •10. ПодСистема ввода/вывода 125

- •11. Вычислительные системы 134

- •12. Библиографический список 140

Основные функциональные регистры

Содержимое этих регистров определяется текущей задачей, т.е. в эти регистры автоматически загружается новое значение при переключении задач.

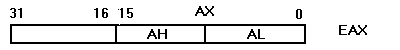

Регистры общего назначения. Восемь 32-разрядных регистров предназначены для хранения данных и адресов. Они поддерживают работу с данными разрядностью 1,8, 16, 32 и 64 бита, битовыми полями длиной от 1 до 32 бит и адресами размером 16 и 32 бита. Младшие 16 разрядов этих регистров (рис. 5.3) доступны отдельно при использовании соответствующего имени, например регистр ЕАХ (имя АХ для 16 разрядов).

Рис. 5.3. Структура регистра общего назначения ЕАХ

При операциях с байтами можно отдельно обращаться к младшему байту (разряды 0 - 7) и старшему байту (8 – 15) по именам AL и АН. Доступ к отдельным байтам обеспечивает дополнительную гибкость при операциях с данными.

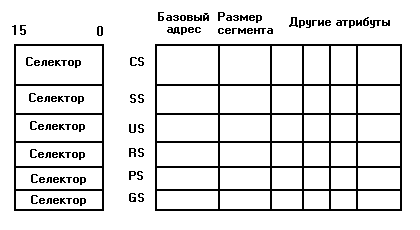

Регистры сегментов и дескрипторы сегментов. Шесть 16-разрядных сегментных регистров (CS, SS, DS, ES, FS, GS) содержат значения селекторов сегментов, указывающих на текущие адресуемые сегменты памяти. С каждым из них связан программно-недоступный регистр дескриптора сегмента (рис. 5.4).

В защищенном режиме каждый сегмент может иметь размер от 1 байта до 4 Гбайт, в режиме реальных адресов максимальный размер сегмента составляет 64 Кбайта.

Селектор в CS обеспечивает обращение к текущему сегменту команд, селектор в SS — к текущему сегменту стека, селекторы в DS, ES, FS, GS — к текущим сегментам данных. Каждый регистр дескриптора содержит 32-разрядный размер сегмента и другие необходимые атрибуты.

Когда в регистр сегмента загружается новое значение селектора, содержимое соответствующего регистра дескриптора автоматически корректируется. В реальном режиме базовый адрес сегмента получается путем сдвига значения селектора на 4 разряда влево (20 разрядов), максимальный размер и атрибуты сегмента в реальном режиме имеют фиксированные значения.

Рис. 5.4. Регистры сегментов и соответствующие регистры дескрипторов

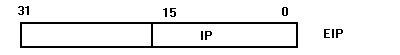

Указатель команд. Указатель команд (рис. 5.5) представляет собой 32-разрядный регистр с именем EIP, содержимое которого используется в качестве смещения при определении адреса следующей выполняемой команды. Смещение задается относительно базового адреса сегмента команд CS. Младшие 16 бит (0 — 15) содержат 16-разрядный указатель команд с именем IP, который используется при 16-разрядной адресации.

Рис. 5.5. Структура регистра указателя команд

Указатель команд непосредственно программисту недоступен. Его содержимое изменяется при выполнении команд передачи управления и прерываний.

Регистр флаговявляется 32-разрядным, имеет имя EFLAGS. Его разряды содержат признаки результата выполнения команды, управляют обработкой прерываний, последовательностью вызываемых задач, вводом/выводом и рядом других процедур.

Регистры процессора обработки чисел с плавающей точкой

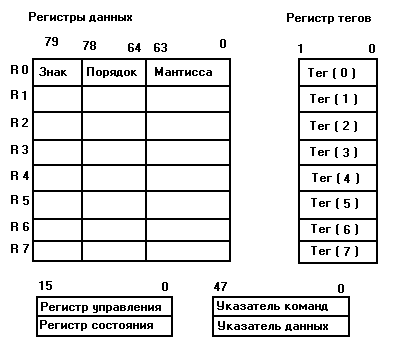

Набор регистров, входящих в блок (FPU), изображен на рис. 5.6.

Рис. 5.6. Регистры блока FPU.

Регистр тегов FPU содержит 16-разрядное слово, включающее восемь двухбитовых тегов. Каждый тег (признак) характеризует содержимое одного из регистров данных.

Тегопределяет, является ли регистр пустым (незаполненным) - код 11 или в него введено конечное число — 00 (достоверное значение), или нуль -01, неопределенное значение (бесконечность) — 10 (нет числа и неподдерживаемый формат). Слово тегов позволяет оптимизировать функционирование FPU посредством идентификации пустых и непустых регистров данных, проверить содержимое регистра без сложного декодирования хранящихся в нем данных.