- •Н.Ю. Юдина в.Н. Харин вычислительные машины, системы и сети

- •Лабораторная работа № 1 Формирование логических структур

- •Лабораторная работа № 2 Иерархическая структура памяти. Модели памяти

- •Лабораторная работа № 3 Организация управления эвм

- •1. Обработка прерываний

- •2. Управление многозадачностью

- •2. Обработка исключений

- •4. Передача управления

- •Лабораторная работа № 4 Архитектура микропроцессоров

- •Лабораторная работа № 5 Интерфейс

- •Регистровая модель процессора

- •Стандартные интерфейсы:com,usb

- •Сом-порт

- •Ресурсы и конфигурирование сом-портов

- •Последовательная шина usb

- •Лабораторная работа № 6 Телекоммуникации и сети

- •Библиографический список

- •Вычислительные машины, системы и сети

Лабораторная работа № 4 Архитектура микропроцессоров

Понятие архитектуры микропроцессора включает в себя систему команд и способы адресации, возможность совмещения выполнения команд во времени, наличие дополнительных устройств в составе микропроцессора, принципы и режимы его работы. Выделяют понятия микроархитектуры и макроархитектуры.

Микроархитектура микропроцессора – это аппаратная организация и логическая структура микропроцессора, регистры, управляющие схемы, арифметико-логические устройства, запоминающие устройства и связывающие их информационные магистрали.

Макроархитектура – это система команд, типы обрабатываемых данных, режимы адресации и принципы работы микропроцессора.

В общем случае под архитектурой ЭВМ понимается абстрактное представление машины в терминах основных функциональных модулей, языка ЭВМ, структуры данных.

Типы архитектур

Существует несколько подходов к классификации микропроцессоров по типу архитектуры. Так, выделяют МП с CISC (Complete Instruction Set Computer) архитектурой, характеризуемой полным набором команд, и RISC (Reduce Instruction Set Computer) архитектурой, которая определяет систему с сокращенным набором команд одинакового формата, выполняемых за один такт МП.

Определяя в качестве основной характеристики МП разрядность, выделяют следующие типы МП архитектуры:

- с фиксированной разрядностью и списком команд (однокристальные);

- с наращиваемой разрядностью (секционные) и микропрограммным управлением.

Анализируя адресные пространства программ и данных, определяют МП с архитектурой фон Неймана (память программ и память данных находятся в едином пространстве и нет никаких признаков, указывающих на тип информации в ячейке памяти) и МП с архитектурой Гарвардской лаборатории (память программ и память данных разделены, имеют свои адресные пространства и способы доступа к ним).

Рассмотрим более подробно основные типы архитектурных решений, выделяя связь со способами адресации памяти.

Регистровая архитектура определяется наличием достаточно большого регистрового файла внутри МП. Команды получают возможность обратиться к операндам, расположенным в одной из двух запоминающих сред: оперативной памяти или регистрах. Размер регистра обычно фиксирован и совпадает с размером слова, физически реализованного в оперативной памяти. К любому регистру можно обратиться непосредственно, поскольку регистры представлены в виде массива запоминающих элементов – регистрового файла. Типичным является выполнение арифметических операций только в регистре, при этом команда содержит два операнда (оба операнда в регистре или один операнд в регистре, а второй в оперативной памяти).

Стековая архитектура дает возможность создать поле памяти с упорядоченной последовательностью записи и выборки информации. В общем случае команды неявно адресуются к элементу стека, расположенному на его вершине, или к двум верхним элементам стека.

Архитектура МП, ориентированная на оперативную память (типа "память-память"), обеспечивает высокую скорость работы и большую информационную емкость рабочих регистров и стека при их организации в оперативной памяти. Архитектура этого типа не предполагает явного определения аккумулятора, регистров общего назначения или стека; все операнды команд адресуются к области основной памяти.

С точки зрения важности для пользователя-программиста под архитектурой в общем случае понимают совокупность следующих компонентов и характеристик:

- разрядности адресов и данных;

- состава, имен и назначения программно-доступных регистров;

- форматов и системы команд;

- режимов адресации памяти;

- способов машинного представления данных разного типа;

- структуры адресного пространства;

- способа адресации внешних устройств и средств выполнения операций ввода/вывода;

- классов прерываний, особенностей инициирования и обработки прерываний.

Командный и машинный циклы

Центральный процессор (ЦП) выполняет основную работу по обработке данных и управлению другими блоками компьютера в соответствии с программой. Для этого ЦП должен быть в состоянии:

выбирать (извлекать) команды из памяти;

декодировать их двоичные коды (определять содержание инструкции);

выполнять команды.

Все действия процессора, а следовательно и всей системы, синхронизируются тактовыми импульсами. За один такт выполняются некоторые элементарные действия.

Последовательность тактов, в течение которой ЦП выполняет все действия, предписанные командой, называют командным циклом.

Процессор, если этого требует команда, должен уметь обратиться к памяти, чтобы выбрать (“прочитать”) необходимые данные (операнды) или сохранить (“записать”) результаты операции. Другие команды могут потребовать осуществить ввод или вывод данных посредством внешних устройств ввода/вывода (УВВ). Последовательность тактов, в течение которых процессор осуществляет одно обращение к памяти или внешнему устройству, называют машинным циклом. Командный цикл (КЦ) может содержать один или несколько машинных циклов (МЦ).

Диаграмма (фазы) выполнения команд

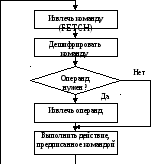

Исполняя команду за командой программы, процессор выполняет циклические действия. В общем виде командный цикл можно проиллюстрировать следующей диаграммой.

Как видим, цикл любой команды содержит хотя бы один машинный цикл, это цикл извлечения команды из памяти (Fetch). Если команда требует операнд, то она будет содержать еще один машинный цикл – цикл чтения памяти (MEMR - Memory Read).

Если результат команды должен быть сохранен в памяти, то потребуется цикл записи в память (MEMW – Memory Write). Команды, выполняющие ввод или вывод данных из/на УВВ, будут содержать циклы ввода (IOR – Input/Output Read) или циклы вывода (IOW – Input/Output Write).

Рис.48 Диаграмма командного цикла

Принцип 3М (микропрограммируемость, модульность, магистральность)

Микропрограммируемость (принцип микропрограммного управления)

Реализация той или иной фазы команды требует определенного количества тактов. Устройство управления в каждом такте подает на остальные узлы процессора и другие блоки ЭВМ сигналы управления (микроинструкции), предписывающие им выполнить в этом такте те или иные действия, либо остаться в том же состоянии. Каждую микроинструкцию можно закодировать двоичным кодом. В простейшем случае этот код может состоять из одного бита и соответствовать активному («1») или не активному («0») значению сигнала. Например, принять («защелкнуть») данные в регистр. Для управления более сложными узлами может понадобиться одновременно подать несколько сигналов. В этом случае микроинструкция должна содержать несколько бит.

Если все микроинструкции, действующие в одном такте, разместить в определенном порядке, то получим многоразрядную двоичную комбинацию, называемую микрокомандой.

Последовательность микрокоманд, такт за тактом реализующая определенную фазу командного цикла (машинный цикл), называют микропрограммой (P) . Таким образом, реализуя ту или иную команду, которую теперь логично назвать “внешней”, процессор выполняет определенный набор внутренних микропрограмм (P1,…, Pm). Этот принцип иллюстрирует рис. 49.

|

Такт 1 |

Микрокоманда 1 000101101011010111101 … 0 |

Микро-программа 1 – FETCH (P1) |

Команда |

|

Такт 2 |

Микрокоманда 2 100111001001010100101 … 0 | ||

|

Такт 3 |

Микрокоманда 2 110111001001010100101 … 1 | ||

|

Такт 4 |

Микрокоманда 4 100111001010110100101 … 0 |

(P2) | |

|

Такт 5 |

Микрокоманда 5 100111001001010100101 … 1 | ||

|

. . . |

|

. . . | |

|

Такт n-2 |

Микрокоманда n-2 |

(Pm) | |

|

Такт n-1 |

Микрокоманда n-1 | ||

|

Такт n |

Микрокоманда n |

Рис. 49 Микропрограмма состоит из нескольких микрокоманд

Рассмотренный принцип управления процессором получил название принципа микропрограммного управления.

Согласно этому принципу все множество микропрограмм размещают внутри самого процессора в так называемой микропрограммной памяти (МПП), выполненной по технологии постоянной памяти (ПЗУ микропрограмм). Теперь устройству управления процессора для реализации той или иной фазы команды достаточно отработать соответствующую микропрограмму, т.е. последовательно, такт за тактом извлекать из микропрограммной памяти микрокоманды, преобразовывать их в наборы сигналов, которые по соответствующим линиям связи будут поданы на нужные узлы.

Реализация такого принципа приводит к обобщенной структуре процессора, показанной на рис.50.

Рис.50 Обобщенная структура процессора

Форматы передачи данных

Рассмотрим некоторые общие вопросы, связанные с обменом данными между ВУ и микроЭВМ. Существуют два способа передачи слов информации по линиям данных: параллельный, когда одновременно пересылаются все биты слова, и последовательный, когда биты слова пересылаются поочередно, начиная, например, с его младшего разряда.

Так как между отдельными проводниками шины для параллельной передачи данных существует электрическая емкость, то при изменении сигнала, передаваемого по одному из проводников, возникает помеха (короткий выброс напряжения) на других проводниках. С увеличением длины шины (увеличением емкости проводников) помехи возрастают и могут восприниматься приемником как сигналы. Поэтому рабочее расстояние для шины параллельной передачи данных ограничивается длиной 1-2 м, и только за счет существенного удорожания шины или снижения скорости передачи длину шины можно увеличить до 10-20 м.

Указанное обстоятельство и желание использовать для дистанционной передачи информации телеграфные и телефонные линии обусловили широкое распространение способа последовательного обмена данными между ВУ и микроЭВМ и между несколькими микроЭВМ. Возможны два режима последовательной передачи данных: синхронный и асинхронный.

При синхронной последовательной передаче каждый передаваемый бит данных сопровождается импульсом синхронизации, информирующим приемник о наличии на линии информационного бита. Следовательно, между передатчиком и приемником должны быть протянуты минимум три провода: два для передачи импульсов синхронизации и бит данных, а также общий заземленный проводник. Если же передатчик (например, микроЭВМ) и приемник (например, дисплей) разнесены на несколько метров, то каждый из сигналов (информационный и синхронизирующий) придется посылать либо по экранированному (телевизионному) кабелю, либо с помощью витой пары проводов, один из которых заземлен или передает сигнал, инверсный основному.

Синхронная последовательная передача начинается с пересылки в приемник одного или двух символов синхронизации (не путать с импульсами синхронизации). Получив такой символ (символы), приемник начинает прием данных и их преобразование в параллельный формат. Естественно, что при такой организации синхронной последовательной передачи она целесообразна лишь для пересылки массивов слов, а не отдельных символов. Это обстоятельство, а также необходимость использования для обмена сравнительно дорогих (четырехпроводных или кабельных) линий связи помешало широкому распространению синхронной последовательности передачи данных.

Асинхронная последовательная передача данных означает, что у передатчика и приемника нет общего генератора синхроимпульсов и что синхронизирующий сигнал не посылается вместе с данными. Как же в таком случае приемник будет узнавать о моментах начала и завершения передачи бит данных. Опишем простую процедуру, которую можно использовать, если передатчик и приемник асинхронной последовательной передачи данных согласованы по формату и скорости передачи.

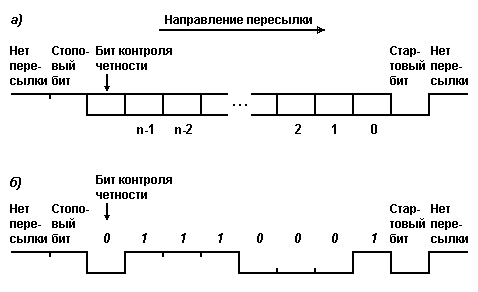

Стандартный формат асинхронной последовательной передачи данных, используемый в ЭВМ и ВУ, содержит n пересылаемых бит информации (при пересылке символов n равно 7 или 8 битам) и 3-4 дополнительных бита: стартовый бит, бит контроля четности (или нечетности) и 1 или 2 стоповых бита (рис. 51, а). Бит четности (или нечетности) может отсутствовать. Когда передатчик бездействует (данные не посылаются на линию), на линии сохраняется уровень сигнала, соответствующий логической 1.

Рис. 51 Формат асинхронной последовательной передачи данных.

Передатчик может начать пересылку символа в любой момент времени посредством генерирования стартового бита, т. е. перевода линии в состояние логического 0 на время, точно равное времени передачи бита. Затем происходит передача битов символа, начиная с младшего значащего бита, за которым следует дополнительный бит контроля по четности или нечетности. Далее с помощью стопового бита линия переводится в состояние логической 1 (рис. 51,б). При единичном бите контроля стоповый бит не изменяет состояния сигнала на линии. Состояние логической 1 должно поддерживаться в течение промежутка времени, равного 1 или 2 временам передачи бита.

Промежуток времени от начала стартового бита до конца стопового бита (стоповых бит) называется кадром. Сразу после стоповых бит передатчик может посылать новый стартовый бит, если имеется другой символ для передачи; в противном случае уровень логической 1 может сохраняться на протяжение всего времени, пока бездействует передатчик. Новый стартовый бит может быть послан в любой момент времени после окончания стопового бита, например, через промежуток времени, равный 0.43 или 1.5 времени передачи бита.

В линиях последовательной передачи данных передатчик и приемник должны быть согласованы по всем параметрам формата, изображенного на рис. 8, включая номинальное время передачи бита. Для этого в приемнике устанавливается генератор синхроимпульсов, частота которого должна совпадать с частотой аналогичного генератора передатчика. Кроме того, для обеспечения оптимальной защищенности сигнала от искажения, шумов и разброса частоты синхроимпульсов приемник должен считывать принимаемый бит в середине его длительности. Рассмотрим работу приемника с того момента, когда он закончил прием символаданных и перешел в режим обнаружения стартового бита следующего слова.

Если линия перешла в состояние логического нуля и находится в этом состоянии в течение времени, не меньшего половины временного интервала передачи бита, то приемник переводится в режим считывания бит информации. В противном случае приемник остается в режиме обнаружения, так как вероятнее всего это был не стартовый бит, а шумовая помеха. В новом режиме приемник вырабатывает сигналы считывания через интервалы, равные времени передачи бита, т. е. выполняет считывание и сохранение принимаемых бит примерно на середине их передачи. Аналогичным образом будут считаны бит контроля четности и сигнал логической единицы (стоповый бит). Если оказалось, что на месте стопового бита обнаружен сигнал логического нуля, то произошла "Ошибка кадра" и символ принят неправильно. Иначе проверяется, четно ли общее число единиц в информационных битах и бите контроля, и если оно четно, производится запись принятого символа в буфер приемника.

Передний фронт стартового бита сигнализирует о начале поступления передаваемой информации, а момент его появления служит точкой отсчета времени для считывания бит данных. Стоповый бит предоставляет время для записи принятого символа в буфер приемника и обеспечивает возможность выявления ошибки кадра. Наиболее часто ошибки кадра появляются тогда, когда приемник ошибочно синхронизирован с битом 0, который в действительности не является стартовым битом. Если передатчик бездействует (посылает сигнал логической единицы) в течение одного кадра или более, то всегда можно восстановить правильную синхронизацию. Хуже обстоит дело при рассинхронизации генераторов передатчика и приемника, когда временной интервал между сигналами считывания принимаемых битов будет меньше или больше времени передачи бита.

Например, если при считывании битов посылки, показанной на рис. 51б, временной интервал между сигналами считывания станет на 6% меньше, чем время передачи бита, то восьмой и девятый сигналы считывания будут выработаны тогда, когда на линии находится бит контроля четности (рис. 52). Следовательно, не будет обнаружен стоповый бит и будет зафиксирована ошибка кадра, несмотря на правильность принятой информации. Однако при 18%-й рассинхронизации генераторов, когда вместо кода (01110001) приемник зафиксирует код (11100001), никаких ошибок не будет обнаружено – четность соблюдена и стоповый (девятый по порядку) бит равен 1 (см. рис. 52).

Рис. 52. Ошибка из-за рассинхронизации генераторов передатчика и приемника.

Режимы адресации

Для взаимодействия с различными модулями в ЭВМ должны быть средства идентификации ячеек внешней памяти, ячеек внутренней памяти, регистров МП и регистров устройств ввода/вывода. Поэтому каждой из запоминающих ячеек присваивается адрес, т.е. однозначная комбинация бит. Количество бит определяет число идентифицируемых ячеек. Обычно ЭВМ имеет различные адресные пространства памяти и регистров МП, а иногда – отдельные адресные пространства регистров устройств ввода/вывода и внутренней памяти. Кроме того, память хранит как данные, так и команды. Поэтому для ЭВМ разработано множество способов обращения к памяти, называемых режимами адресации.

Режим адресации памяти – это процедура или схема преобразования адресной информации об операнде в его исполнительный адрес.

Все способы адресации памяти можно разделить на:

1) прямой, когда исполнительный адрес берется непосредственно из команды или вычисляется с использованием значения, указанного в команде, и содержимого какого-либо регистра (прямая адресация, регистровая, базовая, индексная и т.д.);

2) косвенный, который предполагает, что в команде содержится значение косвенного адреса, т.е. адреса ячейки памяти, в которой находится окончательный исполнительный адрес (косвенная адресация).

В каждой микроЭВМ реализованы только некоторые режимы адресации, использование которых, как правило, определяется архитектурой МП.

Дополнительные режимы адресации

Режимы адресации 32-разрядных процессоров разработаны, исходя из требований образования 32-битового смещения. Другими словами, они предназначены для 32-разрядных приложений, в которых сегменты данных или стека (как, впрочем, и сегменты команд) могут иметь размеры до 232 = 4 Гбайт. Однако в реальном режиме размер любого сегмента ограничивается величиной 216 = 64 Кбайт, и 32-битовые смещения не имеют смысла. С другой стороны, ничто не мешает нам использовать для образования 16-битового смещения 32-разрядные регистры (ЕВХ, ESI и проч.), если, конечно, их реальное содержимое не будет превышать величины FFFFh. Указание в качестве операндов команд 32-разрядных регистров позволяет использовать дополнительные возможности 32-разрядных процессоров по части адресации памяти, что в некоторых случаях может оказаться полезным. Следует подчеркнуть, что речь идет здесь только о тех операндах, или, правильнее сказать, аргументах команды, которые описывают косвенную (через регистры) адресацию памяти.

В отличие от МП86, где базовыми регистрами могут быть только ВХ и ВР, а индексными только SI и DI, 32-разрядные процессоры допускают использование в качестве и базовых, и индексных практически всех регистров общего назначения. Таким образом, вполне законна команда вида

mov ЕАХ,[ЕСХ][EDX]

Второе отличие заключается в возможности масштабирования содержимого индексного регистра, т.е. умножения его на заданный в команде коэффициент, который может принимать значения 1, 2, 4 или 8. Пример такой адресации:

inc word ptr [ЕАХ] [ЕСХ*2]

Еще раз подчеркнем, что дополнительные режимы косвенной адресации требуют использования 32-разрядных регистров. Команды

inc word ptr [AX] [ECX*2] или inc word ptr [ЕАХ] [СХ*2]

рассматриваются ассемблером, как неправильные.

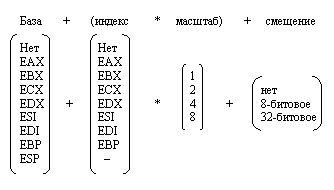

Режимы косвенной адресации памяти, предоставляемые 32-разрядными процессорами при использовании 32-разрядных регистров, изображены на рис. 53.

Из рисунка видно, что в качестве базового можно использовать все регистры общего назначения, включая даже указатель стека ESP. При этом, если в качестве базового выступает один из регистров ESP или ЕВР, то по умолчанию адресация осуществляется через сегментный регистр SS, хотя возможна замена сегмента. Во всех остальных случаях адресация по умолчанию осуществляется через сегментный регистр DS. Использование регистра ЕВР в качестве индексного не адресует нас к стеку: адресация по-прежнему осуществляется с помощью регистра DS.

Рис. 53 Режимы косвенной адресации с использованием 32-разрядных регистров.

Прочерк во второй колонке подчеркивает, что регистр ESP нельзя использовать в качестве индексного. Это не означает, что ESP нельзя указывать в качестве второго операнда:

mov ЕАХ,[ЕСХ][ESP]

Недопустима только конструкция, в которой содержимое ESP умножается на масштабирующий множитель:

mov ЕАХ,[ЕСХ][ESP*8]

Полезно также отметить, что смещение в команде вида

mov ЕАХ,[ЕВХ][ЕСХ]+20

может быть только или 8-битовым, или 32-битовым. 16-битовые смещения не образуются. Если указанная в команде величина смещения помещается в байт, как это имеет место в приведенном выше примере команды, то смещение в коде команды занимает 1 байт. Если же величина смещения больше 255, то под него в коде команды отводится сразу 32 бит.

Таким образом, понятия базовой и индексной адресации в 32-разрядных процессорах несколько размываются. Если регистр указывается с масштабирующим множителем, то это, конечно, индексная адресация. Если же множитель отсутствует, то адресацию и через ЕВХ, и через ESI с равным успехом можно отнести как к базовой, так и к индексной.

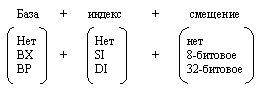

Использование для адресации памяти 16-разрядных регистров резко сужает возможности адресации 32-разрядных процессоров (рис. 54). В этом случае мы фактически имеем дело с МП 86.

Рис. 54. Режимы косвенной адресации с использованием 16-разрядных регистров.

Напомним, что в 16-разрядном режиме допустимы не все сочетания базовых и индексных регистров. В качестве базового регистра можно использовать только ВХ или ВР, а в качестве индексного только SI или DI.

Использование средств 32-разрядных процессоров в программировании

При разработке 16-разрядных программ реального режима, предназначенных для выполнения под управлением операционной системы MS-DOS, вполне допустимо использование ряда дополнительных возможностей 32-разрядных процессоров. В реальном режиме можно использовать:

32-разрядные операнды; дополнительные команды и расширенные возможности команд МП 86;

дополнительные режимы адресации;

четыре сегментных регистра для адресации данных вместо двух.

Для того чтобы транслятор распознавал все эти средства, необходимо начать программу с директивы .586 (или, при желании, .486 или .386) и указать при этом для сегментов команд и данных описатель use 16, чтобы программа осталась 16-разрядной.

Следует заметить, что возможности использования в программах реального режима дополнительных средств 32-разрядных процессоров, хотя и кажутся привлекательными, в действительности весьма ограничены. Новых команд не так уж много, и они не имеют принципиального характера; 32-разрядные данные используются в прикладных программах относительно редко (если не касаться вычислительных программ, содержащих действительные числа, но такие программы редко пишут на языке ассемблера); расширенные возможности адресации в полной мере проявляются лишь в 32-разрядных программах, не работающих в DOS. Тем не менее, в каких-то случаях привлечение средств 32-разрядных процессоров может оказаться полезным и в 16-разрядных программах.

Среди системных данных DOS и BIOS есть данные, требующие для своего размещения 2 слов. К таким данным, в частности, относится системное время, накапливаемое в 4х-байтовой ячейке с абсолютным адресом 46Ch. Выше, в разделе 3.5, уже описывалась системная процедура отсчета текущего времени. В процессе начальной загрузки компьютера в ячейку с адресом 46Ch переносится из часов реального времени время, истекшее от начала суток, а затем содержимое этой ячейки увеличивается на 1 каждым прерыванием от системного таймера, подключенного к вектору 8. Чтение ячейки 46Ch позволяет определить текущее время с погрешностью приблизительно в 1/18 секунды, что позволяет достаточно точно измерять интервалы времени. Арифметические действия с системным временем удобно выполнять в расширенных 32-разрядных регистрах.

Система команд

Проектирование системы команд оказывает влияние на структуру ЭВМ. Оптимальную систему команд иногда определяют как совокупность команд, которая удовлетворяет требованиям проблемно-ориентированных применений таким образом, что избыточность аппаратных и аппаратно-программных средств на реализацию редко используемых команд оказывается минимальной. В различных программах ЭВМ частота появления команд различна; например, по данным фирмы DEC в программах для ЭВМ семейства PDP-11 наиболее часто встречается команда передачи MOV(B), на ее долю приходится приблизительно 32% всех команд в типичных программах. Систему команд следует выбирать таким образом, чтобы затраты на редко используемые команды были минимальными.

При наличии статистических данных можно разработать (выбрать) ЭВМ с эффективной системой команд. Одним из подходов к достижению данной цели является разработка команд длиной в одно слово и кодирование их таким образом, чтобы разряды таких коротких команд использовать оптимально, что позволит сократить время реализации программы и ее длину.

Другим подходом к оптимизации системы команд является использование микроинструкций. В этом случае отдельные биты или группы бит команды используются для кодирования нескольких элементарных операций, которые выполняются в одном командном цикле. Эти элементарные операции не требуют обращения к памяти, а последовательность их реализации определяется аппаратной логикой.

Сокращение времени выполнения программ и емкости памяти достигается за счет увеличения сложности логики управления.

Важной характеристикой команды является ее формат, определяющий структурные элементы команды, каждый из которых интерпретируется определенные образом при ее выполнении. Среди таких элементов (полей) команды выделяют следующие: код операции, определяющий выполняемое действие; адрес ячейки памяти, регистра процессора, внешнего устройства; режим адресации; операнд при использовании непосредственной адресации; код анализируемых признаков для команд условного перехода.

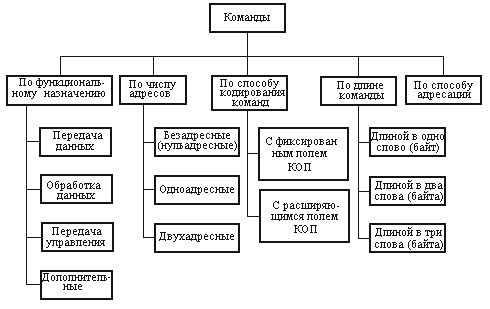

Классификация команд по основным признакам представлена на рис. 55. Важнейшим структурным элементом формата любой команды является код операции (КОП), определяющей действие, которое должно быть выполнено. Большое число КОП в процессоре очень важно, так как аппаратная реализация команд экономит память и время. Но при выборе ЭВМ необходимо концентрировать внимание на полноте операций с конкретными типами данных, а не только на числе команд, на доступных режимах адресации. Число бит, отводимое под КОП, является функцией полного набора реализуемых команд.

При использовании фиксированного числа бит под КОП для кодирования всех m команд необходимо в поле КОП выделить несколько двоичных разрядов. Однако, учитывая ограниченную длину слова мини- и микроЭВМ, различное функциональное назначение команд, источники и приемники результатов операций, а также то, что не все команды содержат адресную часть для обращения к памяти и периферийным устройствам, в малых ЭВМ для кодирования команд широко используется принцип кодирования с переменным числом бит под поле КОП для различных групп команд.

Рис. 55 Классификация команд.

В некоторых командах необходим только один операнд и они называются однооперандными (или одноадресными) командами в отличие от двухоперандных (или двухадресных), в которых требуются два операнда. При наличии двух операндов командой обычно изменяется только один из них. Так как информация берется только из одной ячейки, эту ячейку называются источником; ячейка, содержимое которой изменяется, называется приемником.

Ниже приведен формат двухадресной (двухоперандной) команды процессоров.

Форматы команд и система команд

Структура машинной программы обуславливается набором команд рассматриваемой ЭВМ и порядком обработки команд машиной. Команды, каждая из которых соответствует отдельной операции, обрабатываются процессором последовательно.

Команда осуществляет изменение содержания определенного регистра или передачу содержимого определенного регистра в другой регистр. Выполнение команды, таким образом, соответствует определенному переходу из одного состояния в другое. Возможные переходы машины из одного состояния в другое описываются набором ее команд. И наоборот, действие каждой команды исчерпывающим образом характеризуется осуществляемым изменением перехода.

Команда работает с определенными ячейками памяти или регистрами, называемыми операндами команд, содержимое которых при выполнении команды читается и/или записывается. Машины обычно представляют пользователю фиксированный набор элементарных команд. Для каждой из этих команд в аппаратуре машины имеется соответствующая ее часть для выполнения данной команды. Различают следующие типы команд:

команды загрузки и передачи;

арифметические команды (двоичная арифметика для чисел с фиксированной точкой, двоичная арифметика для чисел с плавающей запятой, десятичная арифметика);

логические операции, выполняемые поразрядно над двоичными словами, выполняемые поразрядно над двоичными словами;

операции с адресами;

команды сдвига и организационные команды;

команды завершения программы;

команды перехода и вызова подпрограмм;

команды ввода/вывода;

управляющие команды (привилегированные команды для изменения статуса программ).

Здесь команды классифицированы по их действию на различные составные части машины.

Представление команд.

Команда содержит несколько составных частей (полей). Формат команды зависит от структуры машинных слов и обычно содержит:

указание на ту операцию, которая подлежит выполнению (операционная часть);

указание на то, с какими операндами надо работать (адресная часть);

дополнительную организационную информацию (индикаторная часть), причем эта информация часто содержится в адресной части.

Команда представляется в машине двоичным словом. Отдельные части (поля) этого слова задают упомянутую выше информацию. При машинной трактовке все данные также представляются в виде двоичных слов. Поэтому важно знать, как должно интерпретироваться это слово — как команда, как адрес или как элемент данных. Это достигается путем использования признаков.

Основной формат кодирования команд Ассемблера (на примере IBM) имеет следующий вид:

[метка] команда [операнд(ы)].

Машинные коды имеют различную длину: один, два, три или четыре байта. Многие специфические команды имеют однобайтовые машинные коды и не используют прямой адресации памяти, например:

КОД Обозначение

40 INCAXУвеличение АХ на 1

50 PUSHAXЗапись АХ в стек

C3RET(short) Короткий возврат из процедуры

CBRET(far) Длинный возврат из процедуры

FDSTDУстановка флага направления

Ни одна из перечисленных команд не использует прямой адресации памяти. Другие команды, использующие непосредственный операнд, 8-битовый регистр, регистровую пару или адрес памяти, требуют более сложного машинного кода. Команды, использующие регистр могут содержать три бита, указывающих на конкретный регистр, и один бит, определяющий размер регистра: байт или слово. Кроме того лишь некоторые команды обеспечивают доступ к сегментным регистрам.

Пример.

Команда MOV с однобайтовым непосредственным операндом.

MOV AH, 00 1011 0 100 00000000

w reg = AH

Первый байт машинного кода указывает на однобайтовый размер (w=0) и на регистр AH (100). Следующая команда MOV содержит непосредственный двухбайтовый операнд:

MOV AX,00 1011 1 000 00000000

w reg=AX

Первый байт машинного кода указывает на размер в одно слово (w=1) и на регистр AX (000).

Обобщать приведенные примеры не следует, так как указание регистра и бита w может быть в различных позициях кода.

Двухбайтовые команды.

Рассмотрим пример сложения содержимого регистров DX и AX:

ADD BX, AX 0000 0011 11 011 000

dw mod reg r/m

d=1 означает, что биты reg и w описывают операнд 1 (BX), а биты mod, r/m и w — операнд 2 (AX); w=1 определяет размер регистров в одно слово; mod=11 указывает, что операнд 2 является регистром; reg = 011, указывает, что операнд 1 является регистром BX; r/m=000, указывает что операнд 2 является регистром AX.

Трехбайтовые команды.

Трехбайтовые команды можно рассмотреть на примере команды MOV.

MOV mem, AX 10100001 dddddddd dddddddd

В данном примере w=1 означает слово, следовательно, предполагается 16-битовый регистр AX. Байты 2 и 3 содержат относительный адрес памяти.

Ниже приведен примерный перечень команд Ассемблера для процессоров 80286, 80386.

ADD: Сложение двоичных чисел. При выполнении данной операции прибавляется один байт или одно слово в памяти, регистре или непосредственно к содержимому регистра или прибавляет один байт или слово в регистре или непосредственно к памяти.

AND: Логическое И. Команда выполняет поразрядную конъюнкцию (И) битов двух операндов. Операнды представляют собой одно- или двухбайтовые величины в регистре или памяти. Второй операнд может содержать непосредственные данные. Команда AND проверяет два операнда поразрядно. Если два проверяемых бита равны 1, то в первом операнде устанавливается единичное значение бита, в других случаях нулевое.

CMP: Сравнение. Выполняется сравнение содержимого двух полей данных. Фактически команда CPM вычитает второй операнд из первого, но содержимое полей не изменяет. Операнды должны иметь одинаковую длину: байт или слово. Команда может сравнивать содержимое регистра, памяти или непосредственное значение с содержимым регистра; или содержимое регистра или непосредственное значение с содержимым памяти.

JMP: Безусловный переход. Выполняется переход по указанному адресу при любых условиях. Команда JMP заносит в регистр IP необходимый адрес перехода. Существует пять типов команды JMP для передачи управления внутри сегмента или между сегментами. При межсегментном переходе в регистр CS заносится также новый сегментный адрес.

LOOP: Цикл. Данная команда управляет выполнением группы команд определенное число раз. До начала цикла в регистр CX должно быть загружено число выполняемых циклов. Команда LOOP находится в конце цикла, где она уменьшает значение в регистре CX на единицу. Если значение в регистре CX не равно нулю, то команда передает управление по адресу, указанному в операнде (прибавляет к регистру IP значение операнда); в противном случае управление передается на следующую после LOOP команду (происходит выход из цикла).

MOV: Пересылка данных. Один байт или одно слово пересылается между регистрами или между регистром и памятью, а также передает непосредственное значение в регистр или в память. Команда MOV не может передавать данные между двумя адресами памяти. Существует семь типов команды MOV.

NEG: Изменение знака числа. Команда меняет двоичное значение из положительного в отрицательное и из отрицательного в положительное. Команда NEG вычисляет двоичное дополнение от указанного операнда: вычитает операнд из нуля и прибавляет единицу. Операндом может быть байт или слово в регистре или памяти.

NOT: Логическое НЕТ. Меняет нулевые биты на единичные и наоборот. Операндом может быть байт или слово в регистре или памяти.

OR: Логическое ИЛИ. Команда выполняет поразрядную дизъюнкцию (ИЛИ) над битами двух операндов. Операндами являются байты или слова в регистрах или памяти, второй операнд может иметь непосредственное значение. Команда OR обрабатывает операнды побитово. Если любой из проверяемых бит равен единице, то бит в операнде 1 становится равным единице, в противном случае бит в операнде 1 не изменяется.

OUT: Вывод байта или слова в порт. Байт или слово из регистра передается в порт вывода. Порт кодируется как фиксированный числовой операнд или как переменная в регистре.

Задание для выполнения работы

Форматы команд. Дать описание разрядов.

Привести примеры одноадресных команд. Привести примеры двухадресных команд.

Основной формат кодирования команд Ассемблера для компьютеров фирмы IBM.

Перечислить типы команд Ассемблера для компьютеров фирмы IBM.

Составные части (поля) команд.

Привести примеры использования команд Ассемблера.

Рассмотреть программу, которая позволяет установить требуемый временной интервал и отработать некоторым образом его окончание. Поскольку MS-DOS является однозадачной системой, единственным способом организации параллельных процессов – выполнения программы и ожидания окончания временного интервала – является использование механизма прерываний. В нашем случае программа содержит обработчик прерываний от системного таймера, который 18 раз в секунду читает системное время и сравнивает его значение с заданной заранее величиной. При достижении равенства обработчик прерываний либо сам отрабатывает это событие, либо устанавливает флаг окончания временного интервала, который периодически тестируется в основной программе. Первый вариант позволяет измерить временной интервал с большей точностью, но второй предоставляет больше возможностей, так как в обработчике прерываний нельзя обращаться к функциям DOS, а основная программа может делать все, что ей заблагорассудится.

; Пример 1. Чтение и сравнение системного времени

;по прерываниям от таймера .586 ;Будут 32-разрядные операнды assume CS : code, DS:code code segment use16 ;16-разрядное приложение org 100h ;Формат .COM main proc ;Сохраним исходный вектор mov AX,3508h int 21h mov word ptr old_08,BX mov word ptr old_08+2,ES ;Установим наш обработчик mov AX,2508h mov DX,offset new_08 int 21h ;Прочитаем системное время, прибавим требуемый интервал ;и сохраним в двухсловной ячейке памяти mov AX,40h ;Настройка ES на mov ES,AX ;область данных BIOS mov EAX, ES : 6Ch ;Получаем системное время add EAX,time_int ;Прибавить интервал mov time_end,EAX ;Сохраним в памяти ;Имитация рабочего цикла программы с опросом флага again: test flag,0FFh ;Проверка флага готовности jnz ok ;Если установлен, на OK mov АН,02h ;B ожидании окончания mov DL,'.' ;временного интервала int 2 In ;выводим на экран точки jmp again ;И снова на проверку флага ok: mov АН,09h ;Интервал завершен. mov DX,offset msg ;Выполним, что хотели int 2 In ;Завершим программу, восстановив сначала исходный вектор lds DX,old_08 mov AX,2508h int 21h mov AX,4C00h int 21n main endp ;Наш обработчик прерываний от системного таймера new_08 proc pushf ;Запишем флаги в стек call CS:old_08 ;и вызовем системный обработчик push EAX ;Сохраним используемые push ES ;регистры mov AX,40h ;Настроим ES mov ES,AX ;на область данных BIOS mov EAX,ES:6Ch;Прочитаем текущее время cmp EAX,CS:time_end ;Сравним с вычисленным jb ex ;Если меньше, на выход inc CS:flag ;Интервал истек, установим флаг ex: mov AL,20h ;Команда конца прерывания out 20h,AL ;в контроллер прерываний pop ES ;Восстановим pop EAX ;сохраненные регистры iret ;Выход из обработчика new_08 endp ;Поля данных программы old_08 dd 0 ;Для хранения исходного вектора time_int dd 18*2 ;Требуемый интервал (~2с) time_end dd 0 ;Момент истечения интервала flag db 0 ;Флаг истечения интервала msg db "Время истекло !$' ;Информационное сообщение code ends end main