- •Н.Ю. Юдина в.Н. Харин вычислительные машины, системы и сети

- •Лабораторная работа № 1 Формирование логических структур

- •Лабораторная работа № 2 Иерархическая структура памяти. Модели памяти

- •Лабораторная работа № 3 Организация управления эвм

- •1. Обработка прерываний

- •2. Управление многозадачностью

- •2. Обработка исключений

- •4. Передача управления

- •Лабораторная работа № 4 Архитектура микропроцессоров

- •Лабораторная работа № 5 Интерфейс

- •Регистровая модель процессора

- •Стандартные интерфейсы:com,usb

- •Сом-порт

- •Ресурсы и конфигурирование сом-портов

- •Последовательная шина usb

- •Лабораторная работа № 6 Телекоммуникации и сети

- •Библиографический список

- •Вычислительные машины, системы и сети

2. Управление многозадачностью

Многозадачность-это метод, с помощью которого управляют компьютерной системой, выполняющей несколько видов работ, таких как редактирование файла, компиляции программы или выполнение внутрисистемных передач. Отдельные задачи выполняются так, как если бы они выполнялись на специализированных процессорах с общей памятью. Другими словами, за исключением пауз для взаимодействия или синхронизации с другими задачами, каждая задача работает параллельно с другими задачами

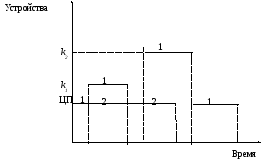

Мультипрограммирование — режим работы ЭВМ, при котором в максимальной степени используются ресурсы ЭВМ. Иллюстрацией может служить следующий пример. В ЭВМ находятся две готовые к исполнению программы. Одна из них, например, первая “захватывает” центральный процессор и начинает исполняться до момента t1, когда ей потребуется начать ввод данных с внешней памяти через канал k1. Первая программа на может работать, пока не будут введены новые данные, поэтому она освобождает центральный процессор и переходит в состояние ожидания конца обмена, а центральный процессор начинает выполнение программы 2. Когда в момент времени t2 завершится ввод данных по каналу k1 для программы 1, исполнение программы 2 прервется, и центральный процессор продолжит исполнение программы 1. В момент t3>t2 программа 1 начнет вывод данных по каналу k2, а центральный процессор продолжит исполнение программы 2 с прерванного момента. В момент t4 программа 2 завершится и центральный процессор будет простаивать до момента t5, когда закончится обмен программы 1, она начнет считаться и завершится в момент времени t6 (рис.37).

Рис.37

В этом режиме программы 1 и 2 совместно, поочередно используют общий ресурс — центральный процессор (разделяют центральный процессор). Аналогичным образом могут разделяться и другие ресурсы: каналы, оперативная память, внешние устройства, файлы на магнитных дисках.

Общая схема работы выглядит так: каждая программа, когда ей требуется некоторый ресурс (процессор, память, канал и т.д.), обращается по прерыванию к операционной системе с запросом на него. Если есть свободный ресурс и очередь программ к нему пуста, операционная система выделяет его программе и разрешает ей продолжить исполнение. А если нет—ставит программу в очередь к этому ресурсу, задерживает ее исполнение. Когда ресурс освободится, операционная система просмотрит очередь к нему, выберет одну из программ, выделит ей ресурс и разрешит исполняться. Например, если освободился канал k1, в этом случае это будет список всех канальных программ, сформированных разными из них и запустит на счет в канале k1.

2. Обработка исключений

В данном разделе рассмотрены операции вне режима нормальной обработки, связанной с выполнением инструкций. Описаны функции битов супервизорной части регистра состояния: бит супервизор/пользователь, бит разрешения трассирования и маска приоритетов прерываний. Наконец, детально описаны последовательность обращений к памяти и действия, предпринимаемые процессором в условиях исключения.

Процессор всегда находится в одном из трех состояний: нормальном, состоянии исключения и состоянии останова. Нормальное состояние процессора связано с выполнением инструкции; обращения к памяти выполняются с целью выборки инструкций и данных и сохранения результатов. Особым случаем нормального состояния является состояние приостанова, являющееся итогом выполнения инструкции STOP. В этом состоянии дальнейших обращений к памяти не производится.

Кроме того, особым случаем нормального состояния является циклический режим (loop mode) процессора MC68010, который может возникнуть при выполнении инструкций перехода (DBcc), декремента и проверки условия. В циклическом режиме происходит только выборка операндов (прил. А. Работа в циклическом режиме MC68010).

Обработка исключения связана с прерываниями, инструкциями прерывания, трассировкой и другими особыми случаями. Исключение может быть выработано внутренне инструкцией или необычным условием, возникшим во время выполнения инструкции. Извне обработку исключения вызывает прерывание, сбой шины или сброс. Обработка исключения обеспечивает эффективное переключение контекста так, что процессор может поддерживать необычные условия.

Состояние останова (halted state) процессора индицирует катастрофические сбои аппаратуры. Например, если в процессе обработки исключения сбоя шины возникает еще один сбой шины, процессор считает систему неработоспособной и останавливается. Перезапустить остановленный процессор можно только внешним сбросом. Следует заметить, что нахождение процессора в stopped state не является нахождением его в halted state, и наоборот.

Любое нарушение нормальной работы процессора приводит к ситуации, которая называется исключением (exception). Исключение могут обусловить как внутренние, так и внешние причины. Внешние причины: сигнал сброса, ошибка магистрали, прерывания; внутренние причины: адресные ошибки, результаты обработки и выполнения инструкций, трассировка. Кроме указанных могут быть дополнительные причины, связанные со спецификой их работы конкретного процессора.

Для разрешения конфликтов при одновременном возникновении двух или нескольких исключений все исключения разделены на группы по приоритетам. Внутри каждой из групп они также упорядочены по приоритетам.

Обработка исключения осуществляется подпрограммой, адрес которой процессор вычисляет, используя номера вектора исключения. Номер вектора исключения генерируется самим процессором или передается ему в цикле подтверждения прерывания.

Механизм обработки исключений включает в себя ряд операций, независимых от типа исключения:

сохранение в стеке содержимого программного счетчика и регистра состояния;

получение номера вектора исключения;

переход на подпрограмму обработки исключения, адрес которой выбирается из таблицы векторов исключений по номеру вектора.

Специфичной для разных процессоров и некоторых типов исключений является информация, сохраняемая в стеке дополнительно к содержимому программного счетчика и регистра состояния. Для различных типов исключений и процессоров существуют различные кадры стека.

Режимы привилегий

Процессор функционирует на одном из двух уровней привилегий: в режиме супервизора или режиме пользователя. Режим определяет, какие операции разрешены. Режим может быть использован внешним устройством управления памятью для управления и трансляции доступа. Режим используется и для выбора типа указателя стека супервизора (SSP) или пользователя (USP) в ссылках инструкций.

Режим привилегий является механизмом обеспечения безопасности компьютерных систем. Программы должны иметь доступ только к своим областям кода и данных. Необходимо предотвратить их доступ к информации, которая им не нужна и должна быть неизмененной. Операционная система работает в режиме супервизора, предоставляющем ей доступ ко всем ресурсам, необходимым для выполнения задач уровня, превосходящего уровень программ режима пользователя. Большинство программ выполняются в пользовательском режиме при контролируемом доступе и ограниченном влиянии на другие части системы.

Режим супервизора

Режим супервизора обладает наивысшим уровнем привилегий. Режим процессора определяется битом S регистра состояния: если он установлен, процессор находится в режиме супервизора. В этом режиме могут выполняться любые инструкции. Циклы шины, генерируемые при выполнении инструкций в режиме супервизора, классифицируются как обращения супервизора. Пока процессор находится в супервизорном режиме, SSP доступен для тех инструкций, которые используют либо системный указатель стека по умолчанию, либо явно указанное значение седьмого адресного регистра.

Режим пользователя

Режим пользователя имеет низший уровень привилегий. Процессор выполняет инструкции в режиме пользователя, если бит S регистра состояния сброшен.

Выполнение большинства инструкций не зависит от режима. Однако, некоторые важные для системы инструкции, реализованы как привилегированные. Например, программам пользователя не разрешается выполнение инструкций STOP или RESET. Чтобы не допустить переход программы пользователя в режим супервизора, кроме случая выполнения ею управляющих функций, инструкции, которые полностью изменяют регистр состояния, являются привилегированными. Для упрощения отладки системного программного обеспечения инструкции записи в указатель стека пользователя (MOVE в USP) и чтения из него (MOVE из USP) являются привилегированными.

Примечание: Концепция виртуальной машины в MC68010 реализована за счет привилегированности инструкций чтения регистра состояния (MOVE из SR), записи/чтения регистра управления (MOVEC) и установки альтернативного адресного пространства (MOVES). Шинные циклы, генерируемые при выполнении инструкций в режиме пользователя, классифицируются как обращения пользователя. Такая классификация позволяет внешнему устройству управления памятью преобразовывать адреса доступа к защищенным частям адресного пространства и управлять доступом. При нахождении процессора в режиме пользователя доступ к USP имеют те инструкции, которые используют либо по умолчанию системный указатель стека, либо явно указанное значение седьмого адресного регистра.

Изменение режима привилегий

Если процессор выполняет инструкции в режиме пользователя, изменить режим привилегий может только обработка исключения. В процессе обработки исключения текущее состояние бита S сохраняется, затем он устанавливается, переводя процессор в режим супервизора. Таким образом, когда начинается выполнение инструкции по адресу обработчика исключения, процессор находится в режиме супервизора.

Примечание: Переключиться из режима супервизора в режим пользователя можно одной из четырех инструкций: возврата из исключения (RTE) только для MC68010); записи в регистр состояния (MOVE в SR), AND непосредственно с регистром состояния (ANDI с SR) и исключающее OR непосредственно с регистром состояния (EORI с SR). По инструкции RTE в MC68010 из стека супервизора выбираются новые значения регистра состояния и программного счетчика загружаются в соответствующие регистры. Далее, процессор выбирает инструкции по новому адресу программного счетчика в режиме привилегий, определенном битом S нового содержимого регистра состояния.

По инструкциям MOVE (в SR), ANDI (с SR) и EORI (с SR) все операнды выбираются в режиме супервизора, обновляется соответствующим образом регистр состояния, и по следующему адресу программного счетчика выбирается следующая инструкция в режиме привилегий, определенному новым значением бита S.

Классификация обращений

Процессор классифицирует выполняемое обращение кодом на выходных линиях функционального кода. Это позволяет организовать внешнее преобразование адресов, управление доступом и выделение специальных циклов процессора, таких, как холостой цикл (используемый циклом подтверждения прерывания). В табл.6.1 приведена классификация обращений.

Обработка исключения происходит за четыре шага (варьирующихся в зависимости от причин исключения):

Создание временной копии регистра состояния и установка его для обработки исключения;

Получение вектора исключения;

Сохранение текущего контекста процессора;

Получение нового контекста и продолжение обработки инструкций.

Таблица 1

Классификация обращений процессора

|

Выходы функционального кода |

Тип адресного пространства | ||

|

FC2 |

FC1 |

FC0 | |

|

0 |

0 |

0 |

Неопределенно, зарезервировано |

|

0 |

0 |

1 |

Данные пользователя |

|

0 |

1 |

0 |

Программы пользователя |

|

0 |

1 |

1 |

Неопределенно, зарезервировано |

|

1 |

0 |

0 |

Неопределенно, зарезервировано |

|

1 |

0 |

1 |

Данные супервизора |

|

1 |

1 |

0 |

Программа супервизора |

|

1 |

1 |

1 |

CPU space |

Векторы исключений

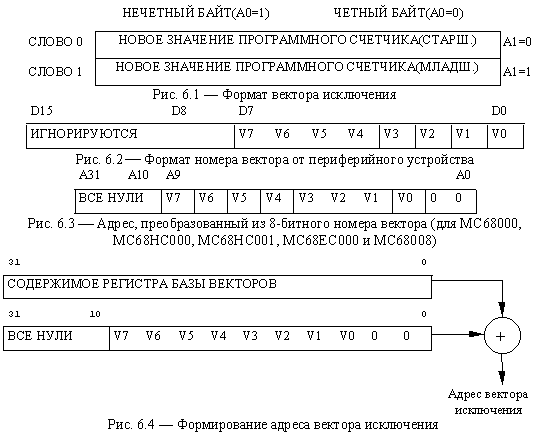

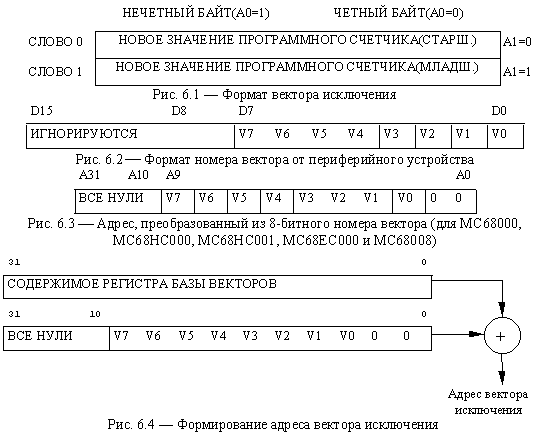

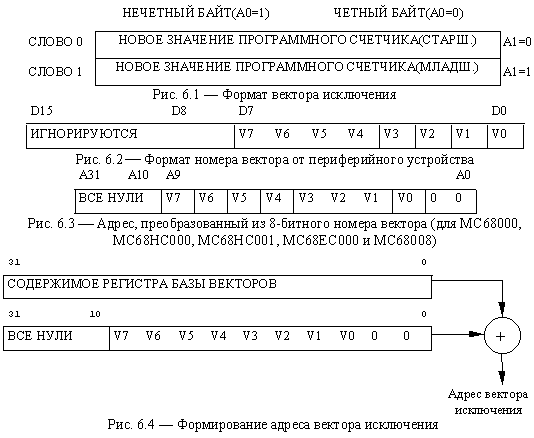

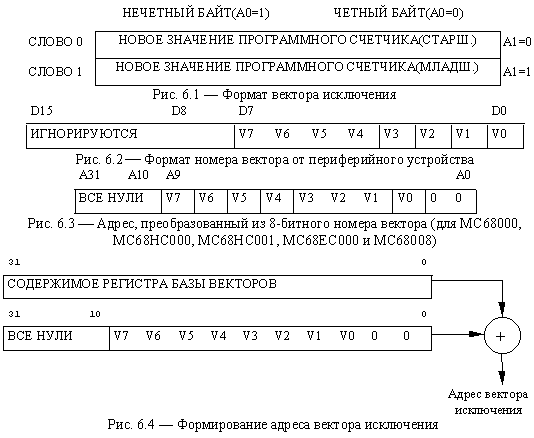

Вектор исключения – это участок памяти, откуда процессор выбирает адрес процедуры-обработчика исключения. Каждому типу исключения требуется процедура-обработчик и уникальный вектор. Все векторы исключений имеют длину два слова (рис.38), за исключением вектора сброса, имеющего длину четыре слова. Все векторы исключений расположены в области данных супервизора, за исключением вектора сброса, расположенного в программной области супервизора. Номер вектора является 8-битным числом, которое умножается на четыре для получения смещения вектора исключения. Номер вектора вырабатывается внутри процессора или вне его, в зависимости от причины исключения. Для прерываний, в цикле подтверждения прерывания периферия предоставляет процессору 8-битный номер прерывания (рис.39) на шину данных по линиям D7-D0. Процессор формирует смещение вектора, сдвигая номера вектора влево на два разряда и заполняя нулями старшие биты для получения 32-битного смещения вектора. В MC68000, MC68HC000, MC68HC001, MC68EC000 и MC68008 это смещение используется в качестве абсолютного адреса для получения самого вектора исключения (рис.40).

Примечание: В MC68010 смещение вектора прибавляется к содержимому 32-разрядного регистра базы векторов (VBR) для получения 32- битного абсолютного адреса вектора исключения (рис.41). С момента обнуления VBR по сбросу MC68010 функционирует идентично MC68000, MC68HC000, MC68HC001, MC68EC000 и MC68008 до момента, когда VBR изменяется инструкцией записи в управляющий регистр MOVEC.

Рис. 38 Формат вектора исключения

Рис. 39 Формат номера вектора от периферийного устройства

Рис. 40 Адрес, преобразованный из 8-битного номера вектора

Рис. 41 Формирование адреса вектора исключения

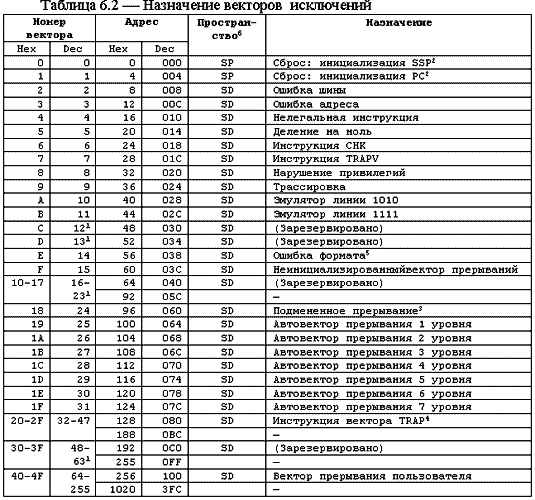

Физический адрес на шине адреса усекается до разрядности, совпадающей с количеством адресных линий в частном случае архитектуры MC68000. Во всех процессорах, кроме MC68008, разрядность шины адреса составляет 24 бита. (A0 обычно закодирован в стробах данных). В MC68008 адрес 20- или 22-битный. Карта памяти для векторов исключений показана в табл. 2. Таблица векторов имеет объем 512 слов (1024 байт), занимая область с адреса 0 до адреса 1023 (десятичного). Таблица векторов предоставляет 255 уникальных векторов; некоторые из них зарезервированы для ловушек и векторов различных системных функций. Из 255 192 зарезервированы под вектора прерываний пользователя. Однако 64 точки входа не защищены, так что векторы прерываний пользователя могут переопределяться разработчиком.

Виды исключений

Исключение может быть вызвано внешней или внутренней причиной. Внешние причины прерывания, сбои шины и сброс. Прерывания являются запросами периферийных устройств на обработку; входы сбоя шины и сброса используются для управления доступом и перезапуска процессора. Внутренние исключения генерируются инструкциями, адресными ошибками или в ходе трассировки. Ловушка (TRAP), ловушка при переполнении (TRAPV), проверка от нарушения границ (CHK) и инструкция деления (DIV) могут генерировать исключения как этап выполнения своих инструкций. Кроме того, исключения вызывают недопустимые инструкции, выборка слов по нечетным адресам и нарушение привилегий. Трассировка имитирует очень высокий уровень приоритета; внутренне генерирумое прерывание следует за каждой инструкцией.

Таблица 2

Назначение векторов исключений

Примечание: 1.Номера векторов 12, 13, 16-23 и 48-63 зарезервированы фирмой Motorola для будущих расширений. Периферийные устройства пользователя не должны их использовать;

2.Вектор сброса (0) требует четыре слова, несмотря на другие вектора, которые требуют всего 2 слова, и расположен он в программном пространстве супервизора;

3.Вектор подмененного прерывания используется, когда в процессе обработки прерывания произошел сбой шины;

4.TRAP #n использует номер вектора 32+n;

5.Только MC68010. Для MC68000 и MC68008 данный вектор не назначен;

6.SP означает программную область супервизора, SD – область данных супервизора.

Многократные исключения

Далее описан процесс обработки в случае одновременного возникновения нескольких исключений. Исключения могут быть сгруппированы по своему происхождению и приоритету. Исключения группы 0 – это сброс, сбой шины и ошибка адреса. Эти исключения приводят к прекращению выполнения текущей инструкции и началу обработки исключения в два такта синхронизации. Группу 1 представляют трассирование и прерывание, нарушение привилегий и недопустимые инструкции. Трассирование и прерывание позволяют выполнить до конца текущую инструкцию, но следующая инструкция не обрабатывается, а вызывается обработчик исключения. Инструкция с нарушением привилегий и недопустимая инструкция обнаруживаются, когда должна быть выполнена следующая инструкция. Исключения группы 2 представляют собой этап нормального выполнения инструкций. К этой группе относятся: исключения TRAP, TRAPV, CHK и деления на нуль. Для этих исключений нормальное выполнение инструкции может привести к обработке исключения.

Исключения группы 0 имеют наивысший приоритет, тогда как группа 2 – низший. В группе 0 наиболее высокий приоритет имеет сброс, далее следует ошибка адреса, а затем сбой шины. В группе 1 трассирование имеет приоритет над всеми внешними прерываниями, которые в свою очередь приоритетны по отношению к недопустимой инструкции и нарушению привилегий. Так как в любой момент времени выполняется только одна инструкция, в группе 2 отсутствуют приоритетные отношения. Отношение приоритетов между двумя исключениями определяется тем, какие исключения имели место, и какие произошли первыми при одновременном возникновении условий для них. Таким образом, если сбой шины возникает в ходе выполнения инструкции TRAP, он имеет приоритет, и выполнение TRAP прерывается. Другой пример: если происходит запрос на прерывание в процессе выполнения инструкции при выставленном бите T, трассирование имеет приоритет и обрабатывается в первую очередь. Однако, перед возобновлением выполнения инструкции, также обрабатывается исключение-прерывание, а обработка инструкций полностью начинается в процедуре обработчика прерывания. Исключения, разбитые по группам и приоритетам, приведены в табл. 3.

Основное правило: чем ниже приоритет исключения, тем скорее выполняется процедура обработчика этого исключения. Например, если одновременно ожидают обработки исключения ловушки, трассирования и прерывания, первой произойдет обработка исключения для ловушки, за ним последует обработка трассирования и затем прерывания. Когда процессор продолжит выполнение инструкций, он сперва находится в обработчике прерывания, который возвратит управление обработчику трассировки, который, в свою очередь, вернет управление обработчику исключения ловушки. Это правило не распространяется на исключение сброса; оно обрабатывается первым, даже, несмотря на то, что он имеет наивысший приоритет, потому что операция сброса устраняет все другие исключения.

Таблица 3

Группы и приоритет исключений

|

Группа |

Исключение |

Обработка |

|

0 |

Сброс Ошибка адреса Сбой шины |

Обработка исключения за два такта синхронизации |

|

1 |

Трассирование Прерывание Недопустимая инструкция |

Обработка исключения перед выполнением следующей инструкции |

|

2 |

TRAP, TRAPV, CHK, деление на нуль |

Обработка исключения начинается выполнением обычной инструкции |

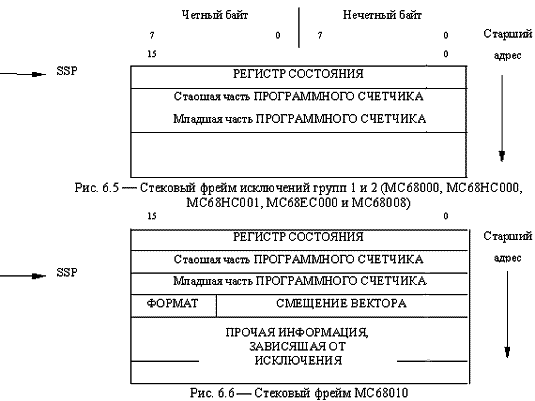

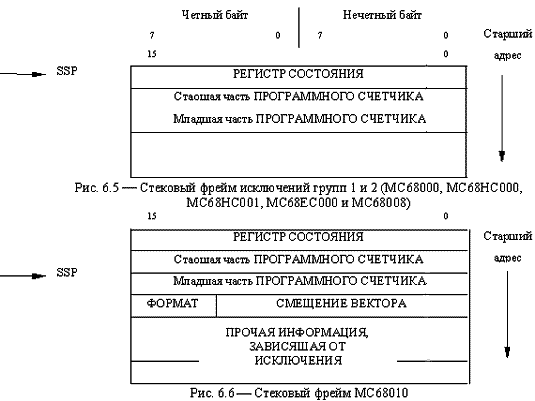

Стековые фреймы исключений

При обработке исключений наиболее непостоянная часть контекста процессора сохраняется в вершине стека супервизора. Этот контекст организован в формате, называемом стековым фреймом исключения (Exception Stack Frame). Хотя эта информация варьируется в зависимости от процессора или типа исключения, она всегда отражает содержимое регистра состояния и программный счетчик процессора, когда происходит исключение.

Количество и тип информации, заносимой в стек, определяется типом процессора и видом исключения. Исключения группируются по типу согласно своему приоритету.

Последовательность обработки исключения

Рис. 42 Стековый фрейм исключений групп 1 и 2

Рис. 43 Стековый фрейм

На первом шаге обработки исключения создается внутренняя копия регистра состояния. После этого устанавливается бит S регистра состояния, и процессор переключается в режим супервизора. Сбрасывается бит T, обеспечивающий при трассировании беспрепятственное выполнение обработчика исключения. Также для исключений сброса и прерывания соответствующим образом обновляется маска приоритетов прерываний (interrupt priority mask).

На втором шаге определяется номер вектора исключения. Для прерываний процессор получает номер вектора в шинном цикле, классифицируемом как цикл подтверждения прерывания. Для остальных исключений номер вектора обеспечивает внутренняя логика. Далее этот номер используется для вычисления адреса вектора исключения.

Третий шаг необходим для сохранения регистра состояния (это не касается исключения, т.к. при нем контекст не запоминается). Текущее значение программного счетчика и сохраненная копия регистра состояния заносятся в стек с использованием SSP. Сохраненное в стеке значение программного счетчика обычно указывает на следующую невыполненную инструкцию. Однако для сбоя шины и ошибки адреса сохраненное значение непредсказуемо и может быть результатом инкремента адреса инструкции, вызвавшей ошибку. Исключения группы 1 и 2 используют короткий формат стекового фрейма исключения. Дополнительная информация, определяющая текущий контекст, сохраняется в стеке для исключений по сбою шины и ошибке адреса. Последний шаг одинаков для всех исключений. Из вектора исключения считывается новое значение программного счетчика. Затем процессор возобновляет выполнение инструкции: инструкция выбирается по адресу, находящемуся в векторе исключения, и начинается декодирование и выполнение обычных инструкций

Исключения классифицируются в зависимости от их источников и каждый тип обрабатывается по-разному. В данном подразделе детально описаны типы исключений и процесс обработки каждого типа.

Сброс

Исключение по сбросу соответствует самому высокому уровню исключений. Обработка исключения по сбросу выполняется с целью системной инициализации и восстановления после катастрофических сбоев. Любая текущая операция прерывается во время сброса и не может быть восстановлена. Процессор переходит в режим супервизора и отключает режим трассирования. В маске приоритетов прерываний устанавливается уровень 7. Внутренне формируется номер вектора для ссылки на вектор исключения по нулевому адресу в области программ супервизора. Так как не гарантирована достоверность содержимого регистров, в особенности SSP, то ни программный счетчик, ни регистр состояния не сохраняются. Адрес в первых двух словах вектора исключения по сбросу выбирается как начальный SSP, а адрес в последних двух словах вектора – как начальное значение программного счетчика (оно должно указывать на код процедуры включения/перезапуска).

Инструкция RESET не вызывает исключения по сбросу; по ней генерируется сигнал RESET# для сброса внешних устройств, который позволяет программным путем перевести в известное состояние сброса и продолжить обработку следующей инструкции.

Прерывания

Для прерываний применимы семь уровней приоритета (от 1 до 7). Уровень 7 имеет самый высокий приоритет.

Устройства могут быть внешне объединены в приоритетную цепочку, позволяющую неограниченному числу периферийных устройств прерывать процессор. Регистр состояния содержит трехбитную маску, показывающую текущий приоритет. Прерывания с уровнем приоритета равным или ниже текущего уровня, запрещаются.

Запрос на прерывание посылается процессору путем установления кода уровня 1-7 на трех линиях запроса прерывания; если все линии неактивны, то это означает отсутствие запроса на прерывание. Запросы на прерывание, поступающие в процессор, не приводят к немедленной обработке исключения, а становятся ожидающими. Ожидающие прерывания распознаются в промежутке между выполнением инструкций.

Если приоритет ожидающего прерывания ниже или равен текущему приоритету процессора, продолжается выполнение следующей инструкции, а обработка исключения откладывается до тех пор, пока приоритет ожидающего прерывания не станет выше текущего приоритета процессора. Если приоритет ожидающего прерывания выше текущего приоритета процессора, начинается последовательность обработки исключения. Сохраняется копия регистра состояния, устанавливается режим привилегий супервизора. Трассирование прекращается, а уровень приоритета процессора устанавливается равным уровню приоритета подтвержденного прерывания. Процессор принимает от прерывающего устройства номер вектора, выполняя цикл подтверждения прерывания. Если внешняя логика запрашивает автоматический вектор, процессор внутренне генерирует номер вектора в соответствии с номером уровня прерывания. Если внешняя логика индицирует сбой шины, прерывание считается подмененным, и сформированный номер вектора указывает на подмененный вектор прерывания. Далее процессор осуществляет обычную обработку исключения, сохранив слово формата/смещения, программный счетчик и регистр состояния в стеке супервизора. Величина смещения в слове формата/смещения определяется как номер вектора, умноженный на четыре. Формат всегда содержит все нули. Сохраненное значение программного счетчика это адрес инструкции, которая была бы выполнена в случае непринятия прерывания. Соответствующий вектор прерывания выбирается и загружается в программный счетчик, выполнение обычных инструкций продолжается в процедуре обработчика прерывания. Приоритетный уровень 7 является особым случаем. Прерывания этого уровня 7 нельзя запретить установкой маски; таким образом, имеется в распоряжении немаскируемое прерывание. Прерывание происходит всякий раз, когда изменяется уровень запроса прерывания с некоторого более низкого до наивысшего уровня 7. Прерывание уровня 7 может быть вызвано и в случае, если уровень запроса равен 7, а инструкцией установлен более низкий приоритет процессора.

Неинициализированное прерывание

Прерывающее устройство выставляет для MC68000 номер вектора прерывания и выдает сигнал подтверждения передачи данных DTACK#, либо сигнал достоверности периферийного адреса VPA#, либо автовектор AVEC#, либо сигнал сбоя шины BERR# в цикле подтверждения прерывания. Если регистр вектора не был проинициализирован, соответствующее периферийное устройство семейства предоставляет номер вектора 15 ("неинициализированный вектор прерывания"). Этот ответ означает единственный способ восстановления от программной ошибки.

Переопределенное прерывание

В цикле подтверждения прерывания, если ни одно устройство не отвечает активизацией DTACK# или AVEC#, или VPA#, должен быть выдан BERR# для прекращения получения вектора. Обработка процессором этой ошибки отличается от обработки сбоя шины формированием стека исключения короткого формата и выборкой переопределенного вектора прерывания вместо вектора сбоя шины. Далее процессор в обычном порядке обрабатывает исключение.

Программные ловушки

Ловушки – это исключения, причиной которых являются инструкции. Они происходят, когда процессор распознает ненормальные условия при выполнении инструкции, или в результате прерывания после нормального выполнения инструкции нормально прерывается в течение выполнения.

Обработка исключений для ловушек прямолинейна. Делается копия регистра состояния, процессор входит в режим супервизора, отключается трассирование. Номер вектора формируется внутренне; для инструкции TRAP часть номера вектора получается из самой инструкции. Слово формата/смещения, программный счетчик и копия регистра состояния сохраняются в стеке супервизора. Величина смещения в слове формата/смещения определяется умножением номера вектора на четыре. Сохраненная копия программного счетчика – это адрес инструкции, следующей за инструкцией, генерируемой ловушкой. Выполнение инструкций продолжается по адресу в векторе исключения.

Некоторые инструкции применяют по-особому для генерации ловушек. Инструкция TRAP всегда вызывает исключение и используется для системных вызовов в программах пользователя. Инструкции TRAPV и CHK вызывают исключения, если программа обнаруживает ошибку выполнения, которая может быть арифметическим переполнением либо выходом за границы. Инструкции знакового (DIVS) и беззнакового (DIVU) деления вызывают исключение при попытке деления на нуль.

Недопустимые и невыполнимые инструкции

Недопустимая инструкция – это термин, обозначающий какой-либо битовый шаблон слова, который не соответствует битовому шаблону первого слова допустимой инструкции. При выборке такой инструкции возникает исключение по недопустимой инструкции. Компания Motorola оставила за собой право на определение инструкций с использованием операционных кодов любых допустимых инструкций. Три битовых шаблона всегда приводят к ловушке недопустимой инструкции во всех процессорах. Этими шаблонами являются $4AFA, $4AFB, $4AFC. Двое из них, $4AFA и $4AFB зарезервированы для системных продуктов Motorola. Третий, $4AFC, зарезервирован для нужд пользователя (таких, как ведение команды ловушки недопустимой инструкции (ILLEGAL) ).

Шаблоны слов с установленными в 1010 или 1111 битами 15-12 трактуются как невыполнимые инструкции, и с целью эффективной эмуляции этим шаблонам соответствуют отдельные векторы исключений. Коды операций, начинающиеся с 1111 (линия F), имеются и определяют инструкции сопроцессора. Эти вектора позволяют операционной системе программно эмулировать невыполнимые инструкции.

Обработка исключений по недопустимым инструкциям подобна обработке исключений ловушек. После выборки инструкции и попытки декодирования процессор определяет, что была предпринята попытка выполнения недопустимой инструкции, и начинает обработку исключения. Затем стековый фрейм исключений для группы 2 помещается в стек супервизора, и выбирается вектор недопустимой инструкции.

Нарушение привилегий

Различные привилегированные инструкции обеспечивают системную безопасность. Попытка выполнить привилегированную инструкцию в режиме пользователя приводит к исключению. Привилегированными инструкциями являются:

Обработка исключения по нарушению привилегий сходна с обработкой недопустимой инструкции. Когда инструкция выбрана и декодирована, а процессор распознает попытку нарушения привилегий, он начинает обработку исключения. Формируется копия регистра состояния, процессор переходит в супервизорный режим, трассирование отключается. Для обращения к вектору нарушения привилегий генерируется номер вектора, а программный счетчик и копия регистра состояния сохраняются в стеке супервизора. Сохраненная копия программного счетчика является адресом первого слова инструкции, вызвавшей нарушение привилегий. Выполнение инструкций начинается с адреса, находящегося в векторе исключения по нарушению привилегий.

Трассирование

Трассированием управляет бит T в супервизорной части регистра состояния. Если бит T сброшен (выключен), трассирование недоступно, и происходит нормальная обработка от инструкции к инструкции. Если бит Т установлен (включен) в начале выполнения инструкции, исключение по трассированию возникает после завершения каждой инструкции. Если инструкция не была выполнена из-за того, что она недопустима, или из-за нарушения привилегий, исключение по трассированию не происходит. Исключение по трассированию также не произойдет, если инструкция прервана сбросом, сбоем шины или ошибкой адреса. Если инструкция выполнена и по завершении имеется ожидающее прерывание, перед обслуживанием прерывания обрабатывается исключение по трассированию. Если в ходе выполнения инструкции происходит исключение, вызванное этой инструкцией, обработка этого исключения предшествует обработке исключения по трассированию.

В качестве примера экстремальной ситуации, иллюстрирующей эти правила, можно рассмотреть случай, когда приходит запрос на прерывание во время выполнения инструкции TRAP при включенном трассировании. Сначала обрабатывается исключение ловушки, затем исключение по трассированию, и, наконец, обработка прерывания. Выполнение инструкций продолжается в процедуре обслуживания прерывания.

После выполнения инструкции перед началом следующей инструкции начинается обработка исключения по трассированию. Создается копия регистра состояния, процессор переводится в супервизорный режим, а бит Т регистра состояния сбрасывается, отменяя дальнейшее трассирование. Для ссылки на вектор трассирования генерируется номер вектора, а текущее значение программного счетчика и копия регистра состояния сохраняются в стеке супервизора. В стеке супервизора также сохраняется слово формата/смещения. Выполнение инструкций начинается по адресу, находящемуся в векторе исключения по трассированию.

Сбой шины

Исключение по сбою шины происходит, когда внешняя логика запрашивает обработку сбоя шины исключением. Текущий шинный цикл прерывается. Текущая работа процессора прерывается, и он немедленно приступает к обработке исключения. Средства обработки сбоя шины идентичны во всех процессорах; однако в стековом фрейме MC68010 содержится большее количество информации. Больший стековый фрейм обеспечивает продолжение выполнение инструкции, поддерживая виртуальную память.

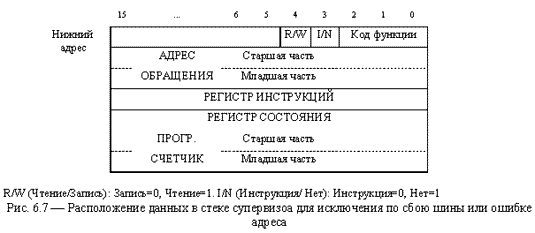

Обработка исключения по сбою шины проводится в обычном порядке. Формируется копия регистра состояния, процессор переводится в режим супервизора, трассирование отключается. Для ссылки на вектор сбоя шины генерируется номер вектора. С этапа выборки инструкции или операнда, когда произошел сбой шины, контекст процессора более подробный. Для запоминания этого контекста дополнительная информация (значение программного счетчика и копия регистра состояния) сохраняется в супервизорной части стека. Содержимое программного счетчика расположено за 2-10 байт от адреса первого слова инструкции, которая совершила сбой шины при обращении. Если сбой происходит в процессе выборки следующей инструкции, сохраняемое значение программного счетчика находится недалеко от текущей инструкции, которая может быть даже инструкцией перехода, ветвления или возврата. Помимо обычной информации процессор делает внутреннюю копию первого слова инструкции, которая выполнялась, и адреса, по которому производилось обращение в прерванном цикле. Также сохраняется специфическая информация о доступе, типе доступа (чтение или запись), работе процессора (обработке инструкции) и выходах кода функции в момент сбоя шины. Процессор выполняет инструкцию, если он в нормальном режиме обрабатывает исключение группы 2; процессор не выполняет инструкцию при обработке исключений группы 1 или 0. На рис.6.7 показано содержимое стека супервизора. Если сбой шины возникает на последнем шаге обработки исключения, т.е. либо во время чтения вектора исключения, либо в процессе выборки инструкции, программный счетчик принимает значение адреса вектора исключения. Хотя этой информации не совсем достаточно для полного восстановления после сбоя шины, становится возможной программная диагностика. Процедура обработки исключения отвечает за очистку стека и определение порядка дальнейшего выполнения.

Если сбой шины происходит во время обработки исключения по сбою шины, ошибке адреса или по сбросу, процессор останавливается и всякая обработка прекращается. Такой останов упрощает обнаружение катастрофических сбоев системы, и с этого момента процессор "удаляет" себя из системы, чтобы защитить память от ошибочного обращения. Перезапустить остановленный (halted) процессор можно только внешним сбросом.

Рис. 44 Расположение данных в стеке супервизора для исключения по сбою шины или ошибке адреса

Ошибка адреса

Исключение по ошибке адреса возникает, когда процессор пытается обратиться к операнду длиной слово, длинное слово или к инструкции по нечетному адресу. Ошибка адреса подобна внутренне генерируемому сбою шины. Шинный цикл прекращается, процессор прекращает текущую обработку и начинает обработку исключения. Последовательность обработки исключения та же, что и при исключении по сбою шины, включая информацию о стеке. Однако номер вектора указывает на вектор ошибки адреса. Кроме того, когда ошибка адреса происходит во время обработки сбоя шины, ошибки адреса или сброса, процессор останавливается.

В процессоре MC68010 при исключении по ошибке адреса в стеке сохраняется та же информация, что и при исключении по сбою шины. Поэтому инструкция RTE может быть использована для продолжения выполнения отложенной инструкции. Однако, если флаг RR не установлен, при повторении цикла применяется адрес ошибки, и возникает другое исключение по ошибке адреса. Значит, перед продолжением инструкции пользователь должен быть уверен в том, что внесены поправки в образ стека и регистры пользователя. Если необходимо, то при корректной программной поддержке обработчик исключения по ошибке адреса может эмулировать доступ к слову или длинному слову по нечетному адресу.

Возврат из исключения

В дополнение к возврату из процедуры обработчика исключения, инструкция RTE продолжает выполнение отложенной инструкции, возвращая режим нормальной обработки после восстановления временных регистров и управляющей информации, сохраненной во время сбоя шины. Для правильной работы RTE стек должен содержать достоверные и доступные данные. Инструкция RTE проверяет достоверность данных двумя путями: проверкой слова формата/смещения на допустимость кода формата стека или, если код формата индицирует длинный формат стека, достоверность стека проверяется при загрузке в процессор. Кроме того, данные проверяются на доступность, когда процессор начинает чтение длинных данных. Для этих проверок инструкция RTE производит следующее:

Определяет формат стека. Этот шаг одинаков для всех форматов стека и включает чтение регистра состояния, программного счетчика и слова формата/смещения. Если формат кода показывает короткий формат стека, выполнение продолжается по новому содержимому программного счетчика. Если код формата не является кодом данного формата, начинается обработка исключения для ошибки формата.

Определяет достоверность данных. Для длинного формата стека начинается чтение из стека оставшихся данных, проверяя их достоверность. Единственным словом, проверяемым на достоверность, является первое из 16 внутренних информационных слов (SP+26). Это слово содержит номер версии (в битах 10-13) и конкретную внутреннюю информацию, соответствующую номеру данной версии, пытавшейся прочесть данные. Эта проверка на достоверность должна гарантировать, что данные правильно интерпретированы инструкцией RTE. Если номер версии неверный для данного процессора, инструкция RTE прерывается и начинается обработка исключения по нарушению формата. С этого момента указатель стека не обновляется до тех пор, пока инструкция RTE успешно не прочитает все данные стека; при ошибке формата, возникающей в этой точке, новые данные не записываются поверх информации стека о предыдущем сбое шины.

Определяет доступность данных. Если данные длинного стека доступны, выполняется чтение последнего слова (SP+56) длинного стека для определения доступности данных. Если чтение завершилось нормально, процессор предполагает, что оставшиеся слова в стековом фрейме также доступны. Если обнаружен сбой шины перед или во время этого чтения, имеет место исключение сбоя шины. После этого чтения процессор должен иметь возможность загрузить оставшиеся данные без сбоя шины; таким образом, если сбой шины возникает при чтении оставшейся части стека, сбой становится двойным отказом шины, и входит в состояние останова (Halted state)