- •Н.Ю. Юдина в.Н. Харин вычислительные машины, системы и сети

- •Лабораторная работа № 1 Формирование логических структур

- •Лабораторная работа № 2 Иерархическая структура памяти. Модели памяти

- •Лабораторная работа № 3 Организация управления эвм

- •1. Обработка прерываний

- •2. Управление многозадачностью

- •2. Обработка исключений

- •4. Передача управления

- •Лабораторная работа № 4 Архитектура микропроцессоров

- •Лабораторная работа № 5 Интерфейс

- •Регистровая модель процессора

- •Стандартные интерфейсы:com,usb

- •Сом-порт

- •Ресурсы и конфигурирование сом-портов

- •Последовательная шина usb

- •Лабораторная работа № 6 Телекоммуникации и сети

- •Библиографический список

- •Вычислительные машины, системы и сети

Федеральное агентство по образованию

Государственное образовательное учреждение

высшего профессионального образования

«Воронежская государственная лесотехническая академия»

Н.Ю. Юдина в.Н. Харин вычислительные машины, системы и сети

Лабораторный практикум

Воронеж 2009

У ДК

681.3

ДК

681.3

Ю16

Печатается по решению учебно-методического совета ГОУ ВПО «ВГЛТА» (протокол № 1 от 25 сентября 2009 г.)

Рецензенты: кафедра инновационных систем информатизации

и безопасности ВИВТ,

проректор по научной работе, заведующий кафедрой ИС ВИВТ, профессор, заслуженный работник высшей школы РФ Ю.С. Сербулов

Юдина, Н. Ю.

Ю16 Вычислительные машины, системы и сети [Текст] : лаб. практикум / Н. Ю. Юдина, В. Н. Харин ; Фед. агентство по образованию, ГОУ ВПО «ВГЛТА».– Воронеж, 2009. – 175 с.

ISBN 978-5-7994-0393-5 (в обл.)

Данный лабораторный практикум состоит из 6 работ.

Предназначен для студентов специальности 220301 – Автоматизация технологических процессов и производств (лесной комплекс).

Табл. 8. Ил. 75. Библиогр.: 10 наим.

УДК 681.3

© Юдина Н. Ю., Харин В.Н., 2009

ISBN 978-5-7994-0393-5 © ГОУ ВПО «Воронежская государственная

лесотехническая академия», 2009

ОГЛАВЛЕНИЕ

ЛАБОРАТОРНАЯ РАБОТА № 1 3

Формирование логических структур 3

ЛАБОРАТОРНАЯ РАБОТА № 2 16

Иерархическая структура памяти. Модели памяти 16

ЛАБОРАТОРНАЯ РАБОТА № 3 26

Организация управления ЭВМ 26

ЛАБОРАТОРНАЯ РАБОТА № 4 74

Архитектура микропроцессоров 74

ЛАБОРАТОРНАЯ РАБОТА № 5 97

Интерфейс 97

Регистровая модель процессора 106

Стандартные интерфейсы: COM, USB 108

СОМ-порт 112

Ресурсы и конфигурирование СОМ-портов 119

Последовательная шина USB 129

ЛАБОРАТОРНАЯ РАБОТА № 6 140

Телекоммуникации и сети 140

Библиографический список 176

Лабораторная работа № 1 Формирование логических структур

Логическим элементом называется электрическая схема, выполняющая какую-либо логическую операцию (операции) над входными данными, заданными в виде уровней напряжения, и возвращающая результат операции в виде выходного уровня напряжения. Так как операнды логических операций задаются в двоичной системе счисления, то логический элемент воспринимает входные данные в виде высокого и низкого уровней напряжения на своих входах. Соответственно, высокий уровень напряжения (напряжение логической 1) символизирует истинное значение операнда, а низкий (напряжение логического 0) - ложное. Значения высокого и низкого уровней напряжения определяются электрическими параметрами схемы логического элемента и одинаковы как для входных, так и для выходных сигналов. Обычно, логические элементы собираются как отдельная интегральная микросхема. К числу логических операций, выполняемых логическими элементами, относятся конъюнкция (логическое умножение, И), дизъюнкция (логическое сложение, ИЛИ), отрицание (НЕ) и сложение по модулю 2 (исключающее ИЛИ). Рассмотрим основные типы логических элементов.

Математической основой цифровой электроники и вычислительной техники является алгебра логики или булева алгебра (по имени английского математика Джона Буля).

В булевой алгебре независимые переменные или аргументы (X) принимают только два значения: 0 или 1. Зависимые переменные или функции (Y) также могут принимать только одно из двух значений: 0 или 1. Функция алгебры логики (ФАЛ) представляется в виде:

Y = F (X1; X2; X3 ... XN ).

Данная форма задания ФАЛ называется алгебраической.

Основными логическими функциями являются:

1. логическое отрицание (инверсия)

Y

=

![]() ;

;

2. логическое сложение (дизьюнкция)

Y = X1 + X2 или Y = X1 V X2 ;

3. логическое умножение (коньюнкция)

Y = X1 · X2 или Y = X1 L X2 .

К более сложным функциям алгебры логики относятся:

1. функция равнозначности (эквивалентности)

Y

= X1 ·

X2 +

![]() или Y = X1 ~

X2 ;

или Y = X1 ~

X2 ;

2. функция неравнозначности (сложение по модулю два)

Y

= X1 ·

![]() +

+![]() ·

X2 или Y

= X1

·

X2 или Y

= X1

![]() X2 ;

X2 ;

3. функция Пирса (логическое сложение с отрицанием)

Y

=

![]() ;

;

4. функция Шеффера (логическое умножение с отрицанием)

Y

=

![]() ;

;

Для булевой алгебры справедливы следующие законы и правила:

- распределительный закон

X1 (X2 + X3) = X1 · X2 + X1 · X3 ,

X1 + X2 · X3 = (X1 + X2) (X1 + X3) ;

- правило повторения

X · X = X , X + X = X ;

- правило отрицания

X

·

![]() = 0 , X +

= 0 , X +![]() = 1 ;

= 1 ;

- теорема де Моргана

![]() =

=![]() ,

,![]() =

=![]() ;

;

- тождества

X · 1 = X , X + 0 = X , X · 0 = 0 , X + 1 = 1.

Схемы, реализующие логические функции, называются логическими элементами. Основные логические элементы имеют, как правило, один выход (Y) и несколько входов, число которых равно числу аргументов (X1;X2;X3 ... XN ). На электрических схемах логические элементы обозначаются в виде прямоугольников с выводами для входных (слева) и выходных (справа) переменных. Внутри прямоугольника изображается символ, указывающий функциональное назначение элемента.

На рис.1 ¸ 10 представлены логические элементы, реализующие рассмотренные ранее функции. Там же представлены так называемые таблицы состояний или таблицы истинности, описывающие соответствующие логические функции в двоичном коде в виде состояний входных и выходных переменных. Таблица истинности является также табличным способом задания ФАЛ.

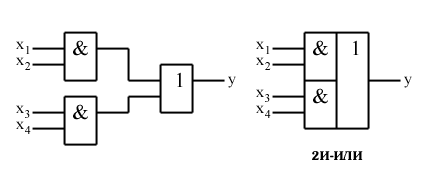

На

рис.1 представлен элемент “НЕ”,

реализующий функцию логического

отрицания Y =

![]() .

.

Рис. 1

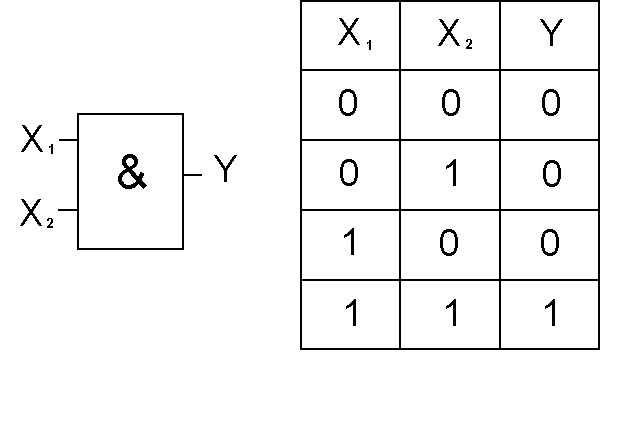

Элемент “ИЛИ” (рис.2) и элемент “И” (рис.3) реализуют функции логического сложения и логического умножения соответственно.

Рис. 2

Рис. 3

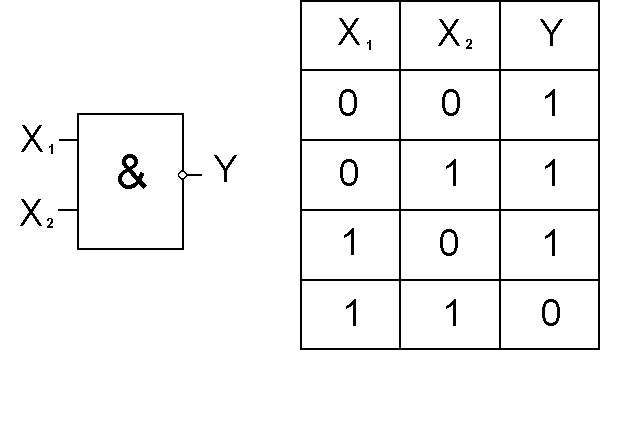

Функции Пирса и функции Шеффера реализуются с помощью элементов “ИЛИ-НЕ” и “И-НЕ”, представленных на рис.4 и рис. 5 соответственно.

Рис. 4

Рис. 5

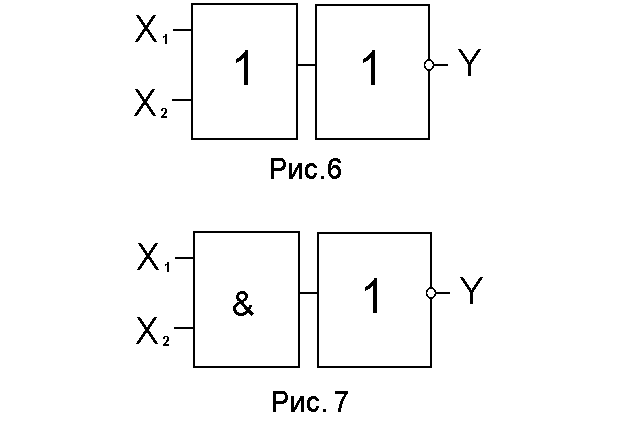

Элемент Пирса можно представить в виде последовательного соединения элемента “ИЛИ” и элемента “НЕ” (рис.6), а элемент Шеффера - в виде последовательного соединения элемента “И” и элемента “НЕ” (рис.7).

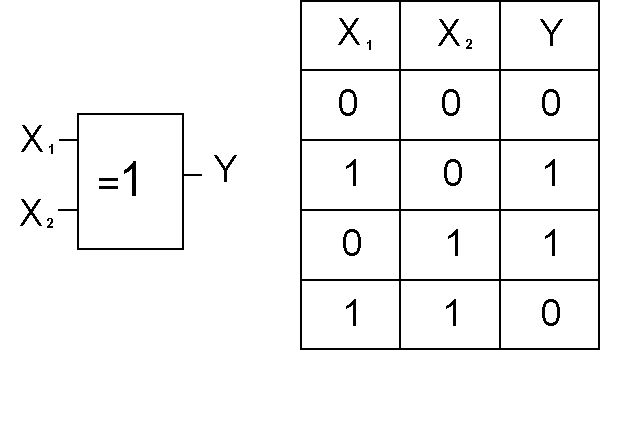

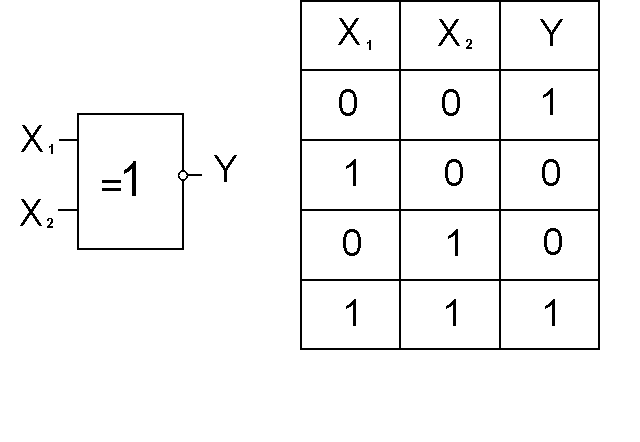

На рис.8 и рис.9 представлены элементы “Исключающее ИЛИ” и “Исключающее ИЛИ - НЕ”, реализующие функции неравнозначности и неравнозначности с отрицанием соответственно.

Рис. 8

Рис. 9

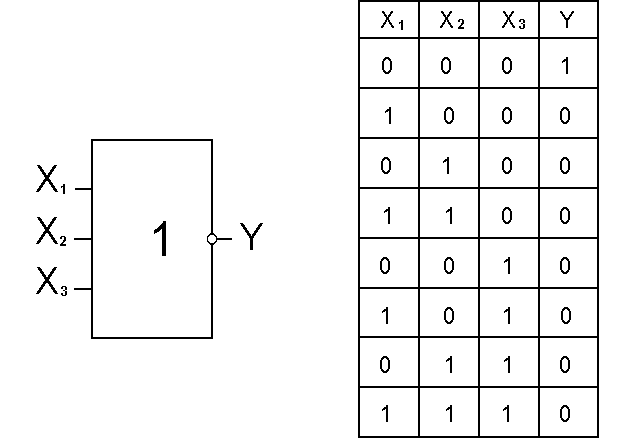

Логические элементы, реализующие операции коньюнкции, дизьюнкции, функции Пирса и Шеффера, могут быть, в общем случае, n - входовые. Так, например, логический элемент с тремя входами, реализующий функцию Пирса, имеет вид, представленный на рис.10.

Рис.10

В таблице истинности (рис.10) в отличие от таблиц в п.2.4. имеется восемь значений выходной переменной Y. Это количество определяется числом возможных комбинаций входных переменных N, которое, в общем случае, равно: N = 2 n , где n - число входных переменных.

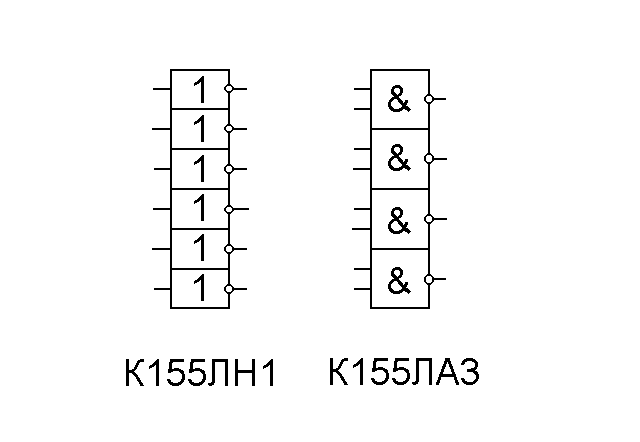

Логические элементы используются для построения интегральных микросхем, выполняющих различные логические и арифметические операции и имеющих различное функциональное назначение. Микросхемы типа К155ЛН1 и К155ЛА3, например, имеют в своем составе шесть инверторов и четыре элемента Шеффера соответственно (рис.11), а микросхема К155ЛР1 содержит элементы разного вида (рис.12).

Рис. 11

Рис. 12

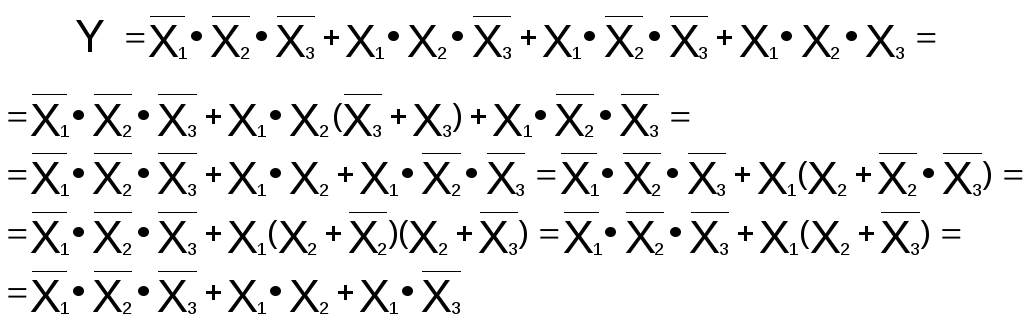

ФАЛ любой сложности можно реализовать с помощью указанных логических элементов. В качестве примера рассмотрим ФАЛ, заданную в алгебраической форме, в виде:

![]() .

(1)

.

(1)

Упростим данную ФАЛ, используя вышеприведенные правила. Получим:

(2)

(2)

Проведенная операция носит название минимизации ФАЛ и служит для облегчения процедуры построения функциональной схемы соответствующего цифрового устройства.

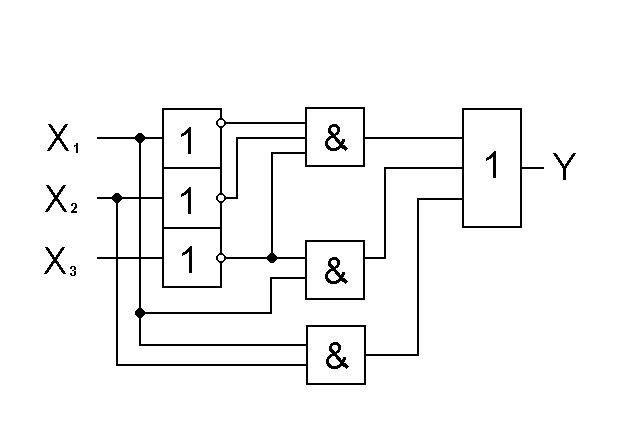

Функциональная схема устройства, реализующая рассматриваемую ФАЛ, представлена на рис.13.

Рис. 13

Следует отметить, что полученная после преобразований функция (2) не является полностью минимизированной. Полная минимизация функции проводится в процессе выполнения лабораторной работы.

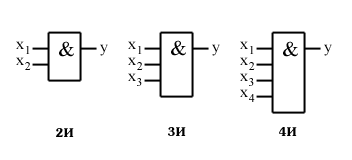

Элемент И

Логический элемент «И» выполняет операцию логического умножения (конъюнкция) над своими входными данными и имеет от 2 до 8 входов и один выход (как правило, выпускаются элементы с двумя, тремя, четырьмя и восемью входами). На рис. 14. изображены условные графические обозначения (УГО) логических элементов И с двумя, тремя и четырьмя входами соответственно. Элементы И обозначаются как NИ, где N - количество входов логического элемента (например, 2И, 3И, 8И и т.д.).

|

|

|

Рис. 14 |

Элемент ИЛИ

Логический элемент ИЛИ выполняет операцию логического сложения (дизъюнкция) над своими входными данными и, также как и логический элемент И, имеет от 2 до 8 входов и один выход. На рис. 15. изображены УГО логических элементов ИЛИ с двумя, тремя и четырьмя входами соответственно. Элементы ИЛИ обозначаются также, как и элементы И (2ИЛИ, 4ИЛИ и т.д.).

|

|

|

Рис. 15 |

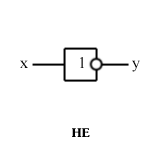

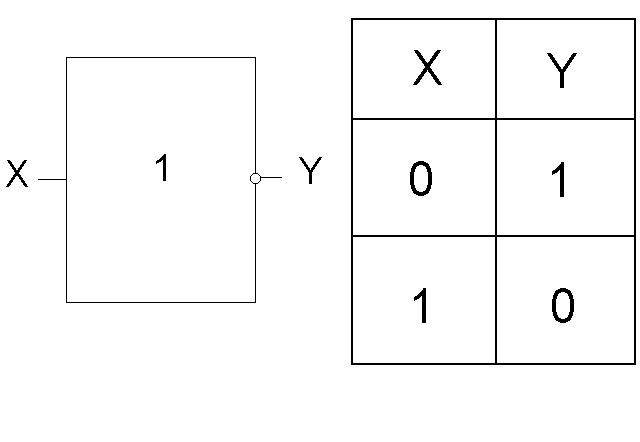

Элемент НЕ (инвертор)

Логический элемент НЕ выполняет операцию логического отрицания над своими входными данными и имеет один вход и один выход. Иногда его называют инвертор, так как он инвертирует входной сигнал. На рис. 16 изображено УГО элемента НЕ.

|

|

|

Рис. 16 |

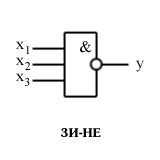

Элемент И-НЕ

Логический элемент И-НЕ выполняет операцию логического умножения над своими входными данными, а затем инвертирует (отрицает) полученный результат и выдаёт его на выход. Таким образом, можно сказать, что логический элемент И-НЕ - это элемент И с инвертором на выходе. УГО элемента 3И-НЕ приведено на рис. 17.

|

|

|

Рис. 17 |

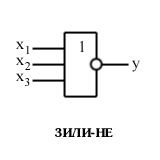

Элемент ИЛИ-НЕ

Логический элемент ИЛИ-НЕ выполняет операцию логического сложения над своими входными данными, а затем инвертирует (отрицает) полученный результат и выдаёт его на выход. Таким образом, можно сказать, что логический элемент ИЛИ-НЕ - это элемент ИЛИ с инвертором на выходе. УГО элемента 3ИЛИ-НЕ приведено на рис. 18.

|

|

|

Рис. 18 |

Элемент сложения по модулю 2

Этот логический элемент выполняет логическую операцию сложения по модулю 2 и, как правило, имеет 2 входа и один выход. Такой элемент, в основном, используется в схемах аппаратного контроля. УГО элемента приведено на рис. 19.

|

|

|

Рис. 19 |

Комбинационные логические элементы

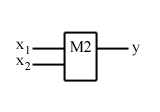

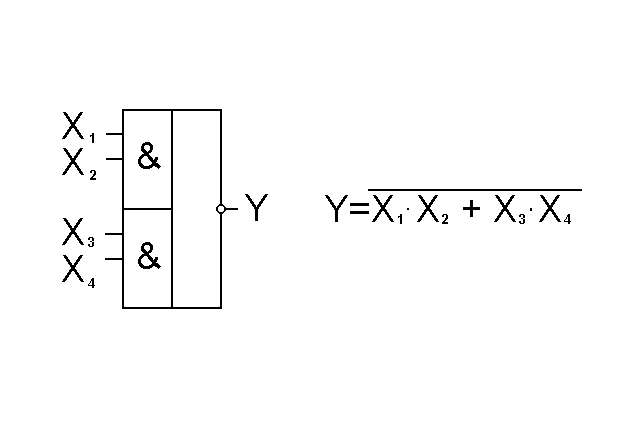

Существуют и более сложные логические элементы, выполняющие несколько логических операций над своими входными данными. Например, элемент 2И-ИЛИ, УГО и схема которого приведено на рис. 20, сначала выполняет операцию логического умножения над парами операндов x1, x2 и x3, x4, а затем выполняет операцию логического сложения над полученными результатами, т.е. y = x1x2 + x3x4. Можно придумать и более сложные комбинационные логические элементы, например 3-2И-ИЛИ-НЕ (рис. 21).

|

| |

|

Рис. 20 | |

|

|

|

|

Рис. 21 |

|

Универсальные логические элементы

Универсальные логические элементы могут использоваться для выполнения разнообразных операций над своими входными данными. Конкретная операция зависит от того, какие сигналы поданы на управляющие входы. Чтобы синтезировать такой универсальный логический элемент, обычно пользуются СКНФ или СДНФ, как и в синтезе комбинационных логических схем.

Электрические принципиальные схемы логических элементов

При рассмотрении электрических принципиальных схем логических элементов пользуются термином тип логики. Тип логики определяет элементную базу, на которой собран логический элемент, а также отражает некоторые особенности отдельных элементов этой элементной базы и характеристики самого логического элемента. Наиболее распространены следующие типы логик: ТТЛ, ДТЛ, МОП, КМОП, также существуют типы логик ЭСЛ, РЕТЛ и некоторые другие. Тип логики ТТЛ (транзисторно-транзисторная логика) определяет элементную базу, на которой собран логический элемент, как состоящую преимущественно из транзисторов, причём транзисторы используются и на входе, и на выходе логического элемента (отсюда и название - транзисторно-транзисторная). Тип логики ДТЛ (диодно-транзисторная логика) определяет элементную базу как состоящую преимущественно из транзисторов и диодов (диоды на входе, транзисторы - на выходе). Типы логик МОП (металл-оксид-полупроводник) и КМОП определяет элементную базу как состоящую из транзисторов МДП (металл-диэлектрик-полупроводник), причём микросхемы этого типа имеют очень низкую потребляемую мощность, за счёт особенностей МДП транзисторов оперировать малыми токами и имеющими очень малый ток утечки.

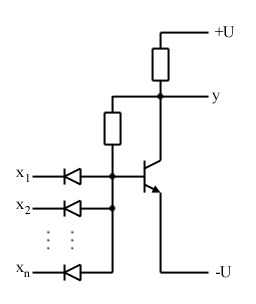

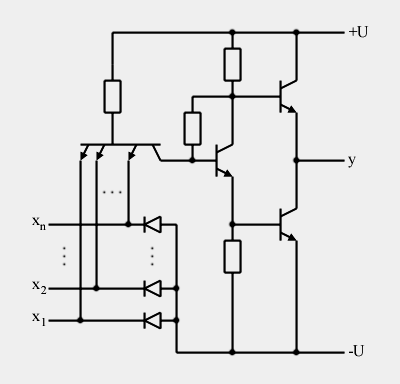

Рассмотрим электрические принципиальные схемы логического элемента И-НЕ с n входами - ДТЛ (рис. 22) и логического элемента И-НЕ с n входами - ТТЛ (рис. 23).

Рис. 22 Рис. 23

На рисунках +U обозначает положительный потенциал источника питания, а -U - отрицательный.

Рассмотрим сначала работу схемы на рис. 22. Если к одному из входных диодов приложено напряжение логического 0, то этот диод открыт и на базу транзистора подаётся напряжение логического 0. Транзистор закрывается и на выходе y устанавливается напряжение логической 1. Только когда ко всем входным диодам будет приложено напряжение логической 1 транзистор откроется и на выходе установится напряжение логического 0. Оставшиеся каскады на транзисторах выполняют функцию усиления сигнала и инвертирования. При подаче на вход второго транзистора напряжения логического 0, он закроется, подключив базы транзисторов оконечного каскада через резисторы к плюсу и к минусу источника питания. Один из транзисторов оконечного каскада откроется, а другой - закроется и на выходе установится напряжение логической 1. При подаче на второй транзистор напряжения логической 1, он откроется. Теперь открытый и закрытый транзисторы оконечного каскада поменяются местами и на выходе установится напряжение логического 0.

Теперь рассмотрим работу схемы на рис. 23. Вызывает некоторый интерес необычный транзистор на входе и схема его включения. Такие многоэмиттерные транзисторы всегда используются на входах логических элементов ТТЛ. Сам транзистор выполняет логическую операцию И. При подаче на один из входов напряжения логического нуля, транзистор открывается и, таким образом, на коллекторе устанавливается напряжение логического 0. Напряжение логической 1 будет на коллекторе только тогда, когда на всех входах будет напряжение логической 1. Подобный транзистор можно рассматривать как много n-p переходов, а соответственно, как много диодов. Таким образом такое включение транзистора в цепь эквивалентно диодной сборке на входе логического элемента И на рис. 9.

Применение логических элементов

Логические элементы могут использоваться как самостоятельные части схемы, так и входить в состав более сложной цифровой комбинационной схемы или схемы с памятью. Как самостоятельные части схемы, логические элементы могут применяться в качестве управляющей логики какого-либо устройства, а также в качестве генератора прямоугольных импульсов с подключённой ёмкостью или кварцевым резонатором. В качестве комбинационных схем логические элементы используются в составе микросхем БИС и СБИС, а также в дешифраторах и шифраторах, выполненных в виде отдельных микросхем. Также, логические элементы могут входить в состав схем с памятью (триггеры, регистры, счётчики и т.д.), выполненных в виде отдельной микросхемы или в составе других микросхем.

Задание для выполнения работы

1. Из каких условных символов состоят обозначения логических элементов?

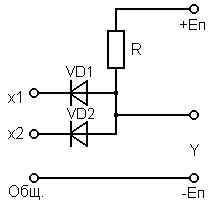

2. Определите напряжение на выходе элемента И (рис. 24) при напряжениях на входах 5 и 7 В и напряжении источника питания 10 В.

Элемент И состоит из диодов и одного резистора, но требует источника питания. Напряжение источника питания должно быть не меньше напряжения уровня логической 1. Заметьте, что диоды к входам подключаются катодами. В первой строчке таблицы истинности элемента И на входы схемы поданы уровни логического 0, а на аноды через резистор R напряжение источника питания Eп. Оба диода открыты. Согласно второму закону Кирхгофа для цепи – (UВХ – UVD – UВЫХ):

UВХ = - UVD + UВЫХ ,

UВЫХ = UВХ + UVD .

Рис. 24. Схема логического элемента И

3. Определите напряжение на выходе элемента И (рис. 24) при напряжениях на входах 5 и 7 В и напряжении источника питания 4 В.

4. На схему рис. 24 подали сначала синусоидальный сигнал, а затем прямоугольные импульсы. Начертите выходной сигнал.

5.Представить схему равнозначности (эквивалентности) в базисе 4И-НЕ.

6. Транзистор логического элемента НЕ (рис. 24) находится в режиме насыщения. Определите ток коллектора при Еп = 5 В и Rк = 1 кОм.

7. Начертите схему ТТЛ логического элемента ИЛИ-НЕ на дискретных элементах.

8. Начертите схему ТТЛ логического элемента И-НЕ на дискретных элементах.

9. Начертите схему логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ на дискретных элементах.

10. Как видоизменить схему, начерченную в пункте 8, чтобы получить логический элемент, выполняющий функцию равнозначности?