- •Features

- •Pin Configuration

- •Overview

- •ATtiny11 Block Diagram

- •ATtiny12 Block Diagram

- •Pin Descriptions

- •Port B (PB5..PB0)

- •XTAL1

- •XTAL2

- •RESET

- •Status Register

- •Internal RC Oscillator

- •Crystal Oscillator

- •External Clock

- •External RC Oscillator

- •Register Description

- •Memories

- •I/O Memory

- •Register Indirect

- •I/O Direct

- •Flash Program Memory

- •EEPROM Data Memory

- •Register Description

- •Sleep Modes

- •Sleep Modes for the ATtiny11

- •Idle Mode

- •Power-down Mode

- •Sleep Modes for the ATtiny12

- •Idle Mode

- •Power-down Mode

- •Reset Sources

- •External Reset

- •Watchdog Reset

- •Register Description

- •Interrupts

- •Reset and Interrupt

- •Interrupt Handling

- •Interrupt Response Time

- •External Interrupt

- •Pin Change Interrupt

- •Register Description

- •I/O Port B

- •Register Description

- •Port B as General Digital I/O

- •Alternate Functions of Port B

- •Timer/Counter0

- •Timer/Counter Prescaler

- •Register Description

- •Watchdog Timer

- •Register Description

- •Analog Comparator

- •Register Description

- •Fuse Bits in ATtiny11

- •Fuse Bits in ATtiny12

- •Signature Bytes

- •ATtiny11

- •ATtiny12

- •ATtiny11/12

- •High-voltage Serial Programming

- •Low-voltage Serial Downloading (ATtiny12 only)

- •Data Polling

- •Electrical Characteristics

- •Absolute Maximum Ratings

- •External Clock Drive ATtiny11

- •External Clock Drive ATtiny12

- •Register Summary ATtiny11

- •Register Summary ATtiny12

- •Instruction Set Summary

- •Ordering Information

- •ATtiny11

- •ATtiny12

- •Packaging Information

- •Table of Contents

|

|

|

|

|

|

|

|

|

|

|

|

|

ATtiny11/12 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

Timer/Counter0 |

|

|

|

|

|

|

|

|

|

|

|

|||

|

The ATtiny11/12 provides one general-purpose 8-bit Timer/Counter – Timer/Counter0. |

||||||||||||||

|

|||||||||||||||

|

|

The Timer/Counter0 has prescaling selection from the 10-bit prescaling timer. The |

|||||||||||||

|

|

Timer/Counter0 can either be used as a timer with an internal clock timebase or as a |

|||||||||||||

|

|

counter with an external pin connection that triggers the counting. |

|||||||||||||

|

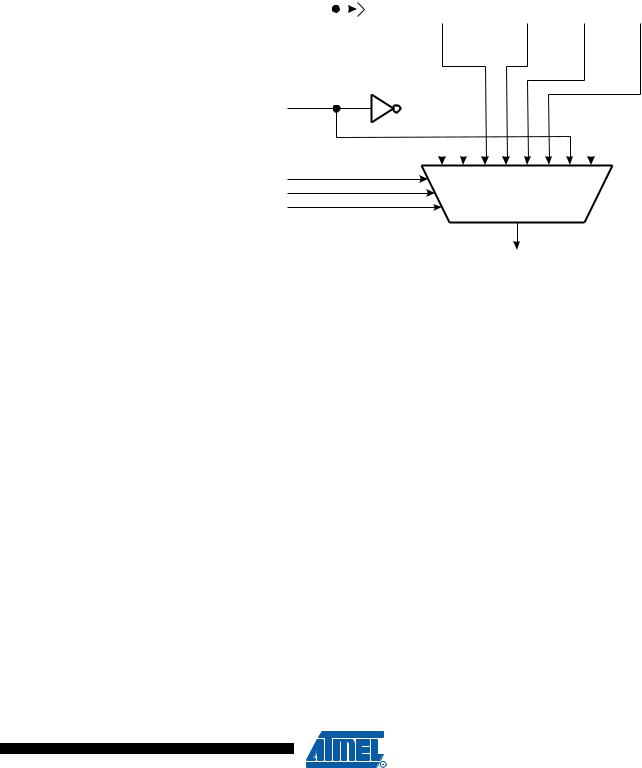

Timer/Counter Prescaler |

Figure 22 shows the Timer/Counter prescaler. |

|

|

|

|

|

||||||||

|

|

Figure 22. Timer/Counter0 Prescaler |

|

|

|

|

|

|

|

|

|||||

|

|

CK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10-BIT T/C PRESCALER |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CK/8 |

|

|

CK/64 |

CK/256 |

|

CK/1024 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

T0 |

|

|

|

|

|

|

|

|

|

||||

|

|

|

0 |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

CS00 |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

||||||

|

|

CS01 |

|

|

|

|

|

|

|

|

|||||

|

|

CS02 |

|

|

|

|

|

|

|

|

|||||

TIMER/COUNTER0 CLOCK SOURCE

TCK0

The four different prescaled selections are: CK/8, CK/64, CK/256 and CK/1024 where CK is the oscillator clock. CK, external source and stop, can also be selected as clock sources.

Figure 23 shows the block diagram for Timer/Counter0.

The 8-bit Timer/Counter0 can select clock source from CK, prescaled CK, or an external pin. In addition, it can be stopped as described in the specification for the Timer/Counter0 Control Register – TCCR0. The overflow status flag is found in the Timer/Counter Interrupt Flag Register – TIFR. Control signals are found in the Timer/Counter0 Control Register – TCCR0. The interrupt enable/disable settings for Timer/Counter0 are found in the Timer/Counter Interrupt Mask Register – TIMSK.

When Timer/Counter0 is externally clocked, the external signal is synchronized with the oscillator frequency of the CPU. To ensure proper sampling of the external clock, the minimum time between two external clock transitions must be at least one internal CPU clock period. The external clock signal is sampled on the rising edge of the internal CPU clock.

The 8-bit Timer/Counter0 features both a high-resolution and a high-accuracy usage with the lower prescaling opportunities. Similarly, the high-prescaling opportunities make the Timer/Counter0 useful for lower-speed functions or exact-timing functions with infrequent actions.

39

1006F–AVR–06/07

Figure 23. Timer/Counter0 Block Diagram

T0 |

40 ATtiny11/12

1006F–AVR–06/07