- •1.2 Функциональная структура процессора с одним трактом обмена данными между регистрами.

- •2.Пересылка слова данных из одного регистра в другой.

- •3.Выполнение арифметической или логической операции.

- •1.5 Реализация безусловного и условного переходов.

- •1.6 Структура процессора с тремя тактами передачи.

- •2. Вертикальная организация микрокоманд

- •3. Смешанная организация микрокоманд

- •2.6 Системы ввода/вывода эвм

- •Глава 3. 3.1 Система прерываний эвм

- •Внешние прерывания (их еще называют аппаратными). Могут быть разделены на 3 типа:

- •3.5. Механизм прерываний на примере процессора Pentium

- •3.8. Механизм вызова программ обработки прерываний в эвм

- •Глава 4 Видеосистема эвм

- •Видеоадаптер (видеокарта)

- •4.6. Восприятие человеком 3-х мерных изображений

- •Глава 5. Периферийные устройства эвм

- •5.4. Графопостроители (плоттеры)

- •Фотоэлектронный умножитель (фэу)

- •6.5. Структурная схема эвм и иерархия средств подключения к ней периферийных устройств (м. Гук Шины usb, pci и FireWire 2005 г. Стр. 203-332)

- •6.8. Протокол шины usb

Внешние прерывания (их еще называют аппаратными). Могут быть разделены на 3 типа:

а) программно-вызываемые

б) немаскируемые

в) маскируемые

а) Программно-вызываемые в прямом смысле не являются прерываниями, а представляют собой специфический способ вызова процедур не по адресу, а по номеру в таблице прерываний.

б) К немаскируемым прерывания относят: запросы от схем контроля памяти, например, возникновение ошибки четности, запросы при ошибках с шин расширения, с клавиатуры, таймера и т.д. Их линия проходит в процессор через порт с адресами 061h или 070h.

в) К маскируемым прерываниям относятся все прерывания от внешних устройств. Их еще называют пользовательскими. Их обработка разрешается командой EI а запрещается командой FI, которые устанавливают или убирают флаг IF в RG FLAGS, причем команда EI может разрешать и вложенные прерывания.

3.5. Механизм прерываний на примере процессора Pentium

Системы прерываний у разных архитектур процессоров могут иметь разное число линий для запросов прерываний. Процессоры архитектуры IA-32, например, типа Pentium используют две входных линии прерываний:

- линия NMI (Non-Maskable Interrupt) – для немаскируемых прерываний, которые имеют наивысший приоритет и принимаются процессором в любой момент времени, независимо от приоритета текущей программы.

- Линия INTR – для маскируемых прерываний которые принимаются процессором, когда они имеют более высокий приоритет, чем выполняемая в это время программа. Прерывания по линии INTR разрешаются или запрещаются флагом разрешения IF в регистре состояния RG FLAGS/

Каждому прерыванию (исключениям и внешнему) назначается вектор, который определяет начальный адрес программы обработки прерывания, хранящийся в таблице дескрипторов прерываний (Interrupt Descriptor Table).

Для прерываний/исключений векторы задаются заранее и являются постоянными. Обрабатываются такие прерывания независимо от значения флага IF, вложенные прерывания не допускаются, их обработка возможно после обработки предыдущего исключения по команде возврата IRET программы обработки.

Особое значение имеет немаскируемое прерывание по сигналу от схе управления энергопотребления. Обладает наивысшим приоритетом. В этом случае процессор не производит вызов процедуры из таблицы прерываний, а переходит в режим NMI#. При этом в памяти SM RAM автоматически сохраняется слово состояния процессора, после чего начинается выполнение программы обработки, находящейся также в SM RAM. Все другие прерывания в это время не воспринимаются.

Примечание. Память SM RAM – это адресное пространство, параллельное пространству основной памяти и доступное процессору только в режиме MI#. SM RAM может быть отдельной микросхемой с энергонезависимой памятью емкостью от 32 кбайт до 4 Г байт.

Процедура перехода к прерывающей программе:

По сигналу запроса ЗПх, после завершения выполнения команды А основной программы, происходит запись адреса следующей команды А+1 в RG AB и слова состояния в стек. Далее в СТ – команд записывается адрес первой команды программы обработки запроса и начинается ее выполнение.

По завершению обработки по команде IRET - возврат прерывающей программы, адрес А+1 основной программы заносится в счетчик СТ, восстановленный в соответствии со словом состояния изъятого из стека и продолжается выполнение основной программы.

Структура прерывающей программы:

Аппаратное обеспечение прерываний ЭВМ

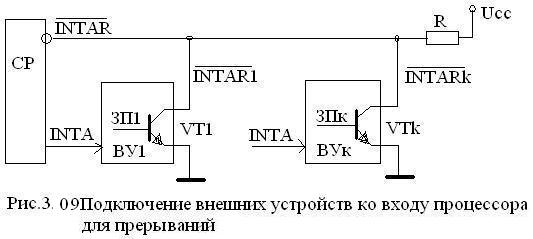

Как уже было сказано, в разных архитектурах процессоров имеется разное число входов (линий) для запросов прерываний, поэтому существуют разные способы подключения внешних устройств (ВУ) для направления запросов в процессор.

Допустим в процессоре имеется одна линия прерывания. Тогда внешние устройства (ВУ) можно подсоединить к этой линии через ключ (VT с открытым коллектором) соединенный с землей.

Когда сигнал запроса ЗП: отсутствует, VT;

Закрыт сигнал на выходе INTRi = 1.

При возникновении запроса ЗП: в одном или нескольких ВУ сигнал INTR = 0, который является активным, т.е. значение INTR является логической суммой (ИЛИ) отдельных ВУ:

INTR = INTR1 + … + INTR к

Однако, может случиться, что запросы возникли одновременно у нескольких ВУ, поэтому потребуется выбор.

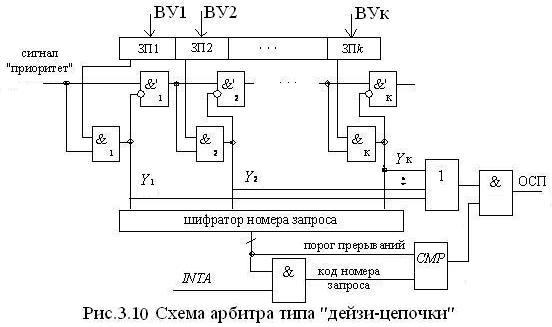

Эта задача может быть решена в этом случае с помощью например «Дейзи-цепочки»: (арбитра приоритетов)

Глее код номера запроса – это номер ВУ, которому разрешается выставить вектор прерывания на шину данных процессора.

При возникновении запроса от ВУ: сигнал INTA проходит через &1, &2 и т.д. до &i и далее не проходит. На выходе элемента &i сформируется сигнал Уi, который в шифраторе CD образует № ВУ: от которого поступил запрос.

После выработки общего сигнала прерывания (ОСП) ВУi по этому номеру передает на ШD процессора свой вектор прерывания и начнется его обработка.

Здесь приоритет более высокий у того ВУ, которое стоит в дейзи-цепочке первым.

Организация приоритетов в подобном подсоединении ВУ к процессору может быть разной.

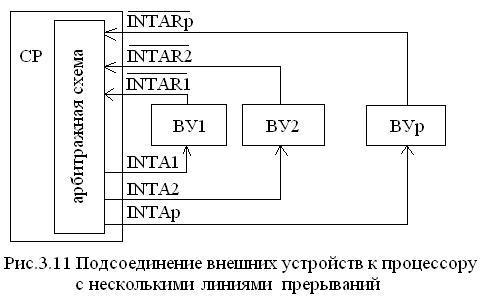

У процессора есть несколько линий прерываний, тогда ВУ можно подсоединять следующим образом.

Процессор принимает запросы в соответствии с приоритетом.

Приоритет может быть установлен в соответствии с номером линии или через арбитражную схему.

Иногда применяется смешанное подсоединение: применяется гирляндная цепь для каждой линии.

Арбитражная схема может быть построена разными способами.

1. С использование RG запросов и RG маски:

2. Схема циклического опроса

Каждому ВУ соответствует разряд (флаг) в RG ЗП. Счетчик СТ циклически через DC опрашивает разряды RG зп. Опрос начинается со сброса триггера Т и СТ в «0», при этом тактовые импульсы с G т.и. поступают в ст. В каждом такте проверяется наличие «1» (флага) в RGзп. Первое совпадение в & вызывает опрокидывание триггера Т и дается разрешение ВУ на посылку вектора прерывания в процессор.

Прерывания с круговым (циклическим) приоритетом

В этом случае установленные приоритеты после обслуживания изменяются в круговом порядке так, что обслуженный запрос переходит в наименьший приоритет.

5. Случайные приоритеты. В этом случае с помощью генератора псевдослучайных числе, приоритеты устанавливаются для каждого ВУ.

Реализация входов прерываний через контроллеры прерываний

Маскируемые прерывания могут обслуживаться и программируемыми контроллерами типа 8259А, имеющими 8 входов запросов IRx и допускающих их каскадное соединение до 8 шт, обеспечивается до 56 прерываний.

Получив запрос ЗП: от ВУ на своем входе IR контроллер вырабатывает сигнал прерывания INTR.

Получив запрос ЗП от ВУ на своем входе IRi контроллер вырабатывает сигнал прерывания INTR и посылает его в процессов по одноименной линии. Процессор получив этот сигнал прерывания вырабатывает сигнал подтверждения и формирует шинный цикл INTA, в течение которого контроллер через свой буфер данных BD передает на шину данных ШД 8мм-битный вектор данного запроса. Этот вектор есть номер, по которому процессор извлекает из таблицы прерываний начальный адрес программы обработки запроса.

Примечание. Контроллер 8259А был разработан для использования в процессорах 8080, имеет 2 шинных цикла INTA:

- в первом цикле передавалась команда вызова программы обработки прерывания

- CALL

- во втором цикле передавались младший и старший байты адреса начала программы обработки (в те времена еще не было таблицы прерываний).

С появлением архитектуры IA-32 контроллер использует только второй цикл для передачи вектора прерываний, тем самым сохранена программная совместимость.

В случае каскадного соединения контроллеров, один из них выполняет роль ведущего, для чего на его вход SP подается +SB, остальные – роль ведомых при подаче на их входы EN= 0.

Ведущий принимает запросы от ведомых (тем самым от ВУ) в виде сигнала INT. Получив этот сигнал ведущий вырабатывает сигнал INTR и посылает его по одноименной линии в процессор и отправляет код CAS 2-0 запросившему прерывание контроллеру, разрешая ему по сигналу INTA из процессора выставить на шину данных ШД 8-ми-битный вектор данного запроса. Далее все происходит аналогично описанному ранее.

В заключение следует отметить, что на входы контроллеров могут поступать запросы от системных устройств как например, от клавиатуры, таймера, сопроцессора, от плат расширения.

На смену контроллера 8259A приходит усовершенствованный, совместимы с 8259А, контроллер APIC – Advanced Periferal Interruption Controller.

Такие внутренние контроллеры связаны между собой одноименной шиной APIC, к которой для связи с процессором подсоединен чиспет (chipset), преобразующий сигналы прерываний в сигналы протокола обмена. (Чипсет – это набор микросхем образующий сложный функциональный узел)

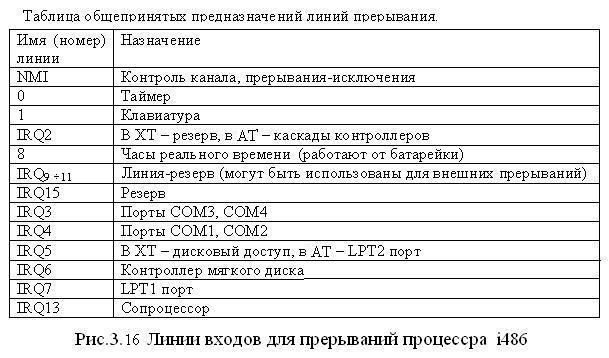

Примечание. Можно привести таблицу общепринятых предназначений линий прерывания для процессора i486 (Рис. 3.16)

В современных ЭВМ число линий сокращено, поскольку появились USB – универсальная шина.

Об этом в курсе «Интерфейсы периферийных устройств».