- •1.2 Функциональная структура процессора с одним трактом обмена данными между регистрами.

- •2.Пересылка слова данных из одного регистра в другой.

- •3.Выполнение арифметической или логической операции.

- •1.5 Реализация безусловного и условного переходов.

- •1.6 Структура процессора с тремя тактами передачи.

- •2. Вертикальная организация микрокоманд

- •3. Смешанная организация микрокоманд

- •2.6 Системы ввода/вывода эвм

- •Глава 3. 3.1 Система прерываний эвм

- •Внешние прерывания (их еще называют аппаратными). Могут быть разделены на 3 типа:

- •3.5. Механизм прерываний на примере процессора Pentium

- •3.8. Механизм вызова программ обработки прерываний в эвм

- •Глава 4 Видеосистема эвм

- •Видеоадаптер (видеокарта)

- •4.6. Восприятие человеком 3-х мерных изображений

- •Глава 5. Периферийные устройства эвм

- •5.4. Графопостроители (плоттеры)

- •Фотоэлектронный умножитель (фэу)

- •6.5. Структурная схема эвм и иерархия средств подключения к ней периферийных устройств (м. Гук Шины usb, pci и FireWire 2005 г. Стр. 203-332)

- •6.8. Протокол шины usb

1. Структурная организация ЭВМ.

1.1Функциональная структура ЭВМ.

В ЭВМ можно выделить 5 основных функционально независимых частей: устройства ввода и вывода, основная память, ALU, устройства управления и система шин. Связь между этими частями может быть организована по-разному, на рисунке приведен один из возможных вариантов.

Устройство ввода принимает через цифровые линии связи закодированную информацию от оператора, различных устройств или от других ЭВМ, которая либо сохраняется в памяти ЭВМ для последующего применяется, либо немедленно используется ALU или логическими схемами для выполнения необходимых операций.

Последовательность шагов обработки определяется соответствующей программой, хранящейся в памяти. Результаты обработки отправляются во внешнюю среду через устройства вывода.

Все эти действия ЭВМ координируются (инициируются) устройствами управления.

Кэш-память служит для увеличения скорости обмена между основной памятью и ALU. ALU и различные логические схемы в комплексе с устройствами управления принято называть процессором.

Шины предназначены для связи между перечисленными частями ЭВМ.

Обрабатываемую ЭВМ информацию удобно разделять на 2 основные категории:

Команды и данные

1)Команды (или машинные команды) – это инструкции, которые управляют пересылкой информации внутри ЭВМ и между ЭВМ и устройствами вв/в, а также определяют подлежащие выполнению арифметические и логические операции.

Список команд, выполняющих определенную задачу, будем называть программой, хранящейся в памяти.

Процессор по очереди извлекает из памяти команды и реализует определенные операции. В этот процесс возможно вмешательство оператора или устройств вв/в через так называемые прерывания.

2)Данные – это числа или закодированные символы, используемые как операнды. (В принципе команды тоже можно считать данными).

Обработку одной программой другой программы называют компиляцией. Выполняет ее компилятор, который транслирует (преобразует) исходную программу в программу на машинном языке.

Информация для обработки в ЭВМ должна быть закодирована в определенном формате (строка двоичных цифр).

3)Устройство ввода читает данные и передает их и в ЭВМ. Наиболее распространенными являются: клавиатура, мышь, которые при нажатии на клавишу преобразую сигнал в двоичный код определенного формата и пересылают в память или процессор. Устройств ввода существует большое количество.

4)Устройство вывода решает противоположную задачу: результаты обработки преобразуют в форму, приемлемую оператором или другим устройством и передают во внешнюю среду.

Некоторые устройства вывода могут выполнять и функцию ввода.

5)Память (отдельный курс ЗУ) предназначена для хранения программ и данных. Представляет собой иерархическую структуру из трех или четырех уровней с различным быстродействием и емкостью. Наиболее быстрая это регистровая и кэш-память.

6)ALU – уже изучено.

7)Устройства управления – это устройства, взаимодействующие с другими частями ЭВМ. На практике большая часть управляющих схем физически распределена в разных частях ЭВМ с целью упрощения с управляемыми объектами.

Основное назначение устройства управления – генерация сигналов управления (синхронизирующих сигналов) пересылкой данных, выполнением операций над ними. Эти сигналы передаются по множеству управляющих линий (проводников).

Структура процессора постоянно совершенствуется с использованием достижений технологии с целью увеличения его производительности.

Основная стратегия создания высокопроизводительных процессоров направлена на обеспечение параллельной работы как можно большего числа функциональных узлов ЭВМ, например, применением конвейерной организации, при которой выполнение очередной команды начинается до завершения предыдущей, или применением суперскалярного функционирования, когда из памяти одновременно выбирается и выполняется несколько команд.

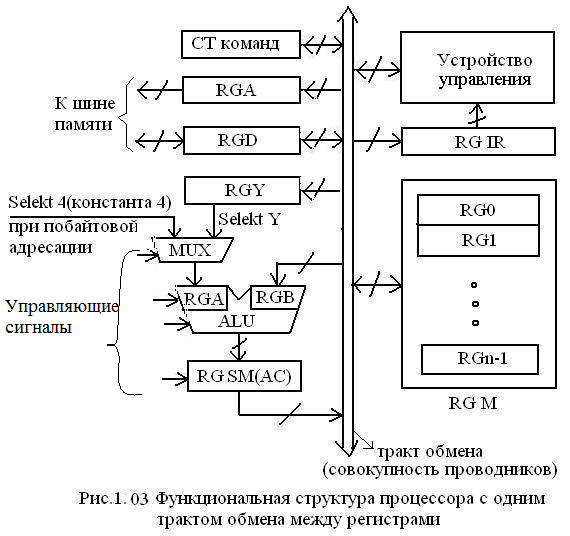

1.2 Функциональная структура процессора с одним трактом обмена данными между регистрами.

Где: CT – счетчик команд (RG – Instruction Register);

RGA – регистр адреса;

RGD – регистр данных;

RGY, RGA, RGB – буферные регистры ALU;

RG IR – регистр команд;

RG M – регистровая память (RG0, RG1,…, RGn-1);

RGD имеет 2 входа и 2 выхода. Данные могут загружаться либо с внутреннего тракта обмена, либо с шины памяти. Аналогично и считывание.

RGM – это набор регистров RG0, RG1,…, RGn-1, который часто называют РОНами (регистры общего назначения) или просто внутренней памятью.

Устройство управления вырабатывает необходимую последовательность управляющих сигналов для управления устройствами внутри процессора и взаимодействия с шиной памяти (системной шиной).

Регистры, ALU и внутренняя шина образуют тракт данных (data path).

Для выполнения программы процессор последовательно выбирает команды из памяти и выполняет определяемые ими действия. Команды выбираются по последовательным адресам, пока не встретится команда перехода (к другой программе или к другой области адресов) или команда ветвления.

Для этого в CT-команд формируется адрес очередной команды путем инкрементирования. Команда перехода или ветвления может загрузить в СТ-команд другой адрес.

Важным регистром, связанным с выполнением команды, является RG IR.

Пусть команда имеет длину 4 байта и содержится в одном слове, хранимом в памяти. Тогда для ее выполнения процессор осуществляет следующие шаги (такты):

Выбирает из памяти слово (4 байта) на которое указывает адрес, содержащийся в CT-команд и загружает его в RG IR.

Если память адресуется побайтно, то содержимое CT увеличивается на 4.

Выполняет действия, определяемые командой, теперь находящейся в RG IR.

Если команда длиной более одного слова, то пункты 1 и 2 повторяются столько раз, сколько надо для выборки всей команды.

Шаги 1 и 2 называют фазой выборки команды, а шаг 3 – фазой выполнения команды.

1.3 Выполнение команд процессором.

Процесс выполнения команды в большинстве случаев это реализация в определенной последовательности одной или нескольких

следующих операций:

Чтение (запись) по заданному адресу содержимого памяти, его загрузки в соответствующие регистры и наоборот.

Пересылка слова на данных из одного регистра в другой.

Выполнение арифметических и логических операций и запись их результата в регистры процессора.

Запись слова данных (результата операций) из регистра процессора по заданному адресу в память.

Рассмотрим эти операции:

4 и 1 – операции записи в память и чтения из памяти.

Суть процесса выборки (чтения) или записи.

Выборка: В RGA по сигналу из устройства управления помещается адрес и по управляющей линии указывается вид операции (Read).

Считанные данные по сигналу YDin из УУ записываются в RG D, откуда используются другими регистрами.

Запись: По сигналу из УУ данные из одного из регистров процессора записываются в RG D и далее по системной шине передаются в память, где и записываются.

Очевидно, что RGD процессора должен иметь 2 входа и 2 выхода (мультиплексированные вход и выход):

Замечание. В ходе считывания (записи) данных из памяти очевидно, что процесс тактирования процессора должен быть скоординирован с сигналами устройств, с которыми он связывается через системную шину.