- •Базовые функции компьютера общего назначения. Взаимодействие компьютера с информационной средой.

- •«Узость» понятия «Архитектура компьютера». Структурная организация компьютера.

- •Уровни организации компьютера.

- •Концепция фон Неймана.

- •Машина фон Неймана: принцип разработки, базовые компоненты.

- •Цикл выполнения команды: состояния; детализированный граф переходов.

- •Архитектура системы команд: основные понятия, свойства, общая характеристика.

- •Команды компьютера общего назначения: основные группы.

- •Команды компьютера общего назначения: компоненты, формат, операционная часть.

- •Символическое представление команды. Критерии выбора формата команд.

- •Адресная часть команды компьютера общего назначения. Варианты реализации.

- •Режимы адресации: непосредственный, прямой, регистровый.

- •Адресация со смещением: общие принципы, относительная адресация, адресация через регистр базы.

- •Стековая адресация: принципы реализации, виды стека, управление стеком, стек-ориентированные операции.

- •Выполнение арифметических операций в компьютере со стековой архитектурой. Полиз.

- •Адресация с индексированием: общие принципы, разновидности.

- •Базовые типы операндов: данные логического типа, строки, адреса.

- •Базовые типы операндов: числа, разрядность основных форматов, размещение в памяти.

- •Данные символьного типа: юникод.

- •Данные символьного типа: общие сведения, принципы кодирования, стандарты ascii и iso 8859, кодовые страницы.

- •Архитектура на основе общей магистрали. Характеристики системной магистрали.

- •Алгоритм функционирования системной магистрали. Взаимодействие устройств.

- •Иерархия магистралей: двух- и трехшинная архитектура.

- •Шинный арбитраж: предпосылки введения, схемы приоритетов.

- •Шинный арбитраж: алгоритмы динамического изменения приоритетов.

- •Централизованный параллельный и многоуровневый арбитраж шины.

- •Централизованный последовательный арбитраж.

- •Децентрализованный арбитраж шин.

- •Опросные схемы арбитража шин.

- •Протокол шины: понятие, виды протоколов. Транзакции синхронной шины.

- •Асинхронные протоколы шины: транзакции, тайм-ауты.

- •Пакетный режим пересылки информации. Конвейеризация транзакций.

- •Расщепление транзакций. Увеличение полосы пропускания шины.

- •Система ввода-вывода: назначение элементов, организация адресного пространства.

- •Детализированные функции модуля ввода-вывода.

- •Структурная организация модуля ввода-вывода.

- •Алгоритм обмена информацией между центральным процессором и внешним устройством.

- •Способы организации ввода-вывода. Программно управляемый ввод-вывод.

- •Команды, используемые при программно управляемом вводе-выводе.

- •Ввод-вывод по прерываниям: принципы, механизм.

- •Методы идентификации устройств, запрашивающих прерывание.

- •Векторные прерывания: принципы реализации, виды.

- •Приоритеты прерываний. Отличие последовательной обработки прерываний от обработки вложенных прерываний.

- •Контроллер прямого доступа к памяти (кпдп): состав и назначение компонентов, инициализация.

- •Алгоритм обмена на основе пдп. Буферизация данных.

- •Варианты реализации механизма пдп. Достоинства и недостатки.

- •Понятия канала ввода-вывода и процессора ввода-вывода.

- •Канальная программа. Управляющее слово канала.

- •Алгоритм функционирования канала ввода-вывода. Способы организации взаимодействия ву с каналом.

- •Режимы канала ввода-вывода.

- •Методы доступа к данным в памяти компьютера.

- •Параметры оценки быстродействия памяти.

- •Иерархическая архитектура памяти компьютера: предпосылки внедрения, принципы реализации и функционирования.

- •Локальность по обращению: виды, использование в архитектурных решениях.

- •Иерархия памяти компьютера: характеристики, описание уровней.

- •Основная память компьютера: назначение, типы запоминающих устройств, способы организации

- •Адресная организация памяти компьютера.

- •Блочная организация памяти: назначение, виды, факторы эффективности применения.

- •Расслоение памяти и чередование адресов: назначение, принцип реализации.

- •Ассоциативная память: логическая организация, функционирование.

- •Логическая и функциональная организация кэш-памяти прямого отображения.

- •Логическая и функциональная организация полностью ассоциативной кэш-памяти.

- •Логическая и функциональная организация множественно-ассоциативной кэш-памяти.

- •Алгоритмы замещения информационных блоков в кэш-памяти: назначение, виды, реализация.

- •Согласование содержимого кэш-памяти и оп. Стратегии записи в кэш-памяти.

- •Многоуровневая кэш-память. Принстонская и гарвардская архитектуры кэш-памяти.

- •Виртуализация памяти компьютеров: предпосылки внедрения, принцип реализации, виды виртуальной памяти.

- •Концепция страничной организации памяти. Взаимодействие виртуальной памяти с кэш-памятью.

- •Ограничения страничной организации памяти. Сегментация памяти.

- •Проблемы динамического распределения памяти при сегментации. Сегментно-страничная организация памяти.

- •Метод колец защиты памяти.

- •Метод граничных регистров памяти.

- •Защита памяти по ключам.

- •Концепция raid: принципы построения массивов дисковой памяти, назначение, способы реализации.

- •Дисковые массивы raid уровней 0, 1, 10: назначение, принципы реализации, свойства.

- •Дисковые массивы raid уровней 5, 6: назначение, принципы реализации, свойства.

- •Многопортовые озу и озу типа fifo.

- •Прерывания: фаза прерывания, поток данных, классы прерываний.

- •Арифметический конвейер: назначение, принципы реализации. Понятие суперконвейера.

- •Конвейерная обработка данных: предпосылки внедрения, принципы реализации, способы синхронизации ступеней.

- •Синхронный конвейер: реализация 6-ступенчатого конвейера, метрики эффективности, оценка выигрыша от внедрения.

- •Виды рисков синхронного конвейера.

- •Методы снижения приостановок конвейера.

- •Risc-архитектура: предпосылки создания, принципы реализации.

- •Risc-архитектура: средства оптимизации использования регистров.

- •Параллелизм уровня команд. Концепция vliw-архитектуры.

- •Суперскалярные компьютеры: принципы построения, структура процессора.

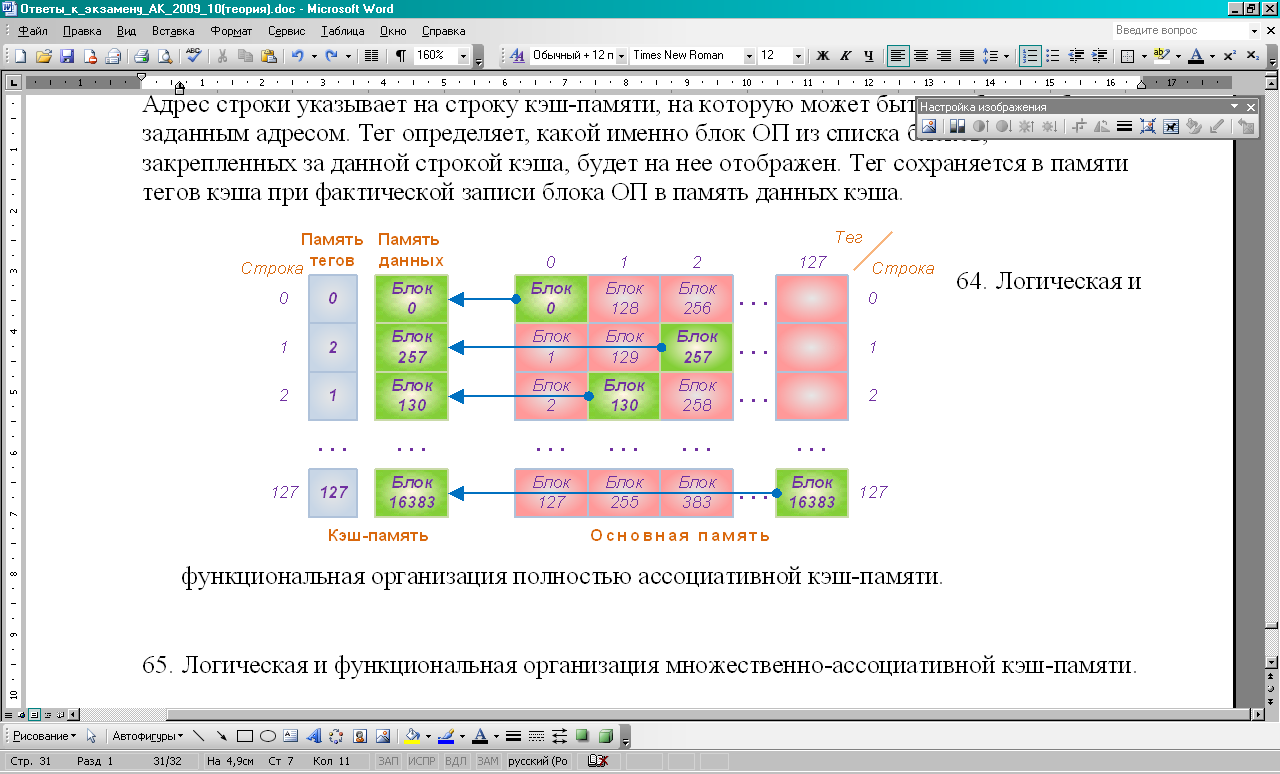

Логическая и функциональная организация кэш-памяти прямого отображения.

При прямом отображении содержимого ОП на кэш-память Адрес строки i кэш-памяти, на которую может быть отображен блок j из ОП, однозначно определяется выражением: i = j mod C (mod - остаток от деления), где С – общее число строк в кэш-памяти.

Таким образом, n-разрядный адрес блока в ОП интерпретируется следующим образом:

- младшие ]log2C[ разрядов адреса – поле адреса строки в кэше;

- остальные (старшие) разряды – поле тега.

Адрес строки указывает на строку кэш-памяти, на которую может быть отображен блок с заданным адресом. Тег определяет, какой именно блок ОП из списка блоков, закрепленных за данной строкой кэша, будет на нее отображен. Тег сохраняется в памяти тегов кэша при фактической записи блока ОП в память данных кэша.

Свойства прямого отображения:

+ простая схемная реализация;

+ невысокая стоимость;

- жесткое закрепление за определенными блоками ОП одной строки в кэше.

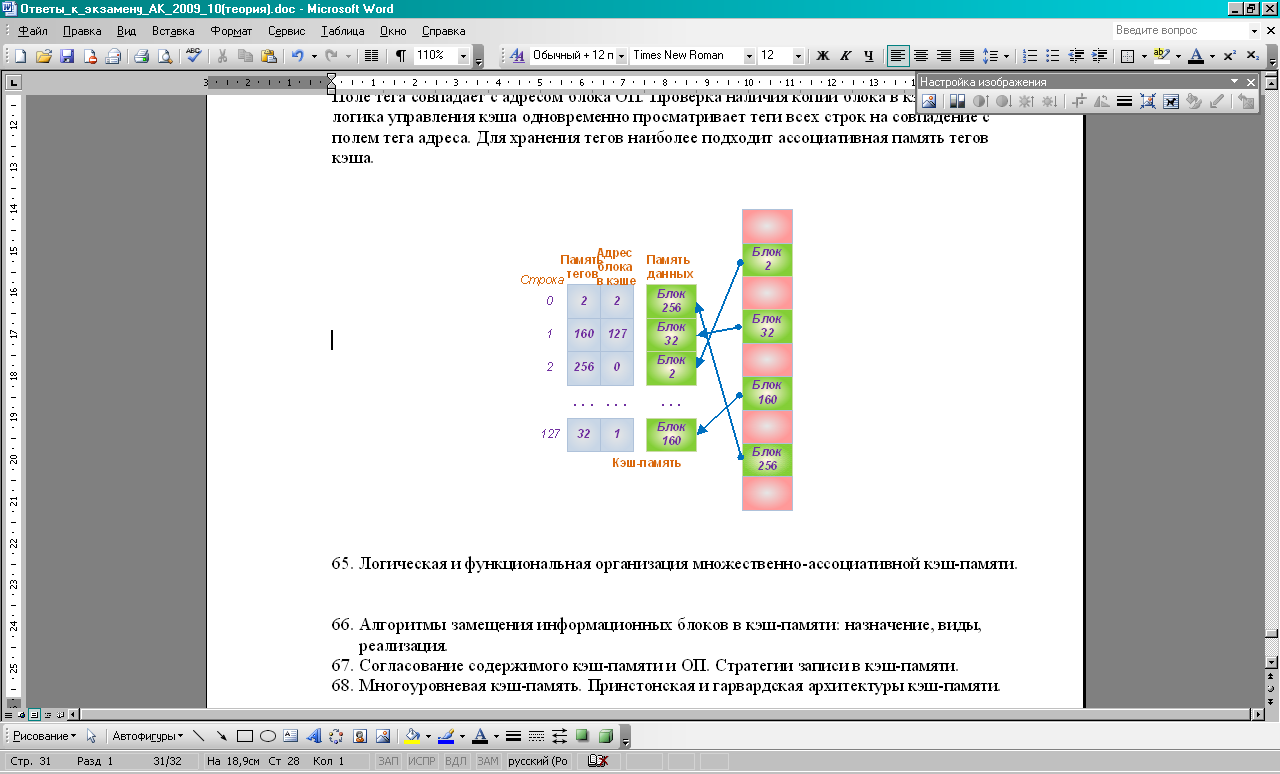

Логическая и функциональная организация полностью ассоциативной кэш-памяти.

Загрузка любого блока ОП в любую строку кэш-памяти.

Логика управления кэш-памяти выделяет в адресе ОП два поля:

- старшие разряды – поле тега;

- младшие разряды – поле слова.

Поле тега совпадает с адресом блока ОП. Проверка наличия копии блока в кэш-памяти: логика управления кэша одновременно просматривает теги всех строк на совпадение с полем тега адреса. Для хранения тегов наиболее подходит ассоциативная память тегов кэша.

Свойства:

+ гибкость при выборе строки для вновь записываемого блока;

+ повышается вероятность кэш-попадания за счет эффективной организации обновления строк;

- сложность схемной реализация (ассоциативный поиск тегов);

- высокая стоимость.

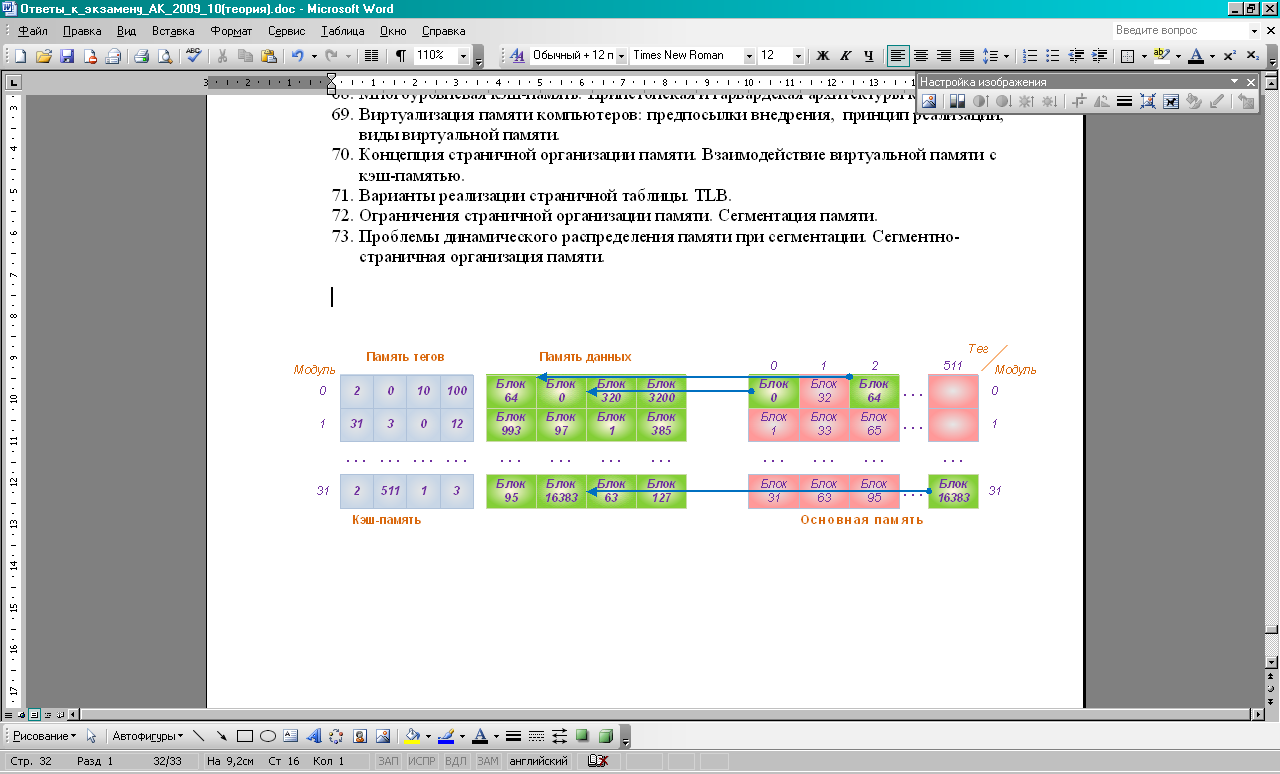

Логическая и функциональная организация множественно-ассоциативной кэш-памяти.

Кэш-память (тегов и данных) разбивается на v подмножеств (модули), каждое из которых содержит k строк («модуль имеет k входов»).

На строки, входящие в модуль i, могут быть отображены только вполне определенные блоки ОП (прямое отображение), в соответствии с соотношением: i = j mod v.

Размещение блоков по строкам модуля – произвольное (ассоциативный способ).

Номер модуля однозначно указывает на один из модулей кэша и позволяет определить номера блока ОП, отображаемых на этот модуль.

Тег – порядковый номер блока из последовательности блоков, отображаемых в кэш.

Чаще всего используют k-входовой модуль.

В предельных случаях множественно-ассоциативное отображение сводится к другим видам отображения:

1) v = C, k = 1 – прямое;

2) v = 1, k = C – полностью ассоциативное.

Алгоритмы замещения информационных блоков в кэш-памяти: назначение, виды, реализация.

При загрузке в заполненную кэш-память нового блока замещается содержимое одной из строк. Алгоритм замещения – правило выбора удаляемой из кэша строки. Цели: удержание строк с актуальной информацией, замена строк, доступ к которым будет в более отдаленном будущем.

Алгоритмы замещения нужно только при полностью или частично-ассоциативном отображении. Виды алгоритмов замещения:

- LRU – least recently used – замещается строк, к которой дольше всего не было обращения.

Способ 1 (гангстерский): С каждой строкой ассоциируется счетчик, который инкрементируется через определенные интервалы времени. При обращении к любой строке счетчик обнуляется. Замещается строк с наибольшим значением на счетчике.

Способ 2 (честный): Используется очередь, куда в порядке заполнения строк заносятся ссылки на них. При каждом обращении к строке ссылка на нее перемещается в конец очереди. Замещается строка, ссылка на которую находится в конце очереди.

Способ 3 (обман трудящихся) - Pseudo-LRU: Используются индикаторы обращения к строке B2B1B0: B2 – указывает, к какой из двух пар строк обращались в последний раз. Анализируя этот индикатор, мы выбираем ту пару, к которой не обращались. За нее отвечает один из индикаторов B1 или B0. По состоянию индикатора можно определить, к какой строке долго не обращались.

- FIFO – first input first output – замещается строка, дольше всего находившаяся в кэше. Используется очередь, в которой положение ссылок после обращения к строке не меняется.

- LFU – least frequently used – замещается строка с наименьшим числом обращения (наименьшее число на счетчика). У каждой строки – свой счетчик, который инкрементируется после обращения к строке. Недостатки: блок, загруженный послденим, будет выгружен первым; сложность аппаратной реализации.

- Random – замещается произвольная строка. Простейший алгоритм, используется редко. Легко реализуется, имеет высокую скорость.