- •Базовые функции компьютера общего назначения. Взаимодействие компьютера с информационной средой.

- •«Узость» понятия «Архитектура компьютера». Структурная организация компьютера.

- •Уровни организации компьютера.

- •Концепция фон Неймана.

- •Машина фон Неймана: принцип разработки, базовые компоненты.

- •Цикл выполнения команды: состояния; детализированный граф переходов.

- •Архитектура системы команд: основные понятия, свойства, общая характеристика.

- •Команды компьютера общего назначения: основные группы.

- •Команды компьютера общего назначения: компоненты, формат, операционная часть.

- •Символическое представление команды. Критерии выбора формата команд.

- •Адресная часть команды компьютера общего назначения. Варианты реализации.

- •Режимы адресации: непосредственный, прямой, регистровый.

- •Адресация со смещением: общие принципы, относительная адресация, адресация через регистр базы.

- •Стековая адресация: принципы реализации, виды стека, управление стеком, стек-ориентированные операции.

- •Выполнение арифметических операций в компьютере со стековой архитектурой. Полиз.

- •Адресация с индексированием: общие принципы, разновидности.

- •Базовые типы операндов: данные логического типа, строки, адреса.

- •Базовые типы операндов: числа, разрядность основных форматов, размещение в памяти.

- •Данные символьного типа: юникод.

- •Данные символьного типа: общие сведения, принципы кодирования, стандарты ascii и iso 8859, кодовые страницы.

- •Архитектура на основе общей магистрали. Характеристики системной магистрали.

- •Алгоритм функционирования системной магистрали. Взаимодействие устройств.

- •Иерархия магистралей: двух- и трехшинная архитектура.

- •Шинный арбитраж: предпосылки введения, схемы приоритетов.

- •Шинный арбитраж: алгоритмы динамического изменения приоритетов.

- •Централизованный параллельный и многоуровневый арбитраж шины.

- •Централизованный последовательный арбитраж.

- •Децентрализованный арбитраж шин.

- •Опросные схемы арбитража шин.

- •Протокол шины: понятие, виды протоколов. Транзакции синхронной шины.

- •Асинхронные протоколы шины: транзакции, тайм-ауты.

- •Пакетный режим пересылки информации. Конвейеризация транзакций.

- •Расщепление транзакций. Увеличение полосы пропускания шины.

- •Система ввода-вывода: назначение элементов, организация адресного пространства.

- •Детализированные функции модуля ввода-вывода.

- •Структурная организация модуля ввода-вывода.

- •Алгоритм обмена информацией между центральным процессором и внешним устройством.

- •Способы организации ввода-вывода. Программно управляемый ввод-вывод.

- •Команды, используемые при программно управляемом вводе-выводе.

- •Ввод-вывод по прерываниям: принципы, механизм.

- •Методы идентификации устройств, запрашивающих прерывание.

- •Векторные прерывания: принципы реализации, виды.

- •Приоритеты прерываний. Отличие последовательной обработки прерываний от обработки вложенных прерываний.

- •Контроллер прямого доступа к памяти (кпдп): состав и назначение компонентов, инициализация.

- •Алгоритм обмена на основе пдп. Буферизация данных.

- •Варианты реализации механизма пдп. Достоинства и недостатки.

- •Понятия канала ввода-вывода и процессора ввода-вывода.

- •Канальная программа. Управляющее слово канала.

- •Алгоритм функционирования канала ввода-вывода. Способы организации взаимодействия ву с каналом.

- •Режимы канала ввода-вывода.

- •Методы доступа к данным в памяти компьютера.

- •Параметры оценки быстродействия памяти.

- •Иерархическая архитектура памяти компьютера: предпосылки внедрения, принципы реализации и функционирования.

- •Локальность по обращению: виды, использование в архитектурных решениях.

- •Иерархия памяти компьютера: характеристики, описание уровней.

- •Основная память компьютера: назначение, типы запоминающих устройств, способы организации

- •Адресная организация памяти компьютера.

- •Блочная организация памяти: назначение, виды, факторы эффективности применения.

- •Расслоение памяти и чередование адресов: назначение, принцип реализации.

- •Ассоциативная память: логическая организация, функционирование.

- •Логическая и функциональная организация кэш-памяти прямого отображения.

- •Логическая и функциональная организация полностью ассоциативной кэш-памяти.

- •Логическая и функциональная организация множественно-ассоциативной кэш-памяти.

- •Алгоритмы замещения информационных блоков в кэш-памяти: назначение, виды, реализация.

- •Согласование содержимого кэш-памяти и оп. Стратегии записи в кэш-памяти.

- •Многоуровневая кэш-память. Принстонская и гарвардская архитектуры кэш-памяти.

- •Виртуализация памяти компьютеров: предпосылки внедрения, принцип реализации, виды виртуальной памяти.

- •Концепция страничной организации памяти. Взаимодействие виртуальной памяти с кэш-памятью.

- •Ограничения страничной организации памяти. Сегментация памяти.

- •Проблемы динамического распределения памяти при сегментации. Сегментно-страничная организация памяти.

- •Метод колец защиты памяти.

- •Метод граничных регистров памяти.

- •Защита памяти по ключам.

- •Концепция raid: принципы построения массивов дисковой памяти, назначение, способы реализации.

- •Дисковые массивы raid уровней 0, 1, 10: назначение, принципы реализации, свойства.

- •Дисковые массивы raid уровней 5, 6: назначение, принципы реализации, свойства.

- •Многопортовые озу и озу типа fifo.

- •Прерывания: фаза прерывания, поток данных, классы прерываний.

- •Арифметический конвейер: назначение, принципы реализации. Понятие суперконвейера.

- •Конвейерная обработка данных: предпосылки внедрения, принципы реализации, способы синхронизации ступеней.

- •Синхронный конвейер: реализация 6-ступенчатого конвейера, метрики эффективности, оценка выигрыша от внедрения.

- •Виды рисков синхронного конвейера.

- •Методы снижения приостановок конвейера.

- •Risc-архитектура: предпосылки создания, принципы реализации.

- •Risc-архитектура: средства оптимизации использования регистров.

- •Параллелизм уровня команд. Концепция vliw-архитектуры.

- •Суперскалярные компьютеры: принципы построения, структура процессора.

Основная память компьютера: назначение, типы запоминающих устройств, способы организации

ОП - единственный вид памяти (за исключением регистров), к которой ЦП может обращаться непосредственно. Информация, хранящаяся на внешних ЗУ, становится доступной процессору только после того, как будет переписана в основную память. Реализуется на основе запоминающих устройств с произвольным доступом.

Типы ЗУ:

- оперативное ЗУ (ОЗУ, RAM – random access memory – некорректное название):

Свойства:

= допускает как запись, так и считывание информации;

= обе операции выполняются однотипно, практически с одной и той же скоростью;

= операции производятся с помощью электрических сигналов.

ОЗУ может быть энергозависимым (большинство) и энергонезависимым. Энергозависимые ОЗУ, по сравнению с энергозависимыми, имеют бОльшую емкость, небольшое энергопотребление и высокое быстродействие.

Энергозависимые ЗУ:

- динамическая память (DRAM – Dynamic Random, Access Memory) – хранит информацию короткий промежуток времени, по истечение которого информация должна быть восстановлена, запоминающий элемент выполнен из конденсатора или запирающего транзистора.

- статическая память (SRAM – Static Random Access Memory) – при наличии питания хранит информацию неограниченно долго, выполняется на основе триггера (4/6 транзисторов);

Энергонезависимые ОЗУ - NVRAM – Non-Volatile RAM. От перепрограммируемых ПЗУ отличаются отсутствием этапа стирания информации.

- постоянное ЗУ (ПЗУ) – энергонезависимая память. Обеспечивает только считывание информации. Некоторые ПЗУ позволяют изменение информации но процесс записи –

«программирование» - сильно отличается от считывания и требует значительно больше времени. По возможности программирования ПЗУ бывают:

- программируемые при изготовлении;

- однократно программируемые (после изготовления);

- многократно программируемые.

Способ организации памяти зависит от методов размещения и поиска информации в запоминающем массиве. По этому признаку различают память:

- адресную;

- ассоциативную;

- стековую.

Адресная организация памяти компьютера.

Размещение и поиск информации в запоминающем массиве (ЗМ) основаны на использовании адреса хранения слова. Адресом служит номер ячейки ЗМ, в которой это слово размещается. При записи (или считывании) слова в ЗМ инициирующая эту операцию команда должна указывать адрес, по которому производится запись (считывание).

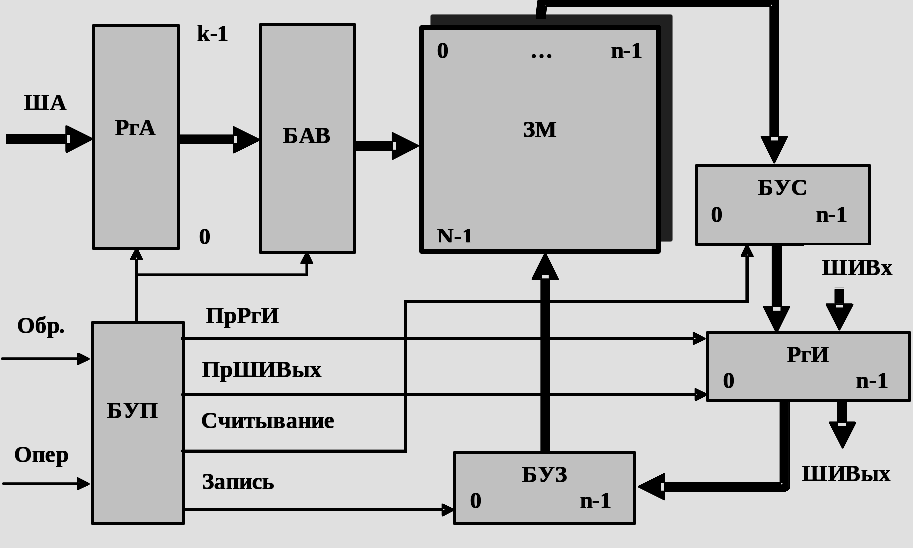

Адресная память с произвольной выборкой содержит запоминающий массив из N n-разрядных ячеек и его аппаратурное обрамление, включающее в себя:

- регистр адреса РгА, имеющий k (k ≥ log2N) разрядов;

- информационный регистр РгИ;

- блок адресной выборки БАВ;

- блок усилителей считывания БУС;

- блок разрядных усилителей формирователей сигналов записи БУЗ;

- блок управления памятью БУП.

По коду адреса в РгА БАВ формирует в соответствующей ячейке памяти сигналы, позволяющие произвести в ячейке считывание или запись слова. БУП генерирует необходимые последовательности управляющих сигналов, инициирующих работу отдельных узлов памяти.