- •Интегральные схемы и их элементы

- •Вопрос 1

- •Вопрос 2

- •Общие сведения о логических элементах

- •Вопрос 1

- •Вопрос 2.

- •Логические элементы в униполярных транзисторах

- •Вопрос 1

- •Вопрос 2

- •Вопрос 3 Элементы интегральной инжекционной логики

- •Логические элементы на мдп-транзисторах

- •Вопрос 2: лэ на комплементарных мдп-транзисторах

- •Согласование связей в цифровых устройствах (цу)

- •1.Типы выходных каскадов

- •2.Преобразователи уровней

- •3.Цепь питания

- •4.Оптоэлектронные развязки

- •Методика синтеза комбинационных схем

- •4.Построение схемы на заданных лэ

- •4.1. На и, или, Не без ограничения на количество входов

- •Анализ комбинационных схем

- •Функциональные узлы комбинационного типа

- •Вопрос 1.

- •Вопрос 2

- •Вопрос 3.

- •Вопрос 4.

- •Вопрос 5. Цифровые компараторы

- •Вопрос 6. Сумматоры

- •Цифровые устройства комбинационного типа

- •Вопрос 1. Алу

- •Вопрос 2. Матричные умножители

- •Методика синтеза цифровых автоматов с памятью

- •Вопрос 1. Понятие ца с памятью

- •Вопрос 2. Способы задания ап

- •Вопрос 3. Элементарные цАсП

- •Вопрос 4. Канонический метод синтеза цАсП

- •Триггеры

- •Вопрос 1. Общие сведения о триггерах

- •Вопрос 2. Одноступенчатые триггеры

- •Вопрос 3.Двухступенчатые триггеры

Вопрос 2: лэ на комплементарных мдп-транзисторах

Основной логического элемента является ключ на комплементарной паре МДП-транзисторов с индуцированном каналом (один канал n-типа, другой p-типа). В таких ЛЭ напряжение низкого уровня практически 0, а напряжение высокого практически напряжение питания.

В качестве примера разберем схему базового элемента КМОПТЛ

VT1, VT2 – n канальные

VT3, VT4 – p канальные

Принцип действия:

Х1=х2=0В= U0 VT1, VT2 – закрыт (Uзи1=Uзи2<Uзи пор), VT3,Vt4 – открыты (Uзи1=Uзи2>Uзи пор). Выход = U1= Uп

Х1=х2=U1 Vt1, Vt2 открыт, Vt3,Vt4 закрыты. Выход U0

На одном U0, на другом U1. Vt1 или Vt2 открыт и выход ЛЭ подключен к земле, а Vt3 ил Vt4 закрыт и выход ЛЭ отключен от Uп. На выходе 0В

В любом из этих состояний сквозной ток через ЛЭ не протекает.

Выполняемая логическая операция: ИЛИ-НЕ

X1 |

X2 |

Y |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

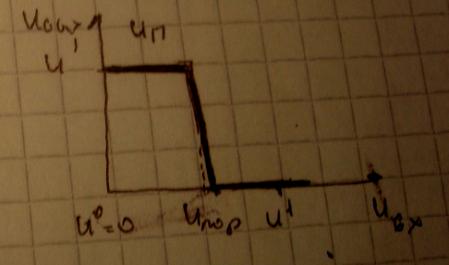

Передаточная характеристика

Примеры: серии 164, 176, 561, 564, 1561, 1564

Достоинства:

Самая хорошая помехоустойчивость;

Высокая плотность упаковки

Минимальная потребляемая мощность

Относительное малое выходное сопротивление, так как у всех транзисторов короткий и широкий канал, за счет чего быстродействие растёт (ед-дес нс)

Недостаток: *можно считать, что их нет.

28022012 Лекция 5

Согласование связей в цифровых устройствах (цу)

Вопросы:

Типы выходных каскадов

Преобразование уровней

Цепи питания

Оптоэлектронные развязки

1.Типы выходных каскадов

Логический выход

Формируется 2 уровнями вых «И»: низкий И высокий И.

Такой выход имеет большинство ЛЭ, используемых в комбинационных схемах.

Для обеспечения быстрого перезаряда Cн, подключаемого к выходному каскаду, и повышения быстродействия выходное сопротивление Rвых должно быть небольшим.

В ЛЭ ТТЛ/ТТЛШ к КМПОТЛ обеспечивают применением к выходной цепи 2х транзисторов, которые при любом направлении переключения находятся в активном режиме и работают противофазно.

Выходная цепь ЛЭ ТТЛ/ТТЛШ

Особенность:

Нельзя соединить параллельно, так как если ЛЭ формируют различные уровни Uвых, то в точке их соединения возникает неопределённость. При параллельном соединении в выходных цепях могут возникать перегрузки с последующим нарушением работоспособности ЛЭ.

При переключении ЛЭ из одного состояния в другое в течение некоторого времени оба транзистора открыты, что приводит к появлению в выходной цепи короткого импульса сквозного тока значительной величины.

1.2.Элементы с 3мя состояниями выхода (типа ТС)

Кроме логических состояний «0» и «1» имеется и третье состояние «отключено», при котором ток в выходной цепи пренебрежительно мал. Состояние обеспечивается переходом в закрытое состояние транзисторов схемы на рисунке к п.1.1.

Для этой цепи на элементе типа ТС подаётся специальный управляющий сигнал ОЕ (output enable). При сигнале ОЕ =1, элемент находится в состоянии логической операции. При ОЕ=0 – в состоянии «отключено».

Различают 4 типа буферных каскадов с третьим состоянием:

Выходы и управляющие входы буферов могут быть инвертирующими и не инвертирующими.

Применяются для управления передачи сигнала по тем или иным линиям.

Выходы типа ТС обозначаются или Z.

В отличие от логических выходов, выходы типа ТС можно соединять параллельно, при условии, что в каждый момент времени активным является только один из них. Из этого следует применение ТС в магистрально модульных, микропроцессорных и других системах, где многие источники информации поочередно используют одну и ту же линию связи.

1.3.Выход с открытым коллектором (обозначение ◊)

Элементы с ОК имеют в выходной цепи транзистор, управляемый предыдущей частью схемы элемента, коллектор которого не соединен с какими-либо цепями внутри микросхемы.

Выходная цепь цифрового элемента с открытым коллектором

Несколько выходов типа ОК можно соединять параллельно, подключая к источникам питания через общий резистор нагрузки.

Использование элементов с ОК для реализации монтажной логики (соединены параллельно)

Позволяет реализовать режим поочередной работы нескольких элементов на одну шину (аналогично ТС). При этом в качестве разрешенного входа может быть использован один из входов элемента. Для элемента И-НЕ (на рисунке) подав на вход 0 (один из), можно запретить работу элемента. При подаче 1, работа разрешена.

В случае если активными являются несколько элементов, подключенных к общей нагрузке, можно получить дополнительную логическую операцию – операция на монтажной логике.

U1 на выходе схемы возникает только тогда, когда закрыты VTвых всех элементов, так как насыщение хотя бы одного их них снижает Uвых до U0.

U1 на выходе в случае, когда все выходы, подключенные к общей нагрузке имеют 1чное состояние.

В свою очередь каждый

из элементов, имеющий выход типа ЛК,

реализует над входными переменными

операцию И-НЕ. Следовательно, выходная

функция определяется выражением:

Недостатком элементов с ОК является большая задержка переключения, так как перезаряд Cн осуществляется через внешний резистор R, сопротивление которого может быть слишком малым.

1.4.Выход с открытым эмиттером

Характерен для элементов ЭСЛ, в выходных каскадах которых (эмиттерный повторитель) отсутствует резистор эмиттерной нагрузки.

Несколько выходов с ОЭ так же можно соединять параллельно, подключая их к источникам питания через общие внешние резисторы эмиттерной нагрузки.

Соединяя прямые выходы

нескольких элементов, получают единую

дизъюнкцию входных элементов

.

Соединяя инверсные выходы, получают:

.

Соединяя инверсные выходы, получают:

.

.

Операция И-ИЛИ относительно инверсных значений входных элементов.

Если предусмотреть

соединение F1 и F2,

то получим

.

.