- •Интегральные схемы и их элементы

- •Вопрос 1

- •Вопрос 2

- •Общие сведения о логических элементах

- •Вопрос 1

- •Вопрос 2.

- •Логические элементы в униполярных транзисторах

- •Вопрос 1

- •Вопрос 2

- •Вопрос 3 Элементы интегральной инжекционной логики

- •Логические элементы на мдп-транзисторах

- •Вопрос 2: лэ на комплементарных мдп-транзисторах

- •Согласование связей в цифровых устройствах (цу)

- •1.Типы выходных каскадов

- •2.Преобразователи уровней

- •3.Цепь питания

- •4.Оптоэлектронные развязки

- •Методика синтеза комбинационных схем

- •4.Построение схемы на заданных лэ

- •4.1. На и, или, Не без ограничения на количество входов

- •Анализ комбинационных схем

- •Функциональные узлы комбинационного типа

- •Вопрос 1.

- •Вопрос 2

- •Вопрос 3.

- •Вопрос 4.

- •Вопрос 5. Цифровые компараторы

- •Вопрос 6. Сумматоры

- •Цифровые устройства комбинационного типа

- •Вопрос 1. Алу

- •Вопрос 2. Матричные умножители

- •Методика синтеза цифровых автоматов с памятью

- •Вопрос 1. Понятие ца с памятью

- •Вопрос 2. Способы задания ап

- •Вопрос 3. Элементарные цАсП

- •Вопрос 4. Канонический метод синтеза цАсП

- •Триггеры

- •Вопрос 1. Общие сведения о триггерах

- •Вопрос 2. Одноступенчатые триггеры

- •Вопрос 3.Двухступенчатые триггеры

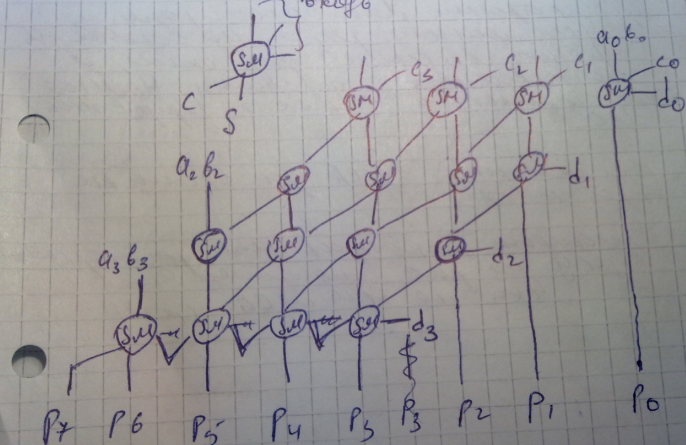

Вопрос 2. Матричные умножители

МУ предназначены для перемножения многоразрядных двоичных чисел (операндов). Появились в 1980ых годах, когда достигнутый уровень интеграции позволил разместить на одном кристалле достаточно большое количество логических элементов. Структура МУ тесно связана со структурой математических выражений, описывающих операцию умножения.

Пусть имеются два целых двоичных числа без знаков Am = am-1…a0 и Bn = bn-1…b0. Их перемножение выполняется по известной схеме «умножения столбиком». Если числа четырехразрядные, то есть m=n=4, то

Рисунок с индексом n

|

|

a3 |

a2 |

a1 |

a0 |

|

b3 |

b2 |

b1 |

b0 |

|||

|

a3b0 |

a2b0 |

a1b0 |

a0a0 |

||

|

a3b1 |

a2b1 |

a1b1 |

a0b1 |

||

a3b2 |

a2b2 |

a1b2 |

a0b2 |

|

||

a3b3 |

a2b3 |

a1b3 |

a0b3 |

|||

p6 |

p5 |

p4 |

p3 |

p2 |

p1 |

p0 |

Результат перемножения выражается числом Pm+n=pm+n-1…p0. Члены вида aibj – частичные произведения. Они могут быть сформированы параллельно во времени конъюнктора. Их сложение в сложение в столбах составляют основную операцию для умножения и определяют почти целиком время умножения.

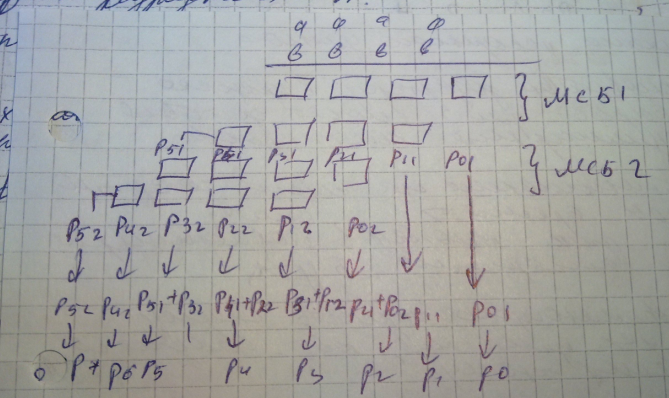

МУ могут выполняться в виде множительных блоков МБ и множительно-суммирующих блоков МСБ.

МСБ реализуют операцию P=Am*Bn + Cm + Dn, то есть существует возможность суммирования произведения и двух слагаемых: одно разрядности m, совпадающей с разрядностью множимого, а другого разрядности n, совпадающей с разрядностью множителя. Благодаря этому обеспечивается удобство наращивания разрядности МУ.

МБ реализует операцию P=Am*Bn.

Структура МСБ для

4хразрядных операндов без набора

конъюнкторов, вырабатывающих частичное

произведение, приведена на рисунке

Для построения МБС чисел равной разрядности n требуется n2 конъюнкторов и n2 одноразрядных сумматоров.

Максимальная длительность определяется tмсб = tk+(2n-1)*tсм

Где tk – задержка в конъюнкторе, tсм – задержка в одноразрядном сумматоре

В общем виде tмсб = tk+(m+n-1)*tсм

Схема МБ отличается от схемы МСБ тем, что в ней нет сумматоров правой диагонали, так как при отсутствии слагаемых C и D они не требуется.

Построение МУ большой размерности из МУ меньшей размерности на основе МБ требует введения дополнительных схем, называемых «Деревьями Уоллиса», которые имеются в некоторых зарубежных сериях интегральных схем. При использовании МСБ дополнительные схемы не требуются.

Принцип наращивания размерности МУ показан на рисунке

На примере умножителя 4х4 из МСБ 4х2

Перемножение в пределах зон даёт частичные произведения p1=p51p41p31p21p11p01 и p2=p52p42p32p22p12p02. Для получения конечного значения произведения эти частичные произведения нужно сложить с учётом их взаимного положения (сдвига одного относительного другого).

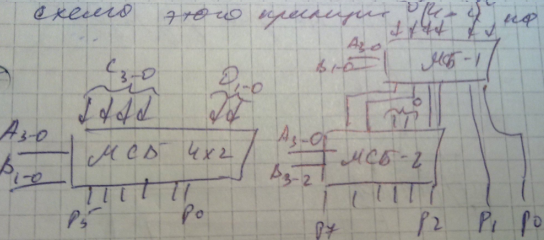

Схема, реализующая данный принцип, показан на рисунке

Построение МУ «4х4» на двух МСБ «4х2» условное графическое обозначение МСБ «4х2» и схема умножителя «4х4».

Схема ускоренного умножения

Основную задержку в процессе выработки произведения вносит суммирование частичных произведений. Уменьшение их числа сократило бы время суммирования. Этот факт положен в основу модифицированного алгоритма Бута, позволяющего строить схемы ускоренного умножения. Процесс ускоренного умножения по алгоритму Бута сводится к следующему: уменьшению числа частных произведений, входящих в состав общего произведения операндов А и В. Если уменьшение вдвое, то говорят об умножении «сразу на два разряда».

Схема умножения «сразу на два разряда»

Множимое А поступает в этой схеме на ряд преобразований, формирующие все возможные варианты частичных произведений, кроме А и 0, которые не требуют аппаратной реализации. Множитель В поступает на логический преобразователь, который анализирует тройки разрядов, декодирует их и даёт мультиплексорам сигналы выбора того или иного варианта частичных произведений. Окончательный результат получается суммированием произведений с учётом сдвига по разрядной сетке 4х4 разрядностью.

Приведенные выше примеры касались операций с прямыми кодами. В этом случае умножение знакопеременных чисел свёдется только к выработке знакового разряда, как суммы по модулю 2 знаковых разрядов множителей. Если же числа представлены не прямыми кодами, то рассмотренные выше умножители можно дополнить преобразователями дополнительного кода в прямые на выходах и преобразователями прямого кода в дополнительный на выходах.

10042012 Лекция 11