- •Интегральные схемы и их элементы

- •Вопрос 1

- •Вопрос 2

- •Общие сведения о логических элементах

- •Вопрос 1

- •Вопрос 2.

- •Логические элементы в униполярных транзисторах

- •Вопрос 1

- •Вопрос 2

- •Вопрос 3 Элементы интегральной инжекционной логики

- •Логические элементы на мдп-транзисторах

- •Вопрос 2: лэ на комплементарных мдп-транзисторах

- •Согласование связей в цифровых устройствах (цу)

- •1.Типы выходных каскадов

- •2.Преобразователи уровней

- •3.Цепь питания

- •4.Оптоэлектронные развязки

- •Методика синтеза комбинационных схем

- •4.Построение схемы на заданных лэ

- •4.1. На и, или, Не без ограничения на количество входов

- •Анализ комбинационных схем

- •Функциональные узлы комбинационного типа

- •Вопрос 1.

- •Вопрос 2

- •Вопрос 3.

- •Вопрос 4.

- •Вопрос 5. Цифровые компараторы

- •Вопрос 6. Сумматоры

- •Цифровые устройства комбинационного типа

- •Вопрос 1. Алу

- •Вопрос 2. Матричные умножители

- •Методика синтеза цифровых автоматов с памятью

- •Вопрос 1. Понятие ца с памятью

- •Вопрос 2. Способы задания ап

- •Вопрос 3. Элементарные цАсП

- •Вопрос 4. Канонический метод синтеза цАсП

- •Триггеры

- •Вопрос 1. Общие сведения о триггерах

- •Вопрос 2. Одноступенчатые триггеры

- •Вопрос 3.Двухступенчатые триггеры

Вопрос 2. Одноступенчатые триггеры

Одна ступень запоминания информации.

2.1.Асинхронные RS-триггеры

Являются простейшими триггерами, которые применяются самостоятельно и на основе которых строятся более сложные схемы триггеров. Асинхронные RS-триггеры имеют два информационных входа: S (set) – установка, R (reset) – сброс.

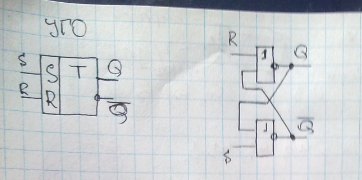

УГО, схема с прямыми входами (на ИЛИ-НЕ)

Таблица переходов

Sn |

Rn |

Qn+1 |

|

0 |

0 |

Qn |

|

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

н/о |

н/о |

УГО, схема с инверсными входами (на И-НЕ)

Таблица переходов

Sn |

Rn |

Qn+1 |

|

0 |

0 |

н/о |

н/о |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

Qn |

|

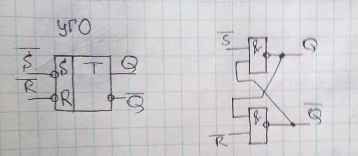

2.2.Сихронный RS-триггер

Схема и УГО

Таблица переходов

Cn |

Sn |

Rn |

Qn+1 |

|

0 |

0 |

0 |

Qn |

|

0 |

0 |

1 |

Qn |

|

0 |

1 |

0 |

Qn |

|

0 |

1 |

1 |

Qn |

|

1 |

0 |

0 |

Qn |

|

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

н/о |

н/о |

При наличии на синхровходе сигнала = 1 схема функционирует как асинхронных RS-триггер с прямыми входами. Если же С=0, то триггер не меняет своего состояния при любой комбинации сигналов на входах S и R, так как в этом случае q1=q2=q=1, что являестя нейтральным набором для асинхронного RS-триггера с инверсными входами, выполненного на элементах DD3 и DD4. Сигналы на информационных входах R и S подготавливают триггер к срабатыванию, тогда как непосредственно срабатывание происходит в момент поступления синхроимпульсов на вход С.

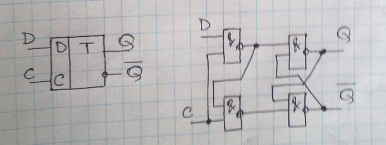

2.3.Синхронный D-триггер

Триггер при наличии синхросигнала на входе С устанавливается в состояние, соответствующее значению сигнала на информационном входе D. Обозначение входа D происходит от слова delay (задержка).

А если С=0, то триггер не изменяет своего действия при любом значении сигнала на входе D.

Схема и УГО со статических сходов синхронизации

Таблица переходов

Сn |

Dn |

Qn+1 |

|

0 |

0 |

Qn |

|

0 |

1 |

Qn |

|

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

Особенность: если во время действия импульса синхронизации изменяется значение сигнала на входе D, то изменение передается на выход. Если такое явление не желательно, то используется D-триггер с динамическим синхровходом.

УГО с динамическим входов синхронизации

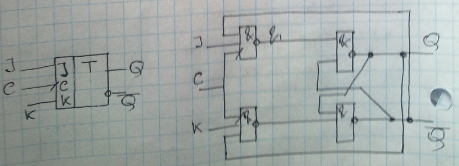

2.4.Синхронный JK-триггер

Триггер имеет информационные входы J и K и динамический синхровход С. Обозначения входов J и K происходит от слов jump (прыжок) и keep (держать). J аналогичен S, K – R, за исключением комбинации с двумя единицами, которая не является запрещённой, а приводит к изменению состояния триггера на противоположное.

УГО и схема

Таблица переходов

Cn |

Sn |

Rn |

Qn+1 |

|

0 |

0 |

0 |

Qn |

|

0 |

0 |

1 |

Qn |

|

0 |

1 |

0 |

Qn |

|

0 |

1 |

1 |

Qn |

|

1 |

0 |

0 |

Qn |

|

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

|

Qn |

JK-триггер является универсальным и может быть использован в качестве RS, D, T триггеров.

2.5.Синхронный Т-триггер

Т-триггер имеет один информационный счетный вход и изменяет свое состояние на противоположное под действием каждого счетного импульса.

УГО и схемы

Таблица переходов

Т |

Qn+1 |

|

0 |

Qn |

|

1 |

|

Qn |

Триггер со счетным

входом можно построить на основе

рассмотренных выше триггеров. При

использовании для этой цели D-триггер

в него вводится обратная связь с выхода

на вход D, а вход С

используется в качестве счетного входа.

Аналогичный эффект получается если в

JKтриггере объединить

входы J и K,

приложив к ним высокий уровень напряжения,

соответствующий логической единице, а

счетные импульсы подавать на синхровход

С.

на вход D, а вход С

используется в качестве счетного входа.

Аналогичный эффект получается если в

JKтриггере объединить

входы J и K,

приложив к ним высокий уровень напряжения,

соответствующий логической единице, а

счетные импульсы подавать на синхровход

С.