- •Схемотехника систем управления

- •1. Устройства числового программного управления

- •1.1. Задачи, решаемые учпу

- •Функции учпу

- •Структура учпу

- •2. Основные вопросы организации системных интерфейсов

- •Термины и определения, используемые в интерфейсах

- •2.2. Характеристики интерфейсов

- •2.3. Классификация интерфейсов

- •2.4. Управление обменом в системных интерфейсах

- •Программно-управляемая передача данных

- •Синхронный обмен

- •2.4.3. Асинхронный обмен

- •2.4.4. Обмен в режиме прерывания программы

- •Программный опрос

- •Опрос по дейзи-цепочке

- •Прерывание по вектору

- •Многоуровневые прерывания

- •Прямой доступ к памяти

- •3. Интерфейс магистральный параллельный

- •3.1. Назначение, принцип действия, основные характеристики

- •3.2. Одиночный адресный обмен

- •3.3. Одноуровневая процедура прерывания

- •3.4. Процедура передачи управления магистралью

- •4. Интерфейс и41

- •4.1. Назначение, принцип действия и характеристика интерфейса

- •4.2. Порядок обмена сообщениями

- •4.3. Операции прерывания

- •4.4. Операции смены задатчика

- •5. Модули микропроцессорных систем управления типа cnc

- •5.1. Модули вввода дискретных сигналов

- •5.2. Модули вывода управляющих сигналов

- •5.3. Модули адаптивного управления

- •5.4. Модули управления приводами

- •5.5. Модули измерительных преобразователей

- •5.6. Модули связи с оператором

- •6. Интерфейс магистральный последовательный гост 26765.52-87

- •7. Интерфейс rs-232c

- •8. Микросхемы малой степени интеграции и особенности их использования в су

- •8.1. Логические элементы с открытым коллектором

- •8.2. Дешифраторы адреса

- •8.3. Организация управления в схемах модулей связи с объектом

- •9. Диагностика работоспособности технологического оборудования

- •10. Общие сведения о системе проектирования печатных плат pcad

- •Графический редактор принципиальных схем pcad Schematic

- •Графический редактор печатных плат pcad рсв

- •Разработка принципиальных электрических схем в pcad Schematic

- •Разработка печатных плат в pcad pcb

- •Оптимизация расположения компонентов по команде Utils/Optimize Nets, если необходимо.

- •Разработка электронных компонентов для саппп pcad

- •Библиографический список

8.2. Дешифраторы адреса

Дешифратор адреса (ДА) модуля связи с объектом (МСО) предназначен для выборки одного или нескольких адресов из всего адресного пространства устройств ввода/вывода МПС. На рис. 8.2.1 показана структурная схема ДА 10х4 (10 линий шины адреса (ША) и 4 адреса, выбираемые из данного адресного пространства).

Рис. 8.2.1. Структурная схема дешифратора адреса в МСО

В

Рис. 8.2.2. Схема формирования «1» или «0»

в ЗА

В схеме сравнения сравнивается адрес модуля с ЗА и адрес, выставляемый в данный момент процессором на ША. При равенстве кодов формируется сигнал разрешения дешифрации (РД), который выдаётся в схему DC. Схема сравнения может быть выполнена на базе микросхем: логических элементов, дешифраторов (DC), мультиплексоров (МХ), компараторов кодов, ПЗУ либо ППЗУ. DC дешифрирует двоичный код адреса, подаваемый на его входы, в сигналы ADR выбора элементов в данном модуле. Линии ША, подаваемые на вход DC, определяют адреса занимаемые элементами модуля в адресном пространстве устройств ввода/вывода. ДА на рис. 8.2.1 из адресного пространства $3FF-$000 выбирает адреса $3F3-$3F0.

Ниже на рис. 8.2.4 – рис. 8.2.9 показаны примеры принципиальных электрических схем построения ДА на различных микросхемах. Для удобства рассмотрения в примерах используется это же адресное пространство $3FF–$000 устройств ввода/вывода, из которого выбирается четыре адресуемых элемента соответствующего модуля. При выборе схемы необходимо учитывать не только простоту его решения (количество микросхем, соответственно стоимость), но и временные характеристики дешифрации адреса. ДА должен дешифрировать адрес за время не более чем интервал между выставлением адреса и началом строба обмена (сигнал /ОБМ в интерфейсе МПИ (рис. 8.2.3 а) и /IORC, /IOWC в И41 (рис. 8.2.3 б)). При разработке ДА необходимо помнить о том, что при наличии большого числа модулей в системе управления, необходимо стремиться к тому, чтобы каждая линия ША не нагружалась двумя входами ДА. Это понижает нагрузку на линии ША. При необходимости сигнал ША усиливается логическим элементом (инвертором или повторителем), а затем к выходу усилителя подключаются необходимые входы ДА.

При разработке МСО также необходимо учитывать требование - на все свободные входы МС подаются логический "0" или "1" с учётом их функционального назначения т.е. МС должна остаться работоспособной.

Рис. 8.2.3. Стробы обмена в интерфейсах: а) – МПИ, б) – И41

При построении ДА на логических элементах может использоваться любая логика. Наиболее простое решение получается при применении элементов «Исключающее ИЛИ» (рис. 8.2.4). В данной схеме задатчик адреса выполнен на 8-разрядной сборке микропереключателей SA1. Разомкнутое состояние контактов обеспечивает подачу через резисторы RR1 на входы микросхем логических «1». При замыкании контактов микропереключателей на соответствующих входах устанавливается логический «0». Схема сравнения выполнена на микросхемах D1, D2 «Исключающее ИЛИ» и D3 «И-НЕ». Дешифрация линий А0 и А1 шины адреса во всех схемах, приводимых ниже, осуществляется микросхемой D4 (дешифратор DC).

Временные параметры работы ДА при установке адреса на ША и снятии в данной схеме рассчитываются по формулам (здесь и далее параметры дешифраторов рассчитываются применительно к микросхемам серии КР1533):

![]() ;

;

![]() .

.

Рис. 8.2.4. Дешифратор адреса на МС «Исключающее ИЛИ», «И-НЕ» и DC

На рис. 8.2.5 приведён ДА, выполненный на инверторах, схеме «И-НЕ» и DC. Так как в схеме каждая линия шины адреса подключается к двум входам микросхем, необходимо усиление сигналов ША, которое выполняется инверторами D1, D5.1 и D5.2. Задатчик адреса выполнен на сборках микропереключателей SA1 и SA2 и инверторах D2, D5.3 и D5.4. Функции схемы сравнения выполняет микросхема D3 (И-НЕ). На выходе DC сформируется соответствующий сигнал ADR, когда на все входы «И-НЕ» поступят «1».

Время дешифрации и снятия адреса определяются выражениями:

![]() ;

;

![]() .

.

Рис. 8.2.5. Схема ДА на инверторах, И=НЕ и DC

Дешифратор адреса, выполненный на микросхемах DC, представлен на рис. 8.2.6. Задание адреса в данной схеме осуществляется установкой перемычек на разъёмах Х1-Х3. Например, при адресе 10-110-001-00, что соответствует кодам 2-6-1-0, перемычки должны быть установлены на следующие выводы разъёмов: 3-14(Х3), 7-10(Х2), 2-15(Х1). Самая большая задержка в данной схеме возникает при прохождении адреса через микросхемы D1, D5.1 и D4.

Временные параметры работы ДА определяются по формулам:

![]() ;

;

![]() .

.

Рис. 8.2.6. Схема ДА на микросхемах DC

Сравнение двоичных кодов можно осуществить с использованием цифровых компараторов (рис. 8.2.7). В данной схеме код адреса, выдаваемый процессором, поступает на входы А3-А0 компараторов, а с ЗА – на В3-В0. При совпадении кодов на выходе «=» формируется «1». Сигналы с выходов компараторов поступают на входы управления DC, разрешая его работу. Задатчик адреса в данной схеме аналогичен ЗА, представленному на рис. 8.2.4.

Задержки дешифратора адреса на микросхемах компараторов при установке и снятии адреса определяются выражениями

![]() ;

;

![]() .

.

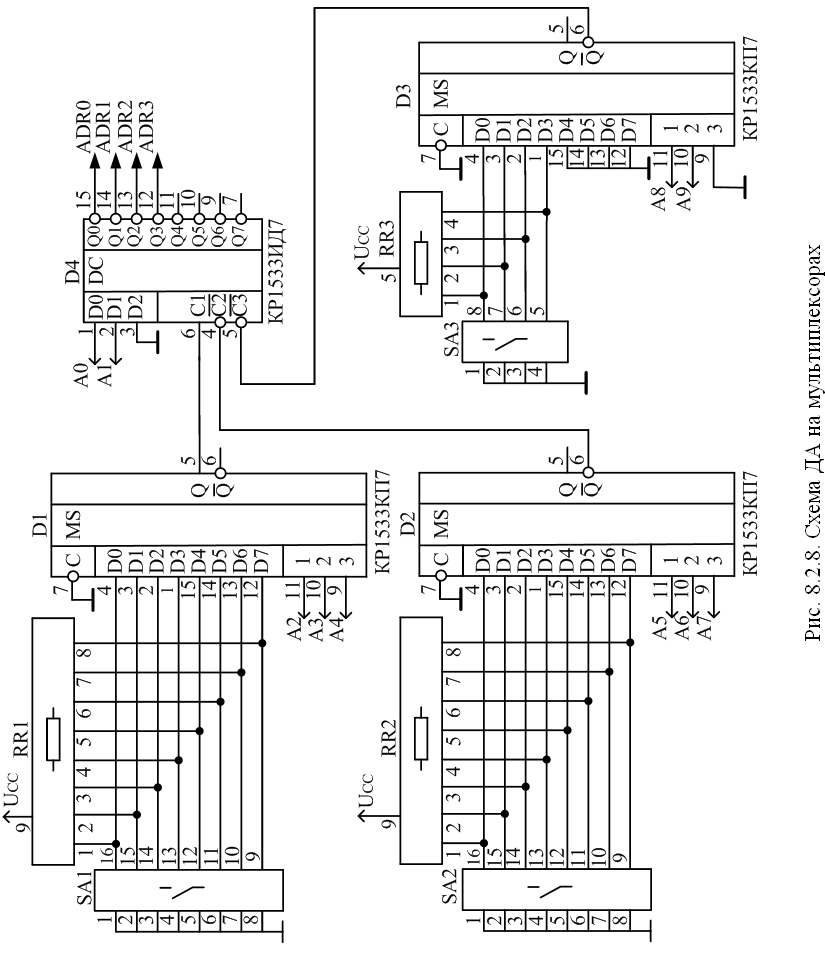

Дешифратор адреса также может быть выполнен на базе микросхем мультиплексоров (рис. 8.2.8). Адрес, выдаваемый процессором, поступает на входы 1, 2, 3 мультиплексоров. Предположим, выдаётся адрес 11-101-100-11. В этом случае необходимо разомкнуть контакты (задать «1»): 4-13 (SA3), 6-11 (SA2), 4-12 (SA1). В этом случае на прямых выходах мультиплексоров формируются «1». Сигналы с выходов мультиплексоров поступают на входы управления DC, разрешая его работу. Задатчик адреса в схеме аналогичен задатчику, приведённому на рис. 8.2.4.

Рис. 8.2.7. Схема ДА на цифровых компараторах

Временные параметры работы ДА на мультиплексорах при установке и снятии адреса процессором рассчитываются с учётом их максимальных значений:

![]() ;

;

![]() .

.

П ри

выполнении дешифратора адреса на

микросхемах памяти ПЗУ или ППЗУ задатчик

адреса, схема сравнения и DC

реализуются программно, т.е. прошивкой

ПЗУ. Схема ДА 16х4 на базе МС ПЗУ КР556РТ

представлена на рис. 8.2.9. На выходах МС

необходимо устанавливать резисторы

R1÷R4, так

как выходы МС с открытым коллектором и

их объединение осуществляется по схеме

"Монтажное И". ДА на МС ПЗУ

целесообразно использовать в тех

случаях, когда заранее известны количество

адресов и их значения в МСО. Микросхема

программируется перед установкой на

плату. При отсутствии данной информации

МС памяти должны располагаться на панели

и у потребителя должен быть соответствующий

программатор ПЗУ.

ри

выполнении дешифратора адреса на

микросхемах памяти ПЗУ или ППЗУ задатчик

адреса, схема сравнения и DC

реализуются программно, т.е. прошивкой

ПЗУ. Схема ДА 16х4 на базе МС ПЗУ КР556РТ

представлена на рис. 8.2.9. На выходах МС

необходимо устанавливать резисторы

R1÷R4, так

как выходы МС с открытым коллектором и

их объединение осуществляется по схеме

"Монтажное И". ДА на МС ПЗУ

целесообразно использовать в тех

случаях, когда заранее известны количество

адресов и их значения в МСО. Микросхема

программируется перед установкой на

плату. При отсутствии данной информации

МС памяти должны располагаться на панели

и у потребителя должен быть соответствующий

программатор ПЗУ.