- •Схемотехника систем управления

- •1. Устройства числового программного управления

- •1.1. Задачи, решаемые учпу

- •Функции учпу

- •Структура учпу

- •2. Основные вопросы организации системных интерфейсов

- •Термины и определения, используемые в интерфейсах

- •2.2. Характеристики интерфейсов

- •2.3. Классификация интерфейсов

- •2.4. Управление обменом в системных интерфейсах

- •Программно-управляемая передача данных

- •Синхронный обмен

- •2.4.3. Асинхронный обмен

- •2.4.4. Обмен в режиме прерывания программы

- •Программный опрос

- •Опрос по дейзи-цепочке

- •Прерывание по вектору

- •Многоуровневые прерывания

- •Прямой доступ к памяти

- •3. Интерфейс магистральный параллельный

- •3.1. Назначение, принцип действия, основные характеристики

- •3.2. Одиночный адресный обмен

- •3.3. Одноуровневая процедура прерывания

- •3.4. Процедура передачи управления магистралью

- •4. Интерфейс и41

- •4.1. Назначение, принцип действия и характеристика интерфейса

- •4.2. Порядок обмена сообщениями

- •4.3. Операции прерывания

- •4.4. Операции смены задатчика

- •5. Модули микропроцессорных систем управления типа cnc

- •5.1. Модули вввода дискретных сигналов

- •5.2. Модули вывода управляющих сигналов

- •5.3. Модули адаптивного управления

- •5.4. Модули управления приводами

- •5.5. Модули измерительных преобразователей

- •5.6. Модули связи с оператором

- •6. Интерфейс магистральный последовательный гост 26765.52-87

- •7. Интерфейс rs-232c

- •8. Микросхемы малой степени интеграции и особенности их использования в су

- •8.1. Логические элементы с открытым коллектором

- •8.2. Дешифраторы адреса

- •8.3. Организация управления в схемах модулей связи с объектом

- •9. Диагностика работоспособности технологического оборудования

- •10. Общие сведения о системе проектирования печатных плат pcad

- •Графический редактор принципиальных схем pcad Schematic

- •Графический редактор печатных плат pcad рсв

- •Разработка принципиальных электрических схем в pcad Schematic

- •Разработка печатных плат в pcad pcb

- •Оптимизация расположения компонентов по команде Utils/Optimize Nets, если необходимо.

- •Разработка электронных компонентов для саппп pcad

- •Библиографический список

8. Микросхемы малой степени интеграции и особенности их использования в су

8.1. Логические элементы с открытым коллектором

Логические элементы с открытым коллектором (ЛЭ с ОК) имеют на выходе транзистор, у которого в корпусе микросхемы (МС) отсутствует нагрузка в цепи коллектора. При использовании данного ЛЭ для реализации логической функции к выходу необходимо подключить внешний нагрузочный резистор (рис. 8.1.1). Напряжение UCC должно соответствовать напряжению питания микросхемы. Некоторые МС с открытым коллектором, разработанные для преобразователей уровней напряжения, допускают подключение напряжения UCC более напряжения питания МС. Открытый коллектор в МС позволяет разработчику СУ использовать данный элемент для реализации специальных функций. Некоторые из них рассмотрены ниже.

На рис. 8.2 приведена схема управления светодиодом VD. Управление осуществляется током нуля I0 = IVD = IRn логического элемента, который обычно на порядок больше тока «1» и составляет от нескольких десятков до сотни мА. Резистор Rn в схеме необходим для ограничения тока до значения IVD, определяемого вольтамперной характеристикой светодиода.

Рассмотрим пример управления светодиодом АЛ307А от МС КР1533ЛН2. Для этого необходимо рассчитать нагрузочный резистор Rn (рис. 8.1.2). Исходные данные для расчёта: IVD = 10 мА, UCC = 5 В.

Расчёт ведётся в следующей последовательности:

по вольтамперной характеристике светодиода (рис. 8.1.3) [10], находится падение напряжения UVD при заданном значении тока (UVD = 2 B);

по справочным данным МС [9] U0 = 0,4 B;

падение напряжения на Rn определяется выражением

URn = UCC – UVD – U0 = 5 – 2 – 0,4 = 2,6 В;

сопротивление Rn по закону Ома равно

Rn = URn / IVD = 2,6 / 0,01 = 260 Ом;

по стандартному ряду [12] выбирается ближайший резистор Rn =260 Ом ;

определяется мощность резистора

PRn = URn • IVD = 2,6 • 0,01 = 0,026 Вт;

по результатам расчёта выбирается нагрузочный резистор Rn

МЛТ 0,063 Вт – 260 Ом ± 10%.

Аналогично осуществляется управление

слаботочными реле (рис. 8.1.4). Расчёт

нагрузочного резистора ведётся исходя

из значения тока срабатывания реле.

Если рабочее напряжение реле UK=UCC,

то нагрузочный резистор не устанавливается.

Для защиты МС от ЭДС самоиндукции,

возникающей в обмотке реле при выключении

питания, необходимо параллельно реле

устанавливать шунтирующий диод VD.

Аналогично осуществляется управление

слаботочными реле (рис. 8.1.4). Расчёт

нагрузочного резистора ведётся исходя

из значения тока срабатывания реле.

Если рабочее напряжение реле UK=UCC,

то нагрузочный резистор не устанавливается.

Для защиты МС от ЭДС самоиндукции,

возникающей в обмотке реле при выключении

питания, необходимо параллельно реле

устанавливать шунтирующий диод VD.

Во всех схемах подключения внешних нагрузок к логическим элементам с открытым коллектором необходимо чтобы ток, протекающий через нагрузку был меньше тока I0 МС.

М

Рис. 3.

В схеме "Монтажное И" выходы МС

объединяются и подключаются через

нагрузочный резистор Rn

к источнику питания UCC

(рис. 8.1.6). Наличие хотя бы одного сигнала

низкого уровня на входе приводит к

формированию низкого уровня на выходе.

Данная схема в СУ может использоваться

для формирования внутри МСО сигналов:

/ОТВ (ОТВЕТ), /ЗПР4 (ЗАПРОС ПРЕРЫВАНИЯ),

/ЗМ ( ЗАПРОС

МАГИСТРАЛИ), /ПЗ (ПОДТВЕРЖДЕНИЕ ЗАПРОСА)

в интерфейсе МПИ; /ХАСК (ПОДТВЕРЖДЕНИЕ

ПЕРЕДАЧИ), /INT7-/INT0

(ЗАПРОСЫ ПРЕРЫВАНИЯ) и т.д. Аналогично

по схеме "Монтажное И" объединяются

выходы указанных выше сигналов на

магистральных линиях соответствующих

интерфейсов (рис. 8.6). На концах магистральных

линий интерфейсов присутствуют делители

R1 и R2,

формирующие при отсутствии сигналов с

МСО высокий уровень (логический "0").

ЗАПРОС

МАГИСТРАЛИ), /ПЗ (ПОДТВЕРЖДЕНИЕ ЗАПРОСА)

в интерфейсе МПИ; /ХАСК (ПОДТВЕРЖДЕНИЕ

ПЕРЕДАЧИ), /INT7-/INT0

(ЗАПРОСЫ ПРЕРЫВАНИЯ) и т.д. Аналогично

по схеме "Монтажное И" объединяются

выходы указанных выше сигналов на

магистральных линиях соответствующих

интерфейсов (рис. 8.6). На концах магистральных

линий интерфейсов присутствуют делители

R1 и R2,

формирующие при отсутствии сигналов с

МСО высокий уровень (логический "0").

При формировании сигнала /ОТВ а также в некоторых других случаях возникает необходимость организовать задержку прохождения сигнала. Задержка может быть сформирована с использованием RC-цепочки, МС таймеров либо логическими элементами. Недостатком RC-цепочки является её зависимость от внешних условий. МС таймеров используются при организации больших задержек. Если в проектируемом МСО остаются свободные элементы их можно использовать для организации небольших задержек. При этом может быть сформирована задержка с высокой временной стабильностью.

Рассмотрим пример формирования сигнала /ОТВ в интерфейсе МПИ с необходимой задержкой. При этом необходимо учитывать следующее: сигналы интерфейса МПИ имеют низкий активный уровень; последняя МС, используемая для формирования сигнала /ОТВ должна быть с открытым коллектором.

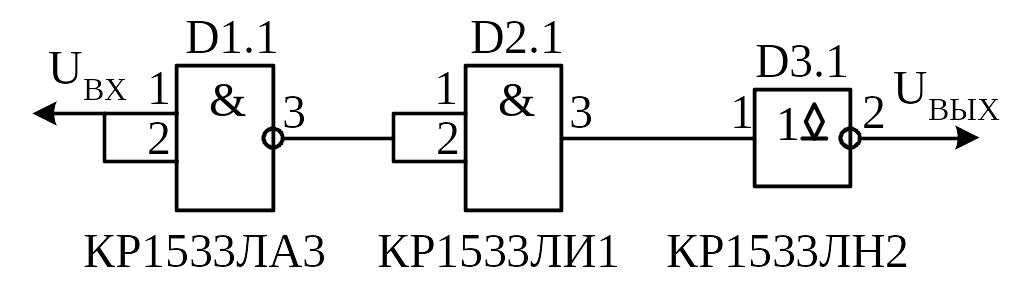

Задержка в примере реализуется на МС КР1533ЛА3, КР1533ЛИ1, КР1533ЛН2. Схема формирования сигнала /ОТВ (UВЫХ) с необходимой задержкой представлена на рис. 8.1.7.

Рис. 8.1.7. Пример схемы формирования сигнала /ОТВ

В соответствии с логическими функциями

МС временные диаграммы входного и

выходного сигналов имеют вид, показанный

на рис. 8.1.8.

соответствии с логическими функциями

МС временные диаграммы входного и

выходного сигналов имеют вид, показанный

на рис. 8.1.8.

Рассчитаем задержки сигнала UВЫХ при установке сигнала UВХ и его снятии:

![]() ;

;

![]() .

.