- •Схемотехника систем управления

- •1. Устройства числового программного управления

- •1.1. Задачи, решаемые учпу

- •Функции учпу

- •Структура учпу

- •2. Основные вопросы организации системных интерфейсов

- •Термины и определения, используемые в интерфейсах

- •2.2. Характеристики интерфейсов

- •2.3. Классификация интерфейсов

- •2.4. Управление обменом в системных интерфейсах

- •Программно-управляемая передача данных

- •Синхронный обмен

- •2.4.3. Асинхронный обмен

- •2.4.4. Обмен в режиме прерывания программы

- •Программный опрос

- •Опрос по дейзи-цепочке

- •Прерывание по вектору

- •Многоуровневые прерывания

- •Прямой доступ к памяти

- •3. Интерфейс магистральный параллельный

- •3.1. Назначение, принцип действия, основные характеристики

- •3.2. Одиночный адресный обмен

- •3.3. Одноуровневая процедура прерывания

- •3.4. Процедура передачи управления магистралью

- •4. Интерфейс и41

- •4.1. Назначение, принцип действия и характеристика интерфейса

- •4.2. Порядок обмена сообщениями

- •4.3. Операции прерывания

- •4.4. Операции смены задатчика

- •5. Модули микропроцессорных систем управления типа cnc

- •5.1. Модули вввода дискретных сигналов

- •5.2. Модули вывода управляющих сигналов

- •5.3. Модули адаптивного управления

- •5.4. Модули управления приводами

- •5.5. Модули измерительных преобразователей

- •5.6. Модули связи с оператором

- •6. Интерфейс магистральный последовательный гост 26765.52-87

- •7. Интерфейс rs-232c

- •8. Микросхемы малой степени интеграции и особенности их использования в су

- •8.1. Логические элементы с открытым коллектором

- •8.2. Дешифраторы адреса

- •8.3. Организация управления в схемах модулей связи с объектом

- •9. Диагностика работоспособности технологического оборудования

- •10. Общие сведения о системе проектирования печатных плат pcad

- •Графический редактор принципиальных схем pcad Schematic

- •Графический редактор печатных плат pcad рсв

- •Разработка принципиальных электрических схем в pcad Schematic

- •Разработка печатных плат в pcad pcb

- •Оптимизация расположения компонентов по команде Utils/Optimize Nets, если необходимо.

- •Разработка электронных компонентов для саппп pcad

- •Библиографический список

3.4. Процедура передачи управления магистралью

Процедура передачи управления используется в интерфейсе МПИ для построения многопроцессорной системы. В составе такой системы имеются общие ресурсы (память, устройства ввода/вывода), доступ к которым и обеспечивает данная процедура. Передача управления в системе от одного активного устройства к другому невозможна, а осуществляется только через процессор.

На рис. 3.11 приведена обобщённая схема организации передачи управления, поясняющая использование необходимых сигналов.

Рис. 3.11. Схема организации передачи управления магистралью

При передаче управления активное устройство, запрашивающее магистраль у процессора, выполняет действия в соответствии с временной диаграммой, приведённой на рис. 3.12, в следующей последовательности:

- каждое активное устройство, готовое стать ведущим в обмене, выдаёт сигнал запроса магистрали /ЗМ;

- процессор параллельно с выполнением текущей программы анализирует состояние линии /ЗМ и при появлении на ней сигнала вырабатывает сигнал /РЗМ (после окончания текущего цикла обмена и при отсутствии /ПЗ). Сигнал /РЗМ последовательно обходит активные устройства, подключённые к магистрали. На входе в устройство он обозначается /РЗМП, на выходе из устройства - /РЗМИ;

- ближайшее по линии /РЗМ активное устройство, выставившее сигнал /ЗМ, при получении сигнала /РЗМП блокирует его дальнейшее распространение и, при отсутствии или при снятии сигналов на линиях /ОТВ и /ОБМ, устанавливает сигнал на линии /ПЗ и сбрасывает сигнал /ЗМ;

- активное устройство, установившее сигнал /ПЗ, становится ведущим и переходит к адресному обмену.

Рис. 3.12. Временная диаграмма передачи управления магистралью

Процессор при необходимости захвата магистрали не выставляет в магистраль сигналы /ЗМ, /РЗМ, /ПЗ, а при отсутствии сигналов /ПЗ, /ОБМ и /ОТВ от других устройств приступает непосредственно к операции назначения ведомого.

Сигнал /ПЗ сбрасывается ведущим после снятия последнего сигнала /ОТВ в ходе выполнения адресного обмена по магистрали.

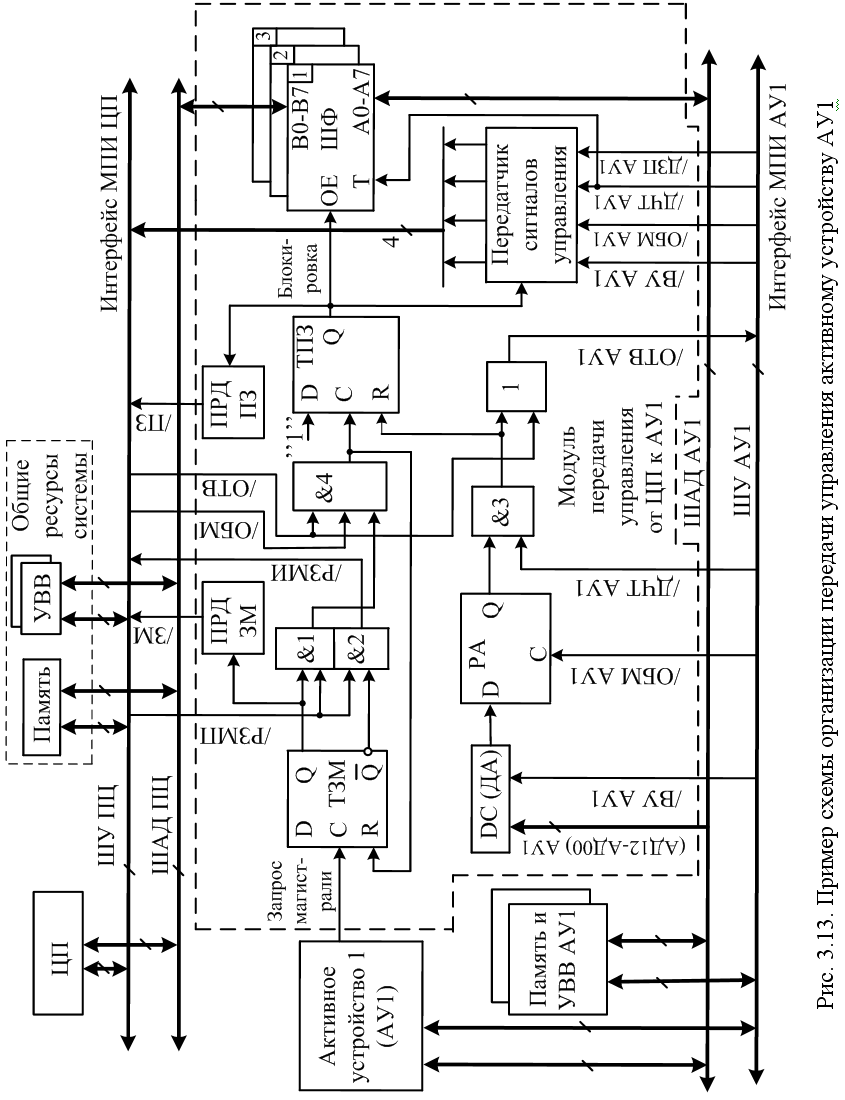

На рис. 3.13 приведён пример схемы передачи управления магистралью от процессора активному устройству У1. Данная операция реализуется следующим образом.

Активное устройство У1, запрашивая магистраль, устанавливает триггер запроса магистрали ТЗМ. Сигналы с его выхода открывают схему &1 и закрывают &2. Одновременно сигнал с прямого выхода триггера ТЗМ поступает на передатчик сигнала запроса магистрали ПРД ЗМ, который выдаёт запрос на линию /ЗМ процессора.

Процессор, получив сигнал /ЗМ, завершает выполнение текущего цикла обмена и выдаёт сигнал /РЗМ. Сигнал /РЗМ последовательно обходит активные устройства, подключённые к магистрали. На входе активного устройства данный сигнал обозначается /РЗМП (П - приёмник), а на выходе - /РЗМИ (И - источник). Сигнал /РЗМП, поступивший в данную схему, проходит через &1 и &4 (/ОБМ и /ОТВ сняты), устанавливает триггер подтверждения запроса ТПЗ и сбрасывает триггер ТЗМ. Сигнал с выхода триггера ТПЗ снимает блокировку с шинных формирователей ШФ и передатчиков сигналов управления, а также поступает на передатчик сигнала подтверждения запроса ПРД ПЗ, который выдаёт его на линию /ПЗ процессора.

Активное устройство У1 становится ведущим и может, например, используя стандартные циклы обмена, записывать информацию в память процессора или читать её из памяти процессора, а также управлять УВВ. Для выполнения данных операций будут задействованы сигналы /ВУ АУ1, /ОБМ АУ1, /ДЧТ АУ1, /ДЗП АУ1, /ОТВ АУ1.

После завершения всех циклов обмена по магистрали процессора активное устройство, используя адресный обмен по своей магистрали, сбрасывает триггер ТПЗ. Для этого используются схемы дешифратора адреса ДА, регистра адреса РА и схема &3. Сброс ТПЗ приводит к блокировке ШФ и передатчиков сигналов.

Сброс сигнала /ПЗ и отсутствие сигналов /ОБМ и /ОТВ разрешают процессору начать адресный обмен по системной магистрали.