- •1.1 Електричні кола постійного струму

- •Електричні кола постійного струму

- •1.1.1 Основні визначення і закони

- •1 Джерела електричної енергії (джерела живлення).

- •1.1.2 Розрахунок лінійних кіл постійного струму з одним джерелом живлення.

- •1.2 Електричні кола змінного струму

- •1.2.1 Поняття про змінний струм

- •1.2.2 Основні поняття синусоїдальної функції

- •1.2.3 Зображення синусоїдальної величини

- •Кутова частота і фазові співвідношення

- •Початковий фазовий кут, або початкова фаза.

- •1.2.4 Прості електричні кола змінного струму

- •1.1 Електронно-дірковий перехід

- •1.1.1 Загальні відомості.

- •1.1.2 Утворення переходу.

- •1.1.3 Контакт метал – напівпровідник.

- •1.2.1 Загальні відомості

- •Продовження таблиці 1.2

- •1.2.2 Характеристики, параметри, область застосування

- •1.3.1 Загальні відомості

- •1.3.2 Фізичні явища й принцип дії бт за схемою із загальним емітером

- •1.3.3 Транзистори Шотки

- •1.3.5 Розрахунок режиму спокою підсилювального каскаду на біполярному транзисторі

- •1.4.1 Загальні відомості

- •1.4.2 Фізичні явища та принцип дії пт

- •1.4.2.1 Польові транзистори з керуючим переходом

- •1.4.2.2 Польові транзистори з ізольованим затвором

- •1.4.3 Лізмон-транзистори

- •1.4.4 Мнон - транзистори

- •3.1 Загальна характеристика імпульсних сигналів і пристроїв

- •3.2 Ключовий режим роботи транзисторів

- •3.3.1 Загальні відомості

- •3.3.2 Логічні елементи в інтегральному виконанні

- •3.3.2.1 Діодно-транзисторні логічні елементи

- •3.3.2.2 Транзисторно логіка -транзисторна

- •3.3.2.3 Логічні елементи на мон-транзисторах

- •3.3.2.4 Логічні елементи на мен-транзисторах

- •3.3.2.5 Інтегральна інжекційна логіка

- •3.3.2.6 Логічні елементи емітерно-зв'язкової логіки

- •3.4.1 Загальні відомості

- •Продовження таблиці 3.3

- •3.4.2 Характерні явища для тригерів

- •Лекція 9 3.5 Компаратори і тригери шмітта, генератори імпульсів

- •3.5.1 Загальні відомості

- •3.5.2 Мультивібратори

- •3.5.3 Одновібратори

- •До пункту 3.5.2

- •3.6 Інтегруючі і диференціюючи rc-ланцюги

- •3.6.1 Інтегруючий rc-ланцюг

- •3.6.2 Диференціюючий rc-ланцюг

- •4.1 Загальні відомості

- •4.2 Однофазний однопівперіодний випрямляч

- •4.3 Однофазний двухпівперіодний випрямляч із нульовим виводом

- •4.4 Однофазний мостовий випрямляч

- •4.5 Випрямлячі - помножувачі напруги

- •4.6 Згладжуючи фільтри

- •4.7.1 Параметричні стабілізатори напруги

- •4.7.2 Компенсаційні стабілізатори напруги

- •Контрольні питання

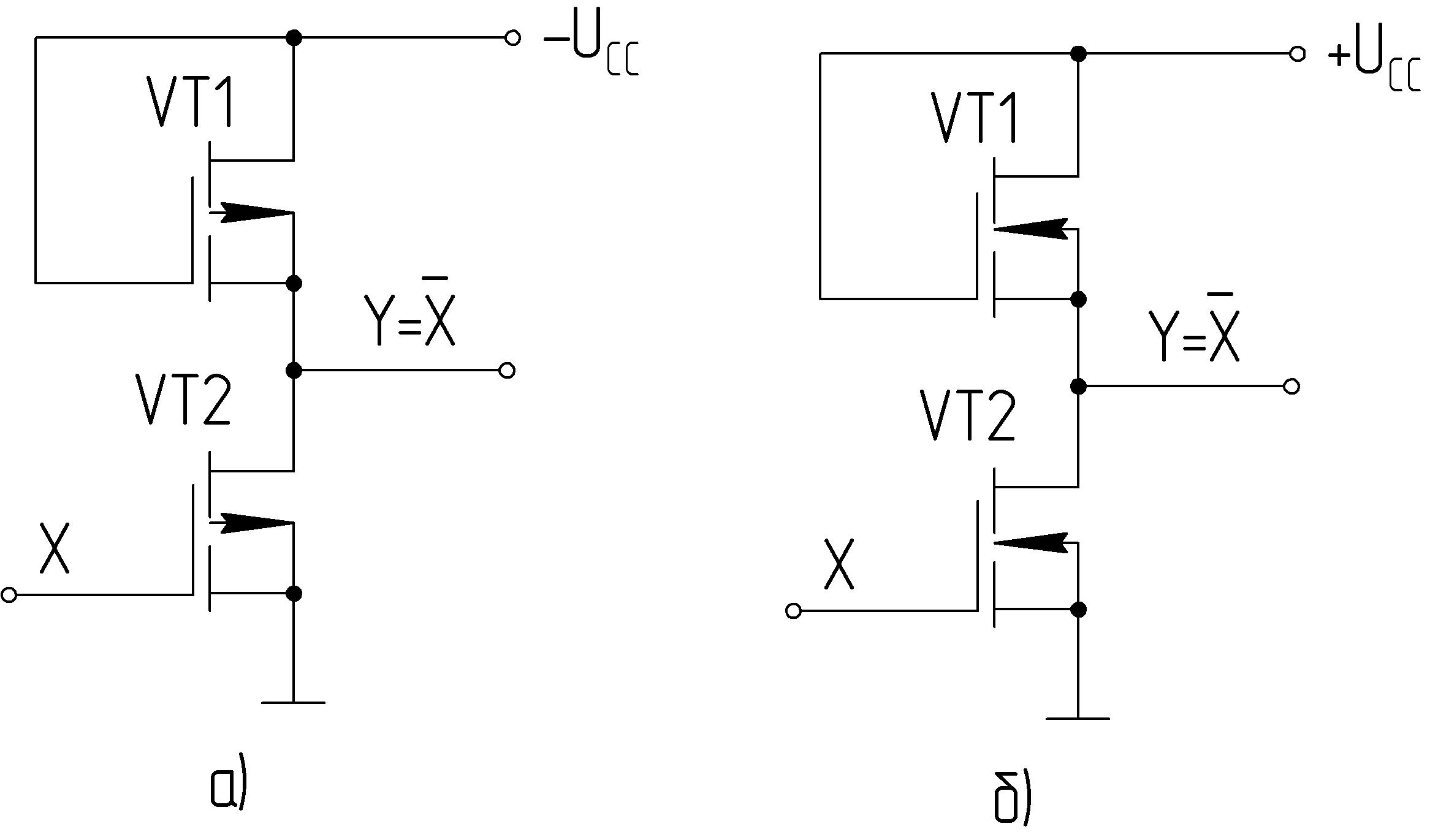

3.3.2.3 Логічні елементи на мон-транзисторах

Схеми

логічних елементів НІ на МОН-транзисторах

показані на рис.3.7.

У схемі елемента НІ на р-МОН-транзисторах

застосовують навантажувальний транзистор

VT1,

стік якого підключається до негативного

джерела живлення мінус

(рис. 3.7,а). Напруга негативної полярності

вхідної змінної

![]() надходить

на затвор вхідного транзистора VT2.

У

цій схемі застосовують транзистори з

індукованими каналами.

надходить

на затвор вхідного транзистора VT2.

У

цій схемі застосовують транзистори з

індукованими каналами.

У схемі елемента НЕ на n-МОН-транзисторах використовують навантажувальний транзистор VT1 з убудованим каналом, що підключається до позитивного джерела живлення плюс UCC . Позитивна напруга вхідний змінної X надходить на затвор вхідного транзистора VT2 з індукованим каналом (рис. 3.7, б). Навантажувальні транзистори включені за схемою двухполюсника.

Якщо

вхідна напруга

![]() то

транзистор VT2

закритий,

a VT1

—

відкритий

і на виході встановлюється рівень

напруги, близький до значення UCC

.

то

транзистор VT2

закритий,

a VT1

—

відкритий

і на виході встановлюється рівень

напруги, близький до значення UCC

.

Рисунок 3.7 - Схеми логічних елементів НІ на МОН-транзисторах.

Якщо

вхідне напруг

![]() ,

то обоє транзистора відкрита й вихідна

напруга

знімається з дільника, утвореного опором

каналів

,

то обоє транзистора відкрита й вихідна

напруга

знімається з дільника, утвореного опором

каналів

![]() ,

,

де

RB

і

RH

— опору каналів вхідного й навантажувального

транзисторів. Граничні

напруги для р-МОН

![]() ,

а для п

– МОН

,

а для п

– МОН

![]() .

.

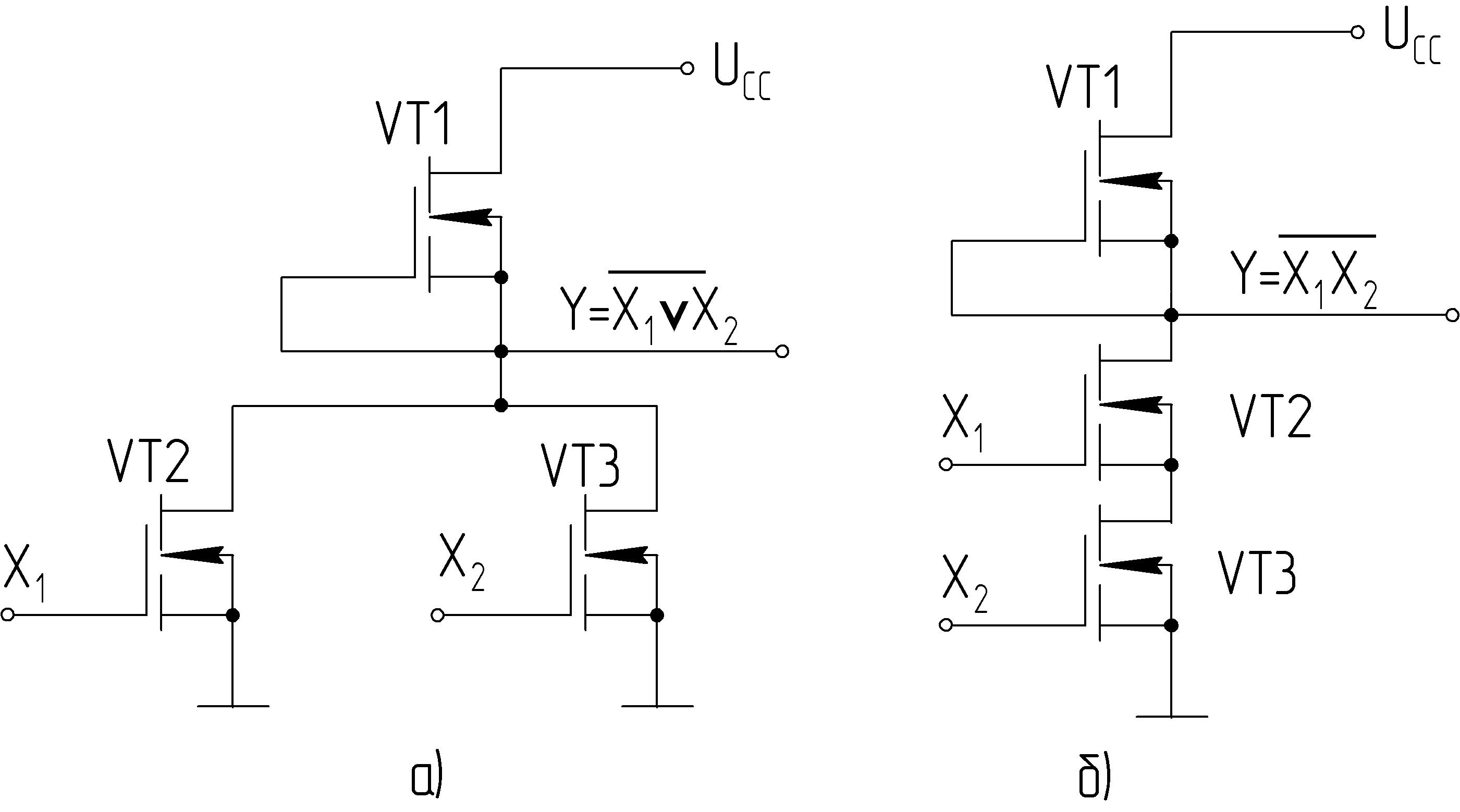

Схеми елементів HE-АБО й НЕ-І на п – МОН транзисторах показані на рис. 3.8. Елемент АБО-HІ утвориться паралельним з'єднанням вхідних транзисторів (рис. 3.8,а елемент НЕ-І послідовним з'єднанням (рис. 3.8, б).

Рисунок 3.8 - Схеми елементів АБО- HІ й І- НІ на п – МОН транзисторах.

Значення

балка. 0 відображається напругою

![]() ,

а балка. 1 — напругою

,

а балка. 1 — напругою

![]() На виході елемента АБО-

HІ встановлюється

інверсне значення логічної суми вхідних

змінних, а на виході елемента І-НІ

встановлюється інверсне

значення логічного добутку вхідних

змінних. Наприклад, на виході

елемента АБО-

HІ рівень

балка. 0 установлюється при наявності

хоча б на одному

вході одиничного сигналу. На виході

елемента І -НІ рівень балка. 0 установлюється

при збігу високих рівнів напруг на двох

входах, коли одночасно відкриваються

транзистори VT2

і

VT3.

На виході елемента АБО-

HІ встановлюється

інверсне значення логічної суми вхідних

змінних, а на виході елемента І-НІ

встановлюється інверсне

значення логічного добутку вхідних

змінних. Наприклад, на виході

елемента АБО-

HІ рівень

балка. 0 установлюється при наявності

хоча б на одному

вході одиничного сигналу. На виході

елемента І -НІ рівень балка. 0 установлюється

при збігу високих рівнів напруг на двох

входах, коли одночасно відкриваються

транзистори VT2

і

VT3.

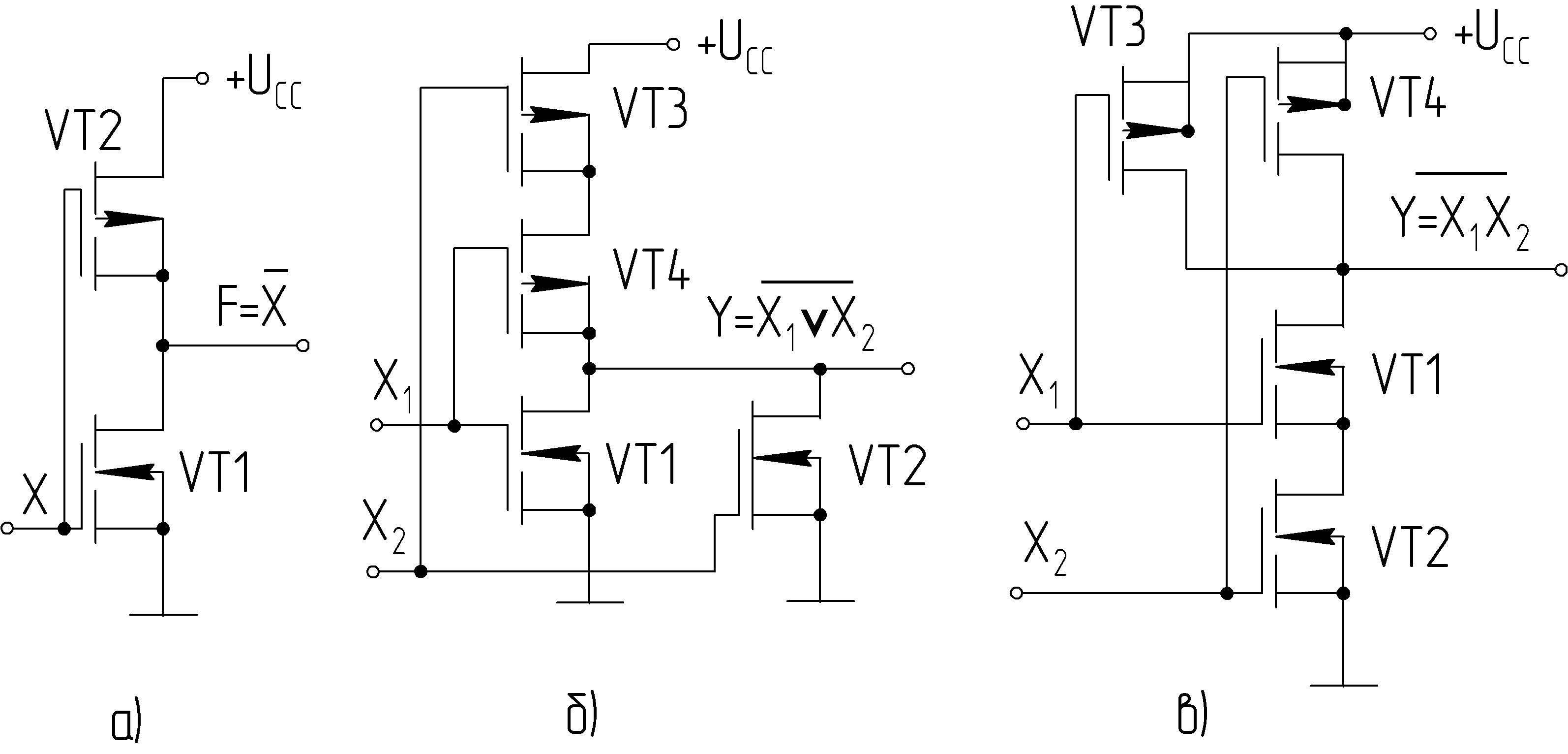

У

комплементарної МОН-структурі (логіка

КМОН) використовуються одночасно р-і

п-канальні транзистори. Елемент НІ в

схемотехніці КМОН побудований на двох

транзисторах з індукованими каналами:

навантажувальному VT2

із

каналом р-типу й

вхідному VT1

із

каналом n-типу (рис. 3.9,а). Виток транзистора

VT2

підключений

до витоку позитивного

живлення

![]() ,

напруга

вхідний змінної X

надходить

на затвори обох транзисторів; вихідна

напруга знімається з об'єднаних

стоків.

,

напруга

вхідний змінної X

надходить

на затвори обох транзисторів; вихідна

напруга знімається з об'єднаних

стоків.

Рисунок 3.9 - Схеми МОН-структур

При

вхідному рівні

![]() транзистор

VTI

відкритий,

a VT2

—

закритий, оскільки між

його затвором і витоком є нульова

напруга. На виході встановлюється

рівень

транзистор

VTI

відкритий,

a VT2

—

закритий, оскільки між

його затвором і витоком є нульова

напруга. На виході встановлюється

рівень

![]() і

струм у ланцюзі не протікає. При вхідному

рівні

і

струм у ланцюзі не протікає. При вхідному

рівні

![]() транзистор VT1

закритий,

a VT2

—

відкритий, тому що між його затвором і

витоком є напруга

транзистор VT1

закритий,

a VT2

—

відкритий, тому що між його затвором і

витоком є напруга

![]() .

На виході — рівень

.

На виході — рівень

![]() і

струм у ланцюзі не протікає.

і

струм у ланцюзі не протікає.

На

рисунку 3.9, б

показана

схема КМОН елемента АБО - НІ, у якому

вхідні транзистори

VT1

і

VT2

включені

паралельно, а навантажувальні — VT3

і

VT4

—

послідовно.

Якщо хоча б на одному із входів є рівень

напруги

,

то даний

транзистор відкривається, на виході

встановлюється рівень

![]() ,

навантажувальні

транзистори закриті, струм у ланцюзі

не протікає. Якщо на обох входах є рівень

напруги

то

транзистори VTI

і

VT2

закриті,

a VT3

і VT4

— відкриті,

на виході встановлюється напруга

й струм у ланцюзі не протікає.

,

навантажувальні

транзистори закриті, струм у ланцюзі

не протікає. Якщо на обох входах є рівень

напруги

то

транзистори VTI

і

VT2

закриті,

a VT3

і VT4

— відкриті,

на виході встановлюється напруга

й струм у ланцюзі не протікає.

На

рис. 3.9 показана схема КМОН-елемента

І-НІ, в якій вхідні транзистори

VT1

і

VT2

включені

послідовно, а навантажувальні VT3

і

VT4

— паралельно. Якщо на затвори вхідних

транзисторів одночасно надходять

сигнали

,

то транзистори VT1

і

VT2

відкриваються,

вихідний рівень дорівнює

![]() , навантажувальні

транзистори закриті, струм у ланцюзі

не протікає. Якщо хоча б на одному із

входів є

рівень напруги

,

то

транзистори VTI

і

VT2

закриті,

відкривається один

з навантажувальних транзисторів VT3

або

VT4.

На

виході встановлюється рівень

і

струм у ланцюзі не протікає.

, навантажувальні

транзистори закриті, струм у ланцюзі

не протікає. Якщо хоча б на одному із

входів є

рівень напруги

,

то

транзистори VTI

і

VT2

закриті,

відкривається один

з навантажувальних транзисторів VT3

або

VT4.

На

виході встановлюється рівень

і

струм у ланцюзі не протікає.

Таким чином, у схемах КМОН у статичному стані протікає дуже малий робочий струм, оскільки при відкритих вхідних транзисторах закриті навантажувальні й навпаки. Сумарна потужність споживання в основному визначається енергією, що витрачається на перезаряд паразитних ємностей.

Промисловість випускає наступні серії КМОН: 176, 564, 561, КР1561 і КР1554. Мікросхеми швидкодіючої серії КР1554 мають функціональну й технічну повноту й включають логічні елементи, тригери, регістри, лічильники, дешифратори, мультиплексори й ін.