- •6.1 Контрольные вопросы для зачёта по дисциплине:

- •Краткая история развития вт

- •Базовая структура машины Джона фон Неймана

- •Поколения эвм

- •Представление информации в эвм

- •2.2.2. Представление других видов информации

- •2.1. Системы счисления

- •2.1.1. Перевод целых чисел

- •2.1.2. Перевод дробных чисел

- •2.6. Прямой, обратный и дополнительный коды

- •2.6.1. Прямой код

- •2.6.2. Обратный код

- •2.6.3. Дополнительный код

- •2.6.8. Модифицированные коды

- •2.4.1.Основные сведения из алгебры логики

- •2.4.3. Понятие о минимизации логических функций

- •Диаграмма Вейча функции y

- •2.4.4. Техническая интерпретация логических функций

- •Диаграмма Вейча для функции f

- •Классификация элементов и узлов эвм

- •3.3. Схемы с памятью

- •Условия работы триггера

- •Диаграмма Вейча для таблицы переходов триггера

- •Общие принципы построения современных эвм

- •3.1. Операционные устройства (алу)

- •3.2. Управляющие устройства

- •3.2.1. Уу с жесткой логикой

- •3.2.2. Уу с хранимой в памяти логикой

- •3.2.2.1. Выборка и выполнение мк

- •3.2.2.3. Кодирование мк

- •3.2.2.4. Синхронизация мк

- •5.2.1. Структура базового микропроцессора

- •Характеристики микропроцессоров фирмы Intel

- •Структура микропроцессора

- •5.2.3. Взаимодействие элементов при работе микропроцессора

- •Структура памяти эвм

- •4.2. Способы организации памяти

- •4.2.1. Адресная память

- •4.2.2. Ассоциативная память

- •4.2.3. Стековая память (магазинная)

- •4.5. Постоянные зу (пзу, ппзу)

- •4.6. Флэш-память

- •5.1.2. Размещение информации в основной памяти ibm pc

- •Назначение, принцип работы и организация системы прерываний эвм

- •Возможные структуры систем прерывания

- •Характеристики систем прерывания

- •Принципы организации ввода / вывода информации в эвм

- •8.1. Общие принципы организации вв

- •8.2. Программный вв

- •8.3. Вв по прерываниям

- •8.4. Вв в режиме пдп

- •8.4.1. Пдп с захватом цикла

- •8.4.2. Пдп с блокировкой процессора

- •Интерфейсы периферийных устройств

- •Последовательный порт

- •Системы визуального отображения информации (видеосистемы)

- •.2. Клавиатура

- •7.3. Принтер

- •.4. Сканер

- •7.5. Анимационные устройства ввода-вывода

- •7.6. Устройства ввода-вывода звуковых сигналов

- •Глава 8. Внешние запоминающие устройства (взу)

- •8.1. Внешние запоминающие устройства на гибких магнитных дисках

- •Стандартные форматы нгмд ms dos

- •8.2. Накопитель на жестком магнитном диске

- •8.3. Стриммер

- •8.4. Оптические запоминающие устройства

- •Основные внешние устройства пк

- •Компоненты материнской платы

- •Разновидности слотов

- •Типы разъемов оперативной памяти

- •Разъемы для подключения внешних устройств

- •Разъемы для подключения дисковых устройств

- •Разъемы процессоров

- •Интерфейс

- •Шинная структура

- •Типы обмена по системной магистрали.

- •Магистраль процессора.

- •Формирование сигналов системной магистрали

- •Магистрально-модульный принцип построения компьютера

- •Принципы организации арбитража магистрали

- •Классификация мп

- •2 Типы микропроцессоров

- •3.7.3 Характеристики мп

- •Структура типового микропроцессора

- •Логическая структура микропроцессора

- •Типы архитектур

- •Микропроцессорные устройства.

- •1. Технология медной металлизации

- •2. Технология soi («кремний-на-изоляторе»)

- •3. Технология Low-k dielectric

- •4. SiGe: кремниево-германиевые микросхемы

- •5. Напряженный кремний

- •1.1. Общая структура микропроцессорной системы

- •Уровни представления микропроцессорной системы

- •1.2. Построение микропроцессорных систем с использованием различных микропроцессорных комплектов

- •1.3. Основные этапы разработки микропроцессорной системы

- •Лекция 13. Рабочие станции и серверы Классификация вычислительных систем. Персональные компьютеры и рабочие станции. X-терминалы. Cерверы. (6 ч.) Классификация вычислительных систем

- •Рабочая станция

- •Микроэвм

- •Классификация аппаратных средств вычислительных систем по ф.Г. Энслоу

- •1. С общей шиной.

- •2. С перекрестной коммутацией.

- •3 Мпвк с многовходовыми озу.

- •4. Ассоциативные вс.

- •5. Матричные системы.

- •6. Конвейерная обработка информации.

- •Признаки суперЭвм

- •Сферы применения суперкомпьютеров

- •Архитектура современных суперЭвм

- •Векторные суперкомпьютеры [simd]

- •Многопроцессорные векторные суперкомпьютеры (mimd)

- •Лекция 17. Проблемно-ориентированные эвм

- •Основы конфигурирования серверов баз данных

Принципы организации ввода / вывода информации в эвм

Вводом/выводом (ВВ) называют передачу данных между ядром ЭВМ, включающим в себя процессор и ОП, и периферийными устройствами (ПУ).

Система ВВ – это единственное средство общения ЭВМ с внешним миром. Ее возможности в серийных ЭВМ представляют собой один из важнейших параметров, определяющих выбор машины для конкретного применения.

Несмотря на разнообразие ПУ, в настоящее время разработано несколько стандартных способов их подключения к ЭВМ и программирования ВВ. Существует три режима ВВ:

Программный ВВ (нефорсированный).

ВВ по прерыванию (форсированный).

Прямой доступ к памяти (ПДП).

Реализация ВВ в каждом из этих режимов отличается программно-аппаратными затратами и, самое важное, скоростью выполнения операций обмена и непроизводительными затратами времени процессора. Суть каждого из трех режимов состоит в следующем.

Программный ВВ. Инициирование и управление ВВ осуществляет процессор по командам прикладной программы. ПУ играют пассивную роль и только сигнализируют о своем состоянии, в частности о готовности к операциям ВВ.

ВВ по прерыванию. Операции ВВ инициирует ПУ, генерируя сигнал запроса прерывания, при этом процессор переключается на подпрограмму обслуживания данного ПУ, вызвавшего прерывание. В результате выполнения подпрограммы (обработчика) осуществляется обмен данными. Действия, выполняемые обработчиком, определяются пользователем, а непосредственно операциями ВВ управляет процессор.

Таким образом, как при программном ВВ, так и при ВВ по прерываниям операциями обмена управляет процессор, поэтому очень часто эти два варианта обмена не разделяют и рассматривают их как программный ВВ. В англоязычной литературе – Programmed Input/Output (PIO). Однако в настоящем курсе эти варианты обмена рассматриваются отдельно.

Прямой доступ к памяти. Процессор в передаче данных не участвует. Он отключается от системной магистрали, а все операции обмена данными идут под управлением специального управляющего устройства – контроллера ПДП. Этот режим используется для быстродействующих ПУ, когда пропускной способности процессора недостаточно.

Следует отметить, что общие принципы организации систем прерывания уже рассмотрены в гл. 6. Организация систем ПДП подробно рассмотрена в гл. 11. Ниже рассматривается простейший случай организации радиальных систем прерывания и ПДП для микроЭВМ на базе МП КР580, поэтому материал настоящего раздела частично перекрывается с материалом, изложенным в гл. 6 и в гл. 11.

8.1. Общие принципы организации вв

В каждой ЭВМ применяются особые способы ВВ, различные конфигурации схем и типы устройств. Однако для большинства ЭВМ можно выделить следующие общие принципы:

Передача данных осуществляется по общей системной магистрали (что характерно для микроЭВМ) либо по специальной магистрали ВВ (что характерно для мини- и больших ЭВМ). Иногда отдельная быстродействующая магистраль ВВ выделяется только для обмена в режиме ПДП.

Подключение ПУ к системному интерфейсу осуществляется с помощью промежуточного интерфейса, поддерживаемого со стороны микроЭВМ и ПУ соответствующими адаптерами (см. п. 7.2).

Операции ВВ инициируются только в случае готовности ПУ к обмену. При наличии нескольких ПУ и обмене в режиме прерывания или ПДП вводится система приоритетов, позволяющая избежать конфликтов. В соответствии с этой системой контроллер прерываний или ПДП среди ПУ, готовых к обмену, в первую очередь обслуживает ПУ с высшим приоритетом (см. гл. 6 и гл. 11).

Передача данных осуществляется двумя способами:

отдельными битами, и тогда промежуточный интерфейс называется последовательным;

полными словами (например, целым байтом), и тогда промежуточный интерфейс называется параллельным.

Информация, передаваемая в процессе ВВ, подразделяется:

на собственно данные (обозначим D);

управляющие данные (обозначим U).

Управляющие данные от процессора называются также командными словами или приказами. Они инициируют действия, не связанные непосредственно с передачей данных (запуск устройства, запрещение прерываний, установка режимов и т.д.).

Управляющие данные от ПУ называются словами состояния. Они содержат информацию об определенных признаках (о готовности устройства к передаче данных, о наличии ошибок при обмене и т.д.). Состояние обычно представляется в декодированной форме – один бит для каждого признака.

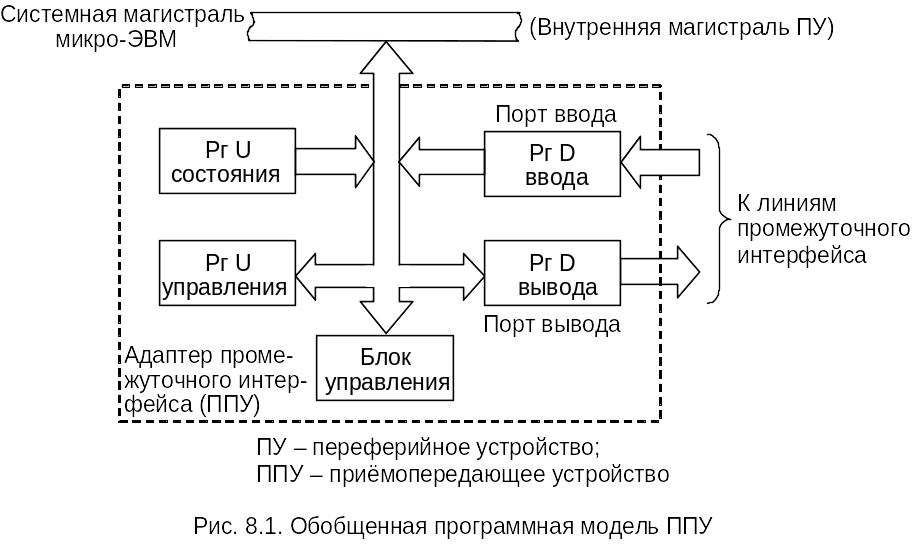

С учетом всего изложенного можно изобразить наиболее общую программную модель адаптера промежуточного интерфейса (ППУ), связывающего системную магистраль микроЭВМ и внутреннюю магистраль ПУ. Такая обобщенная программная модель ППУ представлена на рис. 8.1. Каждый из указанных регистров должен иметь адрес, который может идентифицироваться дешифратором адреса.

Естественно, что конкретная модель адаптера может отличаться от обобщенной схемы, например, регистр состояния и управления могут быть объединены в один регистр, вместо двух однонаправленных портов используют один двунаправленный, регистров управления может быть несколько. Однако при этом логические функции указанных четырех регистров остаются.

В соответствии с рассмотренными ранее различными структурами системной магистрали возможны два способа организации операций ВВ.

Изолированный ВВ (соответствует структуре с изолированными шинами)

Изолированный ВВ предполагает наличие специальных команд ВВ. В МП КР580 это команды IN и OUT. Адресное пространство регистров ППУ изолировано от адресного пространства ячеек памяти, т.е. регистры ППУ и ячейки памяти могут иметь одинаковый адрес. Команды IN и OUT – двухбайтовые. Первый байт – КОП, а второй несет информацию о номере адресуемого ППУ и номере адресуемого в нем регистра. При этом в МП КР580 предусмотрена возможность обмена данными по командам IN, OUT только между аккумулятором и адресуемыми регистрами.

ВВ по общей шине (соответствует структуре с общими шинами)

В этом случае адресация к регистрам ППУ осуществляется как к обычным ячейкам памяти, т.е. ячейки памяти и регистры ППУ имеют единое адресное пространство. Можно использовать все команды обращения к ячейкам памяти. Это удобно, однако часть адресного пространства памяти используется для адресации регистров ППУ, что может вызвать трудности, если программа большая и много ПУ.

ПУ и микроЭВМ могут обмениваться достаточно большими объемами информации, которые невозможно поместить только в регистрах процессора. Ввиду этого часто операции ВВ являются операциями обмена данными между ОП и ПУ. Как уже отмечалось, для повышения гибкости всей вычислительной системы в микроЭВМ предусмотрено три режима выполнения операций ВВ. Рассмотрим эти режимы подробнее.