- •6.1 Контрольные вопросы для зачёта по дисциплине:

- •Краткая история развития вт

- •Базовая структура машины Джона фон Неймана

- •Поколения эвм

- •Представление информации в эвм

- •2.2.2. Представление других видов информации

- •2.1. Системы счисления

- •2.1.1. Перевод целых чисел

- •2.1.2. Перевод дробных чисел

- •2.6. Прямой, обратный и дополнительный коды

- •2.6.1. Прямой код

- •2.6.2. Обратный код

- •2.6.3. Дополнительный код

- •2.6.8. Модифицированные коды

- •2.4.1.Основные сведения из алгебры логики

- •2.4.3. Понятие о минимизации логических функций

- •Диаграмма Вейча функции y

- •2.4.4. Техническая интерпретация логических функций

- •Диаграмма Вейча для функции f

- •Классификация элементов и узлов эвм

- •3.3. Схемы с памятью

- •Условия работы триггера

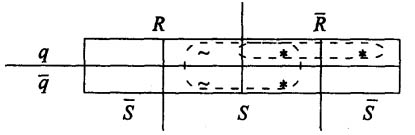

- •Диаграмма Вейча для таблицы переходов триггера

- •Общие принципы построения современных эвм

- •3.1. Операционные устройства (алу)

- •3.2. Управляющие устройства

- •3.2.1. Уу с жесткой логикой

- •3.2.2. Уу с хранимой в памяти логикой

- •3.2.2.1. Выборка и выполнение мк

- •3.2.2.3. Кодирование мк

- •3.2.2.4. Синхронизация мк

- •5.2.1. Структура базового микропроцессора

- •Характеристики микропроцессоров фирмы Intel

- •Структура микропроцессора

- •5.2.3. Взаимодействие элементов при работе микропроцессора

- •Структура памяти эвм

- •4.2. Способы организации памяти

- •4.2.1. Адресная память

- •4.2.2. Ассоциативная память

- •4.2.3. Стековая память (магазинная)

- •4.5. Постоянные зу (пзу, ппзу)

- •4.6. Флэш-память

- •5.1.2. Размещение информации в основной памяти ibm pc

- •Назначение, принцип работы и организация системы прерываний эвм

- •Возможные структуры систем прерывания

- •Характеристики систем прерывания

- •Принципы организации ввода / вывода информации в эвм

- •8.1. Общие принципы организации вв

- •8.2. Программный вв

- •8.3. Вв по прерываниям

- •8.4. Вв в режиме пдп

- •8.4.1. Пдп с захватом цикла

- •8.4.2. Пдп с блокировкой процессора

- •Интерфейсы периферийных устройств

- •Последовательный порт

- •Системы визуального отображения информации (видеосистемы)

- •.2. Клавиатура

- •7.3. Принтер

- •.4. Сканер

- •7.5. Анимационные устройства ввода-вывода

- •7.6. Устройства ввода-вывода звуковых сигналов

- •Глава 8. Внешние запоминающие устройства (взу)

- •8.1. Внешние запоминающие устройства на гибких магнитных дисках

- •Стандартные форматы нгмд ms dos

- •8.2. Накопитель на жестком магнитном диске

- •8.3. Стриммер

- •8.4. Оптические запоминающие устройства

- •Основные внешние устройства пк

- •Компоненты материнской платы

- •Разновидности слотов

- •Типы разъемов оперативной памяти

- •Разъемы для подключения внешних устройств

- •Разъемы для подключения дисковых устройств

- •Разъемы процессоров

- •Интерфейс

- •Шинная структура

- •Типы обмена по системной магистрали.

- •Магистраль процессора.

- •Формирование сигналов системной магистрали

- •Магистрально-модульный принцип построения компьютера

- •Принципы организации арбитража магистрали

- •Классификация мп

- •2 Типы микропроцессоров

- •3.7.3 Характеристики мп

- •Структура типового микропроцессора

- •Логическая структура микропроцессора

- •Типы архитектур

- •Микропроцессорные устройства.

- •1. Технология медной металлизации

- •2. Технология soi («кремний-на-изоляторе»)

- •3. Технология Low-k dielectric

- •4. SiGe: кремниево-германиевые микросхемы

- •5. Напряженный кремний

- •1.1. Общая структура микропроцессорной системы

- •Уровни представления микропроцессорной системы

- •1.2. Построение микропроцессорных систем с использованием различных микропроцессорных комплектов

- •1.3. Основные этапы разработки микропроцессорной системы

- •Лекция 13. Рабочие станции и серверы Классификация вычислительных систем. Персональные компьютеры и рабочие станции. X-терминалы. Cерверы. (6 ч.) Классификация вычислительных систем

- •Рабочая станция

- •Микроэвм

- •Классификация аппаратных средств вычислительных систем по ф.Г. Энслоу

- •1. С общей шиной.

- •2. С перекрестной коммутацией.

- •3 Мпвк с многовходовыми озу.

- •4. Ассоциативные вс.

- •5. Матричные системы.

- •6. Конвейерная обработка информации.

- •Признаки суперЭвм

- •Сферы применения суперкомпьютеров

- •Архитектура современных суперЭвм

- •Векторные суперкомпьютеры [simd]

- •Многопроцессорные векторные суперкомпьютеры (mimd)

- •Лекция 17. Проблемно-ориентированные эвм

- •Основы конфигурирования серверов баз данных

3.3. Схемы с памятью

Более сложным преобразователем информации являются схемы с памятью. Наличие памяти в схеме позволяет запоминать промежуточные состояния обработки и учитывать их значения в дальнейших преобразованиях. Выходные сигналы Y = (y1, y2, ..., уm) в схемах данного типа формируются не только по совокупности входных сигналов Х = (х1, х2, ..., хn), но и по совокупности состояний схем памяти Q = (q1, q2, ..., qk). При этом различают текущий дискретный момент времени t и последующий (t+1) момент времени (рис. 3.8).

Рис. 3.8. Обобщенная структура схемы с памятью

Передача значения Q между моментами времени t и (t+1) осуществляется обычно с применением двухступенчатой памяти и синхронизирующих импульсов (СИ).

В качестве простейшего запоминающего элемента (ЗЭ) в современных ЭВМ используют триггеры. В связи с успешным применением микроэлектроники в схемах основных устройств ЭВМ (процессоров и оперативной памяти) исчезли в качестве запоминающихся элементов схемы, использующие остаточную намагниченность - ферритовые сердечники. Самая простейшая схема триггера может быть синтезирована по общим правилам (п.2.4.4).

Пример3.1. Построить автомат намят - триггер, имеющий вход R (Reset - сброс), Для установки элемента в "нулевое состояние" и вход S (Sеt - установка) - для установки элемента в "единичное" состояние. При отсутствии сигналов R=S=0 элемент должен сохранять свое состояние до тех пор, пока не будут получены новые сигналы на входе К или 8.

Условия работы триггера могут быть представлены в виде таблицы переходов (табл. 3.5), представляющей собой модификацию таблицы истинности.

Таблица 3.5

Условия работы триггера

Входы |

Состояние qt+1 |

|||

R |

S |

0 |

1 |

Режим |

0 |

0 |

0 |

1 |

Хранение |

1 |

0 |

0 |

0 |

Установка 0 |

0 |

1 |

1 |

1 |

Установка 1 |

l |

l |

? |

? |

Запрещенное состояние |

Содержание таблицы расшифровывается следующим образом. Элемент памяти может сохранять значение qt=0 или qt=1 в зависимости от установки ранее установленного состояния. При отсутствии входных сигналов на входах R и S (R =0 и S =0) значения qt+1 первой строке таблицы в точности повторяют значения qt. При поступлении сигнала R=l (сигнала установки "нуля") элемент независимо от своего состояния принимает значение, равное нулю, qt+1=0. Если же на вход S поступает сигнал установки "единицы" (S=1), то qt+1=1 независимо от предыдущего состояния qt. Одновременное поступление сигналов на входы R и S является запрещенной ситуацией, так как она может привести к непредсказуемому состоянию. В схемах формирования сигналов R и S должны быть предусмотрены блокировки, исключающие их совпадения, S=R=1.

Для таблицы переходов (табл.3.5) может быть построена диаграмма Вейча (табл.3.6).

Таблица 3.6

Диаграмма Вейча для таблицы переходов триггера

В этой таблице знаком "~"отмечены запрещенные комбинации входных сигналов. Эти комбинации могут быть использованы для упрощения логических зависимостей. Логическая зависимость, описывающая работу элемента памяти, принимает вид:

![]() (3.4)

(3.4)

Уравнение (3.4) получено путем эквивалентных преобразований. Добавление в него комбинаций, соответствующих запрещенным ситуациям и помеченных знаком "~", т.е.

![]()

позволяет еще больше упростить уравнение триггера:

![]() (3.5)

(3.5)

Для реализации полученной зависимости в базисе И - НЕ применим правило де Моргана и получим функцию

![]()

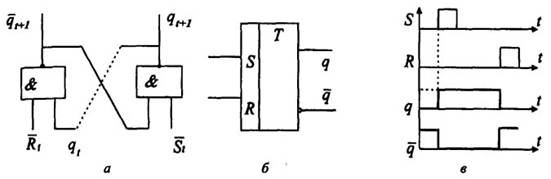

По данной зависимости можно построить схему элемента памяти - асинхронного RS-тригера. В этой схеме следует только соединить выход qt+1со входом qt. На рис.3.9 эта связь отмечена штриховой линией.

Рис. 3.9. Схема асинхронного RS-триггера: а- схема; б - обозначение на принципиальных электрических схемах; в - временная диаграмма

RS-триггер нашел широкое распространение в схемах ЭВМ. Одиночные триггеры этого типа часто используются в различных блоках управления. В асинхронных RS-триггерах имеется один существенный недостаток, обусловленный самой логикой их построения (см. табл. 3.5), т.е. в них сигналы R и S должны быть разнесены во времени. Дополнение этого триггера комбинационными схемами синхронизации на входе и выходе позволяет получить триггеры с более сложной логикой работы: синхронные RS-триггеры, Т-, JK-, D- триггеры и целый ряд комбинированных RST-, JKRS-, DRS-трштеров [ 4].

Прописные буквы в названиях триггеров обозначают:

∙ R (Reset - сброс) - вход установки триггера в нулевое состояние Q=0;

∙ S (Set - установка) - вход установки триггера в единичное состояние 0=1;

∙ Т (Toggle - релаксатор) - счетный вход триггера;

∙ J (Jerk - внезапное включение) - вход установки ЛС-триггера в единичное состояние Q=1;

∙ К (Kill - внезапное выключение) - Q=0;

∙ D (Delay - задержка) - вход установки триггера в единичное или нулевое состояние на время, равное одному такту;

∙ С (Clock - часы) - вход синхронизирующих тактовых импульсов. На рис. 3.10 показаны схемы синхронного однотактного (а) и двухтактного (б) RS-триггеров.

Двухкаскадная схема RS-триггера (рис.3.10, б) нашла наиболее широкое применение для построения n-разрядных схем запоминания - всевозможных регистровых схем. Штриховыми линиями на схеме указаны дополнительные точки подключения сигналов установки и сброса.

Рис. 3.10. Электрическая и функциональная схемы синхронных RS-тригтеров: а, б - варианты

На рис. 3.11 приведена схема Т-триггера или иначе - триггера со счетным входом. При значении 7=0 триггер сохраняет свое ранее установленное состояние - режим хранения состояния, при T=1 триггер переходит в противоположное состояние. Таблица переходов (табл. 3.7) и диаграмма работы (рис. 3.11, б) отражают динамику работы этого элемента.

Рис. 3.11. Схема триггера со счетным входом: а- функциональная; б - условное обозначение; в - временная диаграмма

Таблица 3.7

Таблица переходов Т-триггера

Входные сигналы |

Состояние qt |

Режим |

|

Xt |

0 |

1 |

|

0 l |

0 1 |

1 0 |

Хранение Инверсия |

По таблице переходов можно получить логическую функцию, реализуемую Т-триггером:

![]() (3.7)

(3.7)

Нетрудно видеть, что зависимость (3.7) очень похожа на функцию (3.2), выведенную для одноразрядного комбинационного полусумматора. На рис. 3.11, а показано, как двухтактный RS-триггер преобразуется в Т-триггер.

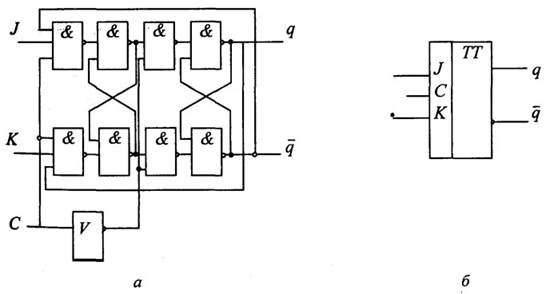

Наиболее сложным типом триггера является JK-тригтер. Он, по существу, является объединением двухтактного RS- и Т-триггеров. Этому соответствует его таблица переходов (табл.3.8).

Таблица 3.8

Таблица переходов JK-триггера

Входные сигналы |

Состояние q |

Режим |

||

J |

K |

0 |

1 |

|

0 0 0 l |

l 0 l l |

0 l 0 0 |

1 0 l 0 |

Хранение Установка 0 Установка l Инверсия |

Если первые три строки таблицы переходов полностью повторяют соответствующие строки табл. 3.5, то последняя строка, с запрещенной комбинацией для RS-триггера, соответствует режиму переключения Т-триггера (см. табл.3.7). Схема JK-триггера изображена на рис. 3.12.

Рис. 3.12. JK-триггер: а - функциональная схема; б - условное обозначение

D-триггер обычно строится на основе двухтактного RS- или JK-тригера. Он предназначается для хранения состояния (1 или 0) на один период тактовых импульсов (с задержкой на 1 такт). Таблица его переходов отражена в табл. 3.9. На рис.3.13, а и б представлены варианты его построения, а на рис.3.13, в - его условное обозначение.

Таблица 3.9

Таблица переходов D-триггера

Входные сигналы |

Состояния q |

Режим |

|

D |

0 |

l |

|

0 l |

0 1 |

0 1 |

Установка 0 Установка l |

Рис. 3.13. D-триггер: a- функциональная схема на основе RS-триггера; б- функциональная схема на основе JK-трштера; в - условное обозначение

Все перечисленные элементы памяти позволяют хранить одну единицу информации - бит или одну двоичную цифру.

При построении ЭВМ широко используются функциональные схемы, обеспечивающие операции хранения и преобразования информации над группами битов (машинными словами). Такие сложные схемы называются узлами. К типовым узлам относят: регистры, счетчики, сумматоры. Все они также принадлежат к регулярным структурам, состоящим из одинаковых параллельно работающих одноразрядных схем.

Регистром называется узел, предназначенный для приема, временного хранения и выдачи машинного слова. Регистры могут также использоваться для некоторых операций преобразования данных: для сдвига кода числа (слова) на определенное число разрядов влево или вправо, для преобразования последовательного кода числа в параллельный и наоборот и т.д. Эти дополнительные функции регистров обеспечиваются путем усложнения схем хранения, выбора более сложных триггеров и подключения дополнительных логических схем на их входах и выходах.

Таким образом, регистры представляют собой совокупность триггеров, число которых соответствует числу разрядов в слове, и вспомогательных схем, обеспечивающих выполнение различных операций над словом.

На рис.3.14 показана функциональная схема n-разрядного регистра, построенного на RS-триггерах. Информация в регистр записывается под действием сигнала "Запись". Предварительно перед установкой кода на регистр обычно на все разряды R подается сигнал сброса. На рисунке показано, что подключение к входам R дополнительных инверторов позволяет избежать этой предварительной операции. Здесь на вход каждого разряда поступает парафазный код двоичной цифры (xi - на вход Si и хi - на вход Ri), т.е. прямое и инверсное значения кода подаются в противофазе.

На рис.3.15 изображена функциональная схема того же регистра, дополненная логическими элементами для преобразования хранящегося на регистре кода. По сигналу "Прямой код" с регистра считывается прямой код хранящихся данных, а по сигналу "Обратный код" - инверсное значение каждого разряда слова. Если оба эти сигнала поступают одновременно, то считывается парафазный код хранящейся информации. Более сложная логика на входе и выходе запоминающих элементов позволяет строить сдвигающие регистры.

Рис. 3.14. Схема регистра на RS-триггерах: а - функциональная схема; б - условное обозначение регистра

Рис. 3.15. Схема выдачи информации из регистра

Счетчик - узел ЭВМ, позволяющий осуществлять подсчет поступающих на его вход сигналов и фиксацию результата в виде многоразрядного двоичного числа. Счетчик, состоящий из n-триггеров, дает возможность подсчитывать до N сигналов, связанных зависимостью:

n = log2 NилиN = 2".

В ЭВМ счетчики используются для подсчета импульсов, сдвигов, формирования адресов и т.д. Функционально различают суммирующие, вычитающие, реверсивные счетчики. Они также отличаются друг от друга логикой работы дополнительных логических элементов, подключаемых к триггерам.

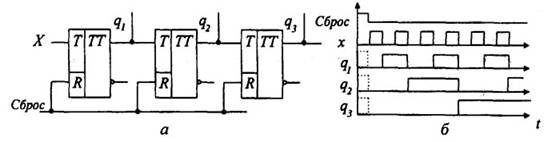

В основу построения любого счетчика положено свойство Т-триггеров изменять свое состояние при подаче очередного сигнала на счетный вход Т. На рис.3.16 показана схема трех разрядов суммирующего счетчика, построенного на Т-триггерах. Логика его работы представлена в табл. 3.10.

Таблица 3.10

Таблица переходов трехразрядного счетчика

Вход х |

Состояние |

||||||||

000 |

001 |

010 |

011 |

100 |

101 |

110 |

111 |

Режим |

|

0 1 |

000 001 |

001 010 |

010 011 |

011 100 |

100 101 |

101 110 |

110 111 |

111 000 |

Хранение Счет |

Рис. 3.16. Организация счетчика на Т-триггерах: а - функциональная схема; б - временная диаграмма

Сумматор - узел ЭВМ, в котором суммируются коды чисел. Как правило, любой сумматор представляет собой комбинацию одноразрядных сумматоров. Сумматоры различают по принципам построения: накапливающего типа и комбинационного типа. Сумматоры накапливающего типа строят на сложных JKRS-триггерах, дополняя их выходы достаточно сложными схемами формирования и распространения переносов. Процесс сложения при этом осуществляется поэтапно. Сначала на триггерах сумматора фиксируется код первого операнда, затем на счетные коды разрядов подается код второго операнда. По зависимостям (3.3) на каждом триггере формируются одноразрядные суммы и значения переносов между разрядами. Учет возникающих переносов задерживает формирование окончательного результата суммы и может требовать дополнительных тактов сложения. Из-за этого многоразрядные схемы сумматора накапливающего типа используются достаточно редко.

Более часто для построения сумматоров используются сумматоры комбинационного типа. Логика работы такого сумматора была представлена данными табл. 2.2. Обычно у такого сумматора на входе и выходе имеются регистры для хранения и преобразования кодов операндов и результата (рис.3.17).

Рис. 3.17. Упрощенная схема сумматора ЭВМ

Регистр Рг1 предназначается для хранения кода первого операнда, регистр Рг2 - для хранения кода второго операнда. Сумматор по сигналам из устройства управления настраивается на выполнение определенной машинной операции, соответствующей коду операции, находящемуся в коде команды. Результат выполняемой операции фиксируется в регистре РгЗ . При необходимости этот результат может использоваться для продолжения вычислений. Для этого предусматривается возможность перезаписи содержимого регистра РгЗ на Рг1 в качестве значения одного из операндов при выполнении очередной операции.

Лекция 3. Структура ЭВМ и назначение ее элементов.

Элементы архитектуры вычислительных систем. Принцип хранимой в памяти программы. Общие принципы построения современных ЭВМ. Архитектура системы команд.

Элементы архитектуры вычислительных систем.

Упрощенная структура ЭВМ представлена на рис. 1.1 ЭВМ содержит следующие основные устройства: арифметико-логическое устройство, память, управляющее устройство, устройство ввода данных в машину, устройство вывода из нее результатов расчета и пульт ручного управления.

Арифметико-логическое устройство (АЛУ) производит арифметические и логические преобразования над поступающими в него машинными словами, т. е. кодами определенной длины, представляющими собой числа или другой вид информации.

Память хранит информацию, передаваемую из других устройств, в том числе поступающую в машину извне через устройство ввода, и выдает во все другие устройства информацию, необходимую для протекания вычислительного процесса. Память машины в большинстве случаев состоит из двух существенно отличающихся по своим характеристикам частей: быстродействующей основной или оперативной (внутренней) памяти (ОП) и сравнительно медленно действующей, но способной хранить значительно больший объем информации внешней памяти (ВнП).

Оперативная память содержит некоторое число ячеек, каждая из которых служит для хранения машинного слова или его части. Ячейки нумеруются, номер ячейки называется адресом.

В запоминающих устройствах, реализующих в ЭВМ функцию памяти, выполняются операции считывания хранимой информации для передачи в другие устройства и записи информации, поступающей из других устройств. При считывании слова из ячейки содержимое последней не меняется и при необходимости слово может быть снова взято из той же ячейки. При записи хранившееся в ячейке слово стирается и его место занимает новое.

Непосредственно в вычислительном процессе участвует только ОП, и лишь после окончания отдельных этапов вычислений из ВнП в ОП передается информация, необходимая для следующего этапа решения задачи.

Рис. 1.1 Структура ЭВМ

Управляющее устройство (УУ) автоматически без участия человека управляет вычислительным процессом, посылая всем другим устройствам сигналы, предписывающие им те или иные действия, в частности включает АЛУ на выполнение нужной операции.

Автоматическое управление процессом решения задачи достигается на основе принципа программного управления, являющегося основной особенностью ЭВМ.

Другим важнейшим принципом является принцип хранимой в памяти программы. Согласно этому принципу команды программы, закодированные в цифровом виде, хранятся в памяти наравне с числами. В команде указываются не сами участвующие в операциях числа, а адреса ячеек ОП, в которых они находятся, и адрес ячейки, куда помещается результат операции.

Поскольку программа хранится в памяти, одни и те же команды могут нужное число раз извлекаться из памяти и выполняться. Более того, так как команды представляются в машине в форме чисел, то над командами как над числами машина может производить операции (“модификации команд”).

Команды выполняются в порядке, соответствующем их расположению в последовательных ячейках памяти, кроме команд безусловного и условного переходов, изменяющих этот порядок соответственно безусловно или только при выполнении некоторого условия, обычно задаваемого в виде равенства нулю, положительного или отрицательного результата предыдущей команды или отношения типа >, =, < для указываемых командой чисел. Именно благодаря наличию команд условного перехода ЭВМ может автоматически изменять соответствующим образом ход вычислительного процесса, решать сложные логические задачи.

Перед решением задачи на ЭВМ программа и исходные данные должны быть помещены в ее память. Предварительно эта информация обычно заносится во внешнюю память. Затем при помощи устройства ввода программа и исходные данные считываются в ОП.

Устройство вывода служит для выдачи из машины результатов расчета, например, путем печатания их на печатных устройствах или отображения на экране дисплея. При помощи пульта управления оператор пускает и останавливает машину, а при необходимости может вмешиваться в процесс решения задачи.

Представленная на рис. 1.1 структура (модель) вычислительной машины, получившая название фоннеймановской, благодаря ее изящной простоте и большой гибкости при управлении вычислительным процессом с самых первых шагов электронной вычислительной техники и по сей день доминирует при построении различных ЭВМ.

Однако в последние годы конструкторы ЭВМ, стремясь достигнуть существенного повышения их производительности, в ряде случаев отходят от модели фон Неймана.

Приведем один из примеров. В фоннеймановской машине с общей памятью для данных и команд имеется всего одна шина (магистраль) для передачи из памяти в другие устройства команд и данных, что ведет к снижению скорости работы ЭВМ.

Возможно построение машины с отдельными памятями и шинами для хранения и передачи команд и данных, допускающей параллельное во времени извлечение их из памяти и передачу по шинам. Такая структура (модель) получила название гарвардской, так как была реализована впервые в 1944 г. в Гарвардском университете (США) в ранней релейной вычислительной машине, предшествовавшей появлению электронных вычислительных машин. Гарвардская модель реализована, в частности, в некоторых микропроцессорах.

Понятие о системе программного обеспечения ЭВМ. Понятие об архитектуре ЭВМ.

Для придания ЭВМ определенных свойств используют средства двух видов: аппаратурные и программные. Последние называются также средствами программного (математического) обеспечения.

Часть свойств ЭВМ приобретает благодаря наличию в ее составе электронного или электромеханического оборудования, специально предназначенного для реализации этих свойств. Арифметико - логическое устройство машины является примером аппаратурных средств.

Ряд других свойств реализуется без специальных аппаратурных средств программным путем, при, этом используются имеющиеся аппаратурные средства машины, работающие в предписанном порядке в соответствии с программой, обеспечивающей выполнение машиной данной функции.

Заметим, что при помощи аппаратурных средств соответствующие функции выполняются значительно быстрее, чем программным путем.

Таким образом, средства программного обеспечения и аппаратурные средства являются двумя взаимосвязанными компонентами современной вычислительной техники.

Система программного (математического) обеспечения ЭВМ представляет собой комплекс программных средств, в котором можно выделить операционную систему, комплект программ технического обслуживания и пакеты прикладных программ. Первые два класса ПО принято также называть системным программным обеспечением.

Машинная зависимость является одной из характеристик, которая обычно отличает системное ПО от прикладного. Прикладная программа интересует нас главным образом с точки зрения решения некоторой задачи. При этом ЭВМ используется как инструмент, и основное внимание сосредоточено на предметной стороне дела, а не на вычислительной системе. С другой стороны, системные программы предназначены скорее для обеспечения управления собственно ЭВМ, чем для решения какой-то конкретной задачи. Вследствие этого они обычно тесно связаны со структурой машины, для которой созданы.

Операционные системы являются важнейшей и центральной частью программного обеспечения ЭВМ, предназначенной для эффективного управления вычислительным процессом, планирования работы и распределения ресурсов ЭВМ, автоматизации процесса подготовки программ и организации их выполнения при различных режимах работы машины, облегчения общения оператора с машиной.

Пользователи и операторы не имеют прямого доступа к устройствам ЭВМ. Связь пользователей и операторов с ЭВМ (точнее, с ее аппаратурными средствами) производится при помощи операционной системы, обеспечивающей определенный уровень общения человека с машиной.

Уровень общения в первую очередь определяется уровнем языка, на котором оно происходит, или, иными словами, уровнем пользовательского интерфейса системы.

Комплект программ технического обслуживания, предназначенный для уменьшения трудоемкости эксплуатации ЭВМ, содержит программы проверки работоспособности ЭВМ и отдельных ее устройств, определения (диагностирования) мест неисправностей.

Пакеты прикладных программ (ППП) представляют собой структурированные комплексы программ (часто со специализированными языковыми средствами), предназначенные для решения определенных достаточно широких классов задач (научно-технических, планово-экономических и др.), а также для расширения функций операционных систем (управление базами данных, реализация режимов телеобработки данных, реального времени и др.).

Аппаратурные средства ЭВМ и система ее программного обеспечения в совокупности образуют вычислительную систему.

Сложность современных вычислительных машин закономерно привела к понятию архитектуры вычислительной машины, охватывающей комплекс общих вопросов ее построения, существенных в первую очередь для прикладного или системного программиста, интересующегося главным образом возможностями машины, а не деталями ее технического исполнения.

Круг вопросов, подлежащих решению при разработке архитектуры ЭВМ, можно условно разделить на вопросы общей структуры, организации вычислительного процесса и общения пользователя с машиной, вопросы логической организации представления, хранения и преобразования информации и вопросы логической организации совместной работы различных устройств, а также аппаратурных и программных средств машины.