- •1. Сравнительный анализ схемотехнических базисов эвм. Взаимосвязь логического, схемотехнического и конструкторского этапов проектирования.

- •3. Синтезировать принципиальную схему ттлш без резисторов, разработать структуру (математическую модель-дерево); сделать 3-х мерный вариант; описать работу полученного элемента.

- •4. Схемотехника моп-вентилей. Принципы синтеза.

- •5. Синтезировать модификации схем ттл с простым и сложным инверторами с низкоомным путем для рассасывания заряда q2.

- •- Нагрузочная способность

- •6. Сравнительный анализ схем инверторов на моп-транзисторах.

- •7. Определить минимальное значение напряжения питания для схемы ттл со сложным инвертором. 56 стр в лекциях?

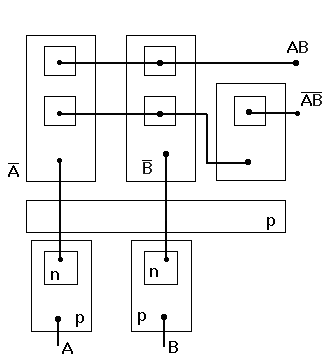

- •8. Логический элемент и-не на моп-транзисторах. Принципиальная схема, работа, математическая модель, варианты топологий и структур.

- •9. Определить напряжение логической «1»схемы ттл с простым инвертором с открытым коллектором.

- •10. Логический элемент или-не на моп-транзисторах. Принципиальная схема, работа, математическая модель, варианты топологий и структур.

- •11. Рассчитать напряжение логической «1»схемы ттлш с простым инвертором.

- •12. Нарисовать модель фиэ размерностью 6 с одним циклом и реализовать ее в трех технологиях (эпитаксиально-планарной, с локальной эпитаксией, 3-d).

- •13. Схемотехника транзисторно-транзисторных элементов (ттл).

- •14. Существует ли кмоп логический вентиль с нечетным количеством транзисторов? Если существует, приведите пример. Опишите его работу.

- •15. Реализация функции и-или-не в ттл-схемотехнике.

- •16. Разработать математическую модель (граф) мэсл с минимальным количеством полупроводниковых областей (вершин графа).

- •17. (36) Схема ттл с тремя состояниями. Работа. Варианты использования.

- •18. Чем определяется напряжение питания в этих схемах, и зависит ли оно от входного вентиля (моп-вентили или-не и и-не)?

- •24. Синтезировать в различных схемотехнических базисах схемы или, математические модели которых содержат минимальное количество полупроводниковых областей.

- •26. Сравнить математические модели n-моп и кмоп инверторов. Синтезировать их трехмерные структуры.

- •25. Методика проектирования устройств эвм в базисе эсл. Привести примеры.

- •27. Методика проектирования устройств эвм в базисе и2л. Привести примеры.

- •28. Определить минимально возможное значение напряжение питания биполярного инвертора.

- •Статическая мощность логических элементов.

- •29. Методика проектирования устройств эвм в моп и кмоп схемотехниках. Привести примеры.

- •30. Синтезировать элемент с тремя состояниями в любой схемотехнике кроме ттл.

- •31. Схемотехника элементов эмиттерно-связанной логики (эсл).

- •Мэсл (маломощная эсл)

- •Увеличение быстродействия за счет уменьшения входного сопротивления

- •Реализацию дополнительной логической функции монтажное или (параллельное соединение эмиттерных повторителей)

- •32. Чем определяется напряжение питания моп-вентилей и-не? Как это влияет на другие технические параметры?

- •33. Варианты эсл. Режимы работы.

- •34. Чем хороша и чем плоха схема моп-инвертора, у которой затвор нагрузочного транзистора подсоединен к выходу схемы?

- •35. Схема источника опорного напряжения эсл-вентиля.

- •36. Синтезировать схему ттл с простым инвертором с тремя состояниями. Принципиальная схема, работа, математическая модель, варианты топологий и структур. 17 вопр

- •37. Реализация сложных логических функций на моп-транзисторах. Привести примеры.

- •38. Синтезировать многобазовый транзистор и вентиль (или вентили) на его основе. Принципиальная схема, работа, математическая модель, варианты топологий и структур.

- •39. Схемотехника кмоп-вентилей.

- •40. Спроектировать в базисе и2л 2-х разрядный сумматор с переносом в старший разряд.

- •41. Кмоп-инвертор. Принципиальная схема, работа, математическая модель, варианты топологий и структур.

- •42. Синтезировать и проанализировать структуры инжекционного инвертора с общей выходной областью. Принципиальная схема, работа, математическая модель, варианты топологий и структур.

- •43. Логический элемент и-не на кмоп-транзисторах. Принципиальная схема, работа, математическая модель, варианты топологий и структур.

- •44. Проанализировать различные структуры инжекционных инверторов.

- •45. Логический элемент или-не на кмоп-транзисторах. Принципиальная схема, работа, математическая модель, варианты топологий и структур.

- •46. Синтезировать структуру нстл с общими коллектором и эмиттером. Сайт

- •48. Нарисовать модель фиэ размерностью 8 с двумя циклами и реализовать ее в трех технологиях (эпитаксиально-планарной, с локальной эпитаксией, 3-d).

- •49. Ттл с простым инвертором. Принципиальная схема, работа, математическая модель, варианты топологий и структур.

- •50. Зависит ли мощность кмоп-вентиля от количества логических входов? Если зависит, то как?

- •52. Определить минимальное значение напряжения питания кмоп-вентилей и-не и или-не на 3 входа.

- •53.(55) Ттл со сложным инвертором. Принципиальная схема, работа, математическая модель, варианты топологий и структур.

- •55. Основные характеристики ттл со сложным инвертором.

- •57. Разновидности схем ттл со сложным инвертором.

- •58. Синтезировать схему мэсл без резисторов. Описать ее работу и различные варианты интегральных структур.

- •59. Инжекционный инвертор. Принципиальная схема, работа, математическая модель, варианты топологий и структур.

- •60. Нарисовать модель фиэ размерностью 7 с одним циклом и реализовать ее в трех технологиях (эпитаксиально-планарной, с локальной эпитаксией, 3-d).

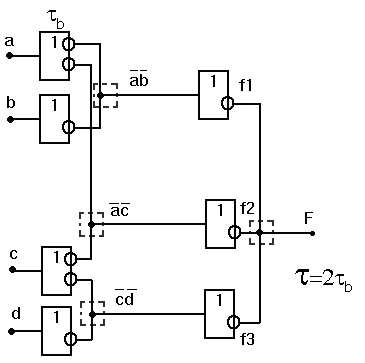

25. Методика проектирования устройств эвм в базисе эсл. Привести примеры.

Алгоритм

проектирования сложных схем в базисе

ЭСЛ ИЛИ-НЕ можно записать следующим

образом:

![]() ,

то есть:

,

то есть:

1. Взять минимальную конъюнктивную нормальную форму функции F.

2. Взять ее двойное отрицание.

3. Раскрыть внутреннее отрицание, использую закон Де Моргана, оставив внешнее отрицание.

Пример:

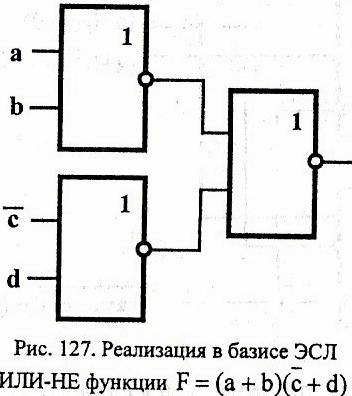

Спроектируем схему

реализующую функцию

![]() в базисе ЭСЛ ИЛИ-НЕ.

в базисе ЭСЛ ИЛИ-НЕ.

В соответствии с алгоритмом преобразуем функцию, оставив в ней только дизъюнкции и инверсии:

![]()

Для реализации, с учетом использования на входах как прямых, так и инверсных аргументов, потребуется 3 вентиля.

Алгоритм

проектирования сложных схем в базисе

ЭСЛ ИЛИ-НЕ-Монтажное ИЛИ можно записать

следующим образом:

![]() ,

то есть:

,

то есть:

1. Взять минимальную дизъюнктивную нормальную форму функции F.

2. Взять двойное отрицание каждой конъюнкции.

3. Раскрыть внутреннее отрицание, использую закон Де Моргана.

Пример:

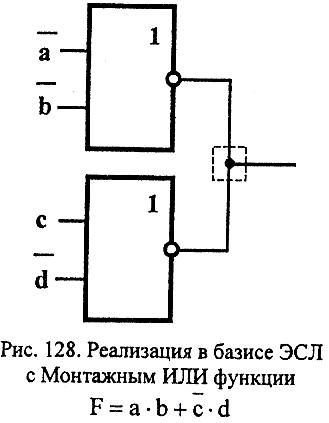

Спроектируем

схему, реализующую функцию

![]() в

базисе ЭСЛ ИЛИ-НЕ-Монтажное ИЛИ.

в

базисе ЭСЛ ИЛИ-НЕ-Монтажное ИЛИ.

В соответствии с алгоритмом преобразуем функцию, оставив в ней только дизъюнкции и инверсии:

![]()

Для реализации, с учетом использования на входах как прямых, так и инверсных аргументов, потребуется 2 вентиля.

В отличие от реализации по предыдущему алгоритму получаем схему, имеющую на один логический уровень меньше. Задержка таких схем – меньше на задержку одного вентиля.

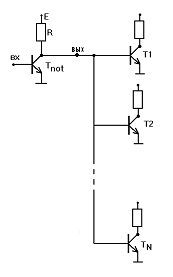

27. Методика проектирования устройств эвм в базисе и2л. Привести примеры.

Алгоритм

проектирования сложных схем в схемотехнике

И2Л можно записать следующим образом:

![]() ,

то есть:

,

то есть:

1. Взять минимальную конъюнктивную нормальную форму функции F.

2. Взять двойное почленное отрицание (над каждой суммой).

3. Раскрыть внутренние отрицания, используя закон Де Моргана, оставив внешнее отрицание. То есть инверсии сумм нужно превратить в произведение инверсий.

Нужно привести логическое уравнение к такому виду, где присутствуют только конъюнкции и инверсии.

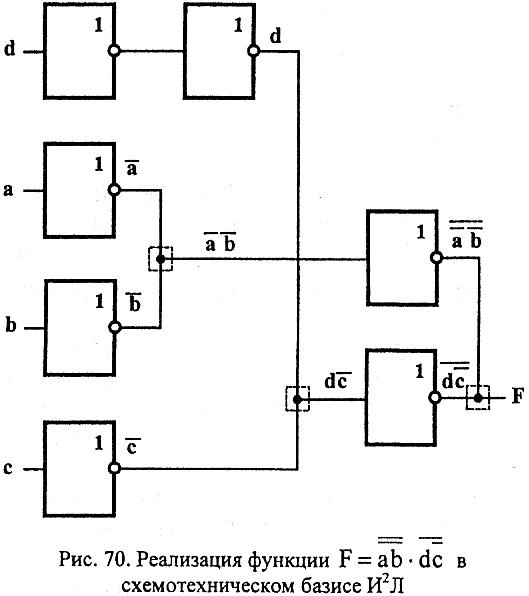

Пример:

Спроектируем схему

реализующую функцию

![]() в базисе И2Л.

в базисе И2Л.

В соответствии с алгоритмом проектирования преобразуем правую часть равенства:

![]()

![]()

![]()

и реализуем это уравнение в базисе И2Л.

реализуем это уравнение в базисе И2Л.

Для того, чтобы

спроектировать сколь угодно сложное

устройство в базисе И2Л, необходимо

взять МКНФ функции. Затем взять двойное

почленное отрицание и раскрыть внутреннее.

![]()

Монтажное И реализуется только тогда, когда аргументы снимаются с выходов инжекционных инверторов.

![]()

![]()

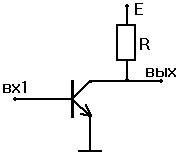

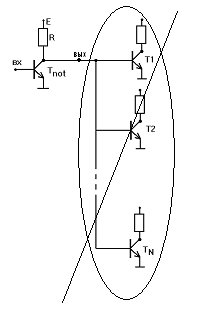

28. Определить минимально возможное значение напряжение питания биполярного инвертора.

Запасы помехоустойчивости.

Запас устойчивости по положительной помехе – это допустимое увеличение напряжения логического нуля на входе, при котором еще не происходит нарушение работы схемы.

Запас устойчивости по отрицательной помехе – это допустимое уменьшение напряжения логической единицы на входе, при котором не происходит нарушение работы схемы.

Статическая мощность логических элементов.

n = 0

![]()

P0, P1 – мощности, соответственно, нуля и единицы. Эти величины определяются по выходу.

Uвых

= U0

Uвых

= U0

На выходе – 0.

Транзистор насыщен.

I = Iнас

Uвых = 1

На выходе – 1

Транзистор закрыт.

![]()

![]()

![]()

2)

![]()

U вых = U0

На выходе ноль, транзистор насыщен.

U вых = 1

Основной транзистор закрыт, а остальные насыщенны.

![]()

![]()