- •1. Сравнительный анализ схемотехнических базисов эвм. Взаимосвязь логического, схемотехнического и конструкторского этапов проектирования.

- •3. Синтезировать принципиальную схему ттлш без резисторов, разработать структуру (математическую модель-дерево); сделать 3-х мерный вариант; описать работу полученного элемента.

- •4. Схемотехника моп-вентилей. Принципы синтеза.

- •5. Синтезировать модификации схем ттл с простым и сложным инверторами с низкоомным путем для рассасывания заряда q2.

- •- Нагрузочная способность

- •6. Сравнительный анализ схем инверторов на моп-транзисторах.

- •7. Определить минимальное значение напряжения питания для схемы ттл со сложным инвертором. 56 стр в лекциях?

- •8. Логический элемент и-не на моп-транзисторах. Принципиальная схема, работа, математическая модель, варианты топологий и структур.

- •9. Определить напряжение логической «1»схемы ттл с простым инвертором с открытым коллектором.

- •10. Логический элемент или-не на моп-транзисторах. Принципиальная схема, работа, математическая модель, варианты топологий и структур.

- •11. Рассчитать напряжение логической «1»схемы ттлш с простым инвертором.

- •12. Нарисовать модель фиэ размерностью 6 с одним циклом и реализовать ее в трех технологиях (эпитаксиально-планарной, с локальной эпитаксией, 3-d).

- •13. Схемотехника транзисторно-транзисторных элементов (ттл).

- •14. Существует ли кмоп логический вентиль с нечетным количеством транзисторов? Если существует, приведите пример. Опишите его работу.

- •15. Реализация функции и-или-не в ттл-схемотехнике.

- •16. Разработать математическую модель (граф) мэсл с минимальным количеством полупроводниковых областей (вершин графа).

- •17. (36) Схема ттл с тремя состояниями. Работа. Варианты использования.

- •18. Чем определяется напряжение питания в этих схемах, и зависит ли оно от входного вентиля (моп-вентили или-не и и-не)?

- •24. Синтезировать в различных схемотехнических базисах схемы или, математические модели которых содержат минимальное количество полупроводниковых областей.

- •26. Сравнить математические модели n-моп и кмоп инверторов. Синтезировать их трехмерные структуры.

- •25. Методика проектирования устройств эвм в базисе эсл. Привести примеры.

- •27. Методика проектирования устройств эвм в базисе и2л. Привести примеры.

- •28. Определить минимально возможное значение напряжение питания биполярного инвертора.

- •Статическая мощность логических элементов.

- •29. Методика проектирования устройств эвм в моп и кмоп схемотехниках. Привести примеры.

- •30. Синтезировать элемент с тремя состояниями в любой схемотехнике кроме ттл.

- •31. Схемотехника элементов эмиттерно-связанной логики (эсл).

- •Мэсл (маломощная эсл)

- •Увеличение быстродействия за счет уменьшения входного сопротивления

- •Реализацию дополнительной логической функции монтажное или (параллельное соединение эмиттерных повторителей)

- •32. Чем определяется напряжение питания моп-вентилей и-не? Как это влияет на другие технические параметры?

- •33. Варианты эсл. Режимы работы.

- •34. Чем хороша и чем плоха схема моп-инвертора, у которой затвор нагрузочного транзистора подсоединен к выходу схемы?

- •35. Схема источника опорного напряжения эсл-вентиля.

- •36. Синтезировать схему ттл с простым инвертором с тремя состояниями. Принципиальная схема, работа, математическая модель, варианты топологий и структур. 17 вопр

- •37. Реализация сложных логических функций на моп-транзисторах. Привести примеры.

- •38. Синтезировать многобазовый транзистор и вентиль (или вентили) на его основе. Принципиальная схема, работа, математическая модель, варианты топологий и структур.

- •39. Схемотехника кмоп-вентилей.

- •40. Спроектировать в базисе и2л 2-х разрядный сумматор с переносом в старший разряд.

- •41. Кмоп-инвертор. Принципиальная схема, работа, математическая модель, варианты топологий и структур.

- •42. Синтезировать и проанализировать структуры инжекционного инвертора с общей выходной областью. Принципиальная схема, работа, математическая модель, варианты топологий и структур.

- •43. Логический элемент и-не на кмоп-транзисторах. Принципиальная схема, работа, математическая модель, варианты топологий и структур.

- •44. Проанализировать различные структуры инжекционных инверторов.

- •45. Логический элемент или-не на кмоп-транзисторах. Принципиальная схема, работа, математическая модель, варианты топологий и структур.

- •46. Синтезировать структуру нстл с общими коллектором и эмиттером. Сайт

- •48. Нарисовать модель фиэ размерностью 8 с двумя циклами и реализовать ее в трех технологиях (эпитаксиально-планарной, с локальной эпитаксией, 3-d).

- •49. Ттл с простым инвертором. Принципиальная схема, работа, математическая модель, варианты топологий и структур.

- •50. Зависит ли мощность кмоп-вентиля от количества логических входов? Если зависит, то как?

- •52. Определить минимальное значение напряжения питания кмоп-вентилей и-не и или-не на 3 входа.

- •53.(55) Ттл со сложным инвертором. Принципиальная схема, работа, математическая модель, варианты топологий и структур.

- •55. Основные характеристики ттл со сложным инвертором.

- •57. Разновидности схем ттл со сложным инвертором.

- •58. Синтезировать схему мэсл без резисторов. Описать ее работу и различные варианты интегральных структур.

- •59. Инжекционный инвертор. Принципиальная схема, работа, математическая модель, варианты топологий и структур.

- •60. Нарисовать модель фиэ размерностью 7 с одним циклом и реализовать ее в трех технологиях (эпитаксиально-планарной, с локальной эпитаксией, 3-d).

14. Существует ли кмоп логический вентиль с нечетным количеством транзисторов? Если существует, приведите пример. Опишите его работу.

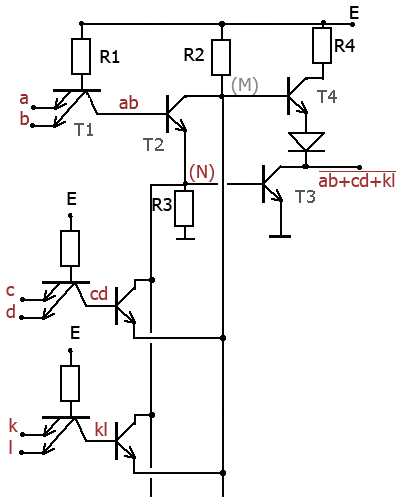

15. Реализация функции и-или-не в ттл-схемотехнике.

ТТЛ с расширителем И-ИЛИ-НЕ.

![]() -

на выходе.

расширитель

-

на выходе.

расширитель

Здесь может быть шесть расширителей (определяется режимом работы и задержки).

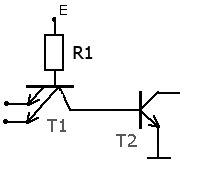

Для реализации дополнительной функции ИЛИ в схемотехническом базисе ТТЛ со сложным инвертором используется схема расширителя.

«Открытость» коллектора и эмиттера транзистора Т2 делает возможным параллельное соединение с транзисторами Т2 других расширителей, которые на входе реализуют функции конъюнкции.

Параллельное соединение транзисторов – это схема «зависимого» ИЛИ, т.е. не выполняющая функцию без нагрузки, которая, как правило, реализует инверсию.

В схеме k расширителей включены параллельно и подсоединены к узлам M и N.

Общий коллектор схемы ИЛИ имеет резистивную нагрузку в виде резистора R2, который является частью сложного инвертора. Поэтому в данной схеме многоэмиттерные транзисторы в совокупности с резисторами R1 реализуют конъюнкции, параллельное соединение транзисторов – функцию ИЛИ, а сложный инвертор – функцию НЕ.

Количество расширителей вентиля И-ИЛИ-НЕ k ограничено следующими соображениями. Когда все транзисторы Т2 закрыты, Т3 также должен быть закрыт, и на выходе схемы должна быть логическая единица. Однако при наличии токов утечки в закрытых транзисторах Т2 через резистор R3 потечет суммарный ток утечки, который создаст на нем падение напряжения, достаточное для отпирания транзистора Т3. А это приведет к нарушению логики работы схемы. Поэтому количество расширителей ограничено, как правило, 5 или 6.

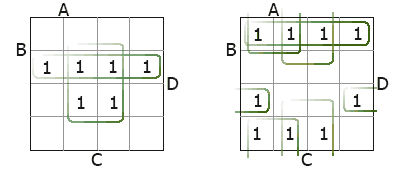

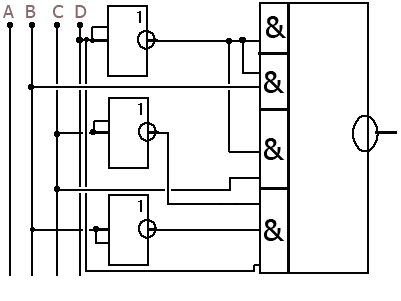

Пример:

F = (0, 3, 5, 7, 11, 13, 15)

16. Разработать математическую модель (граф) мэсл с минимальным количеством полупроводниковых областей (вершин графа).

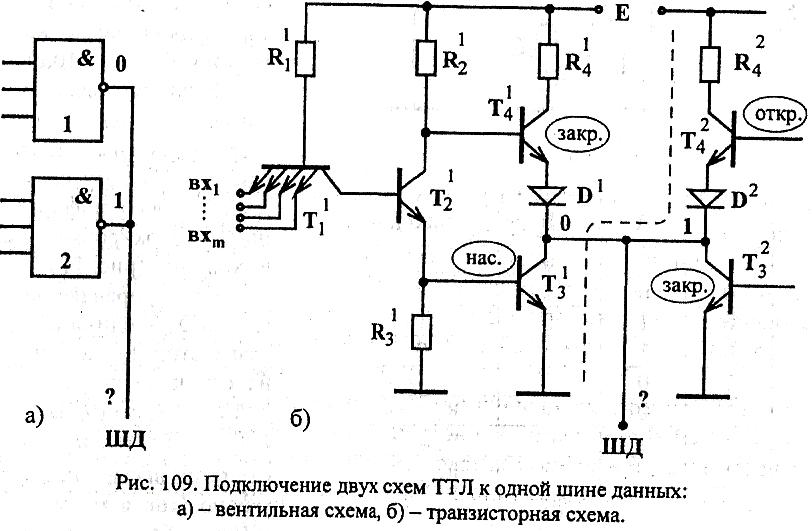

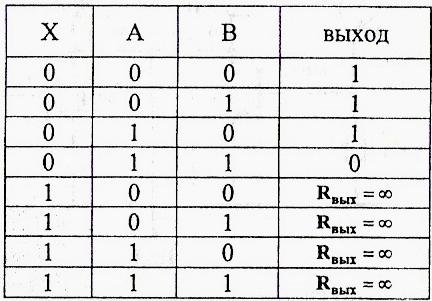

17. (36) Схема ттл с тремя состояниями. Работа. Варианты использования.

Схема ТТЛ с тремя состояниями – это схема ТТЛ с возможностью блокировки выхода. Необходимость в этой схеме может возникнуть в случае, когда несколько схем ТТЛ со сложным инвертором выходами подключены к одной шине данных (ШД).

![]()

В случае, когда на выходе одной схемы – логический ноль, а на выходе другой – логическая единица, возникает проводящая последовательная цепь E-R42- T42- T31, по сути являющаяся делителем напряжения. Потенциал в выходном узле установится не 0 и не 1, а будет неопределенным, зависящим от параметров транзисторов и резистора цепи.

Поэтому необходима возможность отключения (блокировки) выхода той схемы, которая в конкретный момент времени не должна выдавать информацию в шину данных.

Эта возможность реализована в схеме ТТЛ с тремя состояниями.

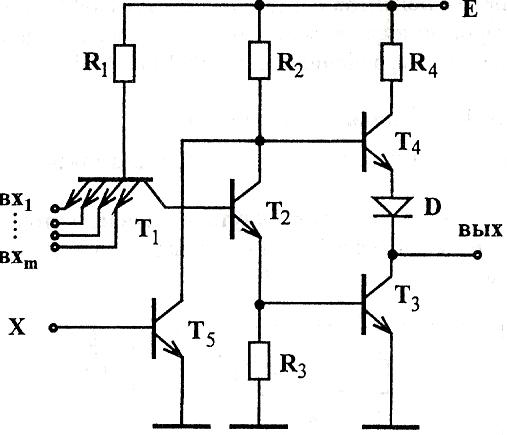

Схема ТТЛ с тремя состояниями отличается от базовой тем, что подключен дополнительный пятый транзистор Т5, на базу которого подается управляющий сигнал Х и его коллектор подключен к коллектору Т2.

Если управляющий сигнал Х – ноль, транзистор Т5 закрыт и не влияет на работу схемы (схема выдает информацию), блокировки по выходу нет.

Если управляющий сигнал Х-единица, то транзистор Т5 насыщен, на его коллекторе низкий потенциал, Т4 и Т3 – закрыты, Rвых=∞, схема не выдает информацию (ток в нагрузку).

x |

A |

B |

T1 |

T2 |

T3 |

T4 |

T5 |

выход |

0 |

0 |

0 |

|

|

|

|

закрыт |

1 |

0 |

0 |

1 |

|

|

|

|

закрыт |

1 |

0 |

1 |

0 |

|

|

|

|

закрыт |

1 |

0 |

1 |

1 |

|

|

|

|

закрыт |

0 |

1 |

0 |

0 |

|

|

закрыт |

закрыт |

насыщен |

|

1 |

0 |

1 |

|

|

закрыт |

закрыт |

насыщен |

|

1 |

1 |

0 |

|

|

закрыт |

закрыт |

насыщен |

|

1 |

1 |

1 |

|

|

закрыт |

закрыт |

насыщен |

|