- •Лекция 1

- •1.Микросхемотехника, история и этапы развития.

- •2.Этапы проектирования интегральных микросхем.

- •10. Ключи на биполярном транзисторе.

- •13.Типовый элемент ттл-логики с простым инвертором. Статические характеристики.

- •14. Типовй элемент ттл – логики с простым инвертором. Динамические характеристики.

- •18. Элементы ттл и дтл с диодами и транзисторами Шотки (тшл).

- •19. Типовой элемент эсл. Статические характеристики.

- •20. Типовой элемент эсл. Динамические характеристики.

13.Типовый элемент ттл-логики с простым инвертором. Статические характеристики.

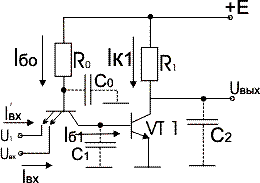

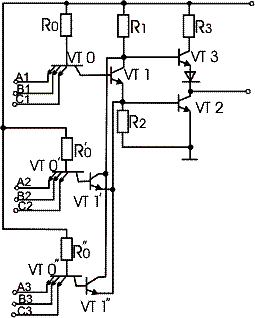

Схема элемента состоит из многоэмитерного транзистора VT0 (МЭТ), выполняющего логическую операцию И, транзисторного ключа инвертора VT1 (рис. 1.13). На выходе элемента реализуется функция И-НЕ.

Рисунок 1.13 – элемент И-НЕ ТТЛ с простым инвертором

Рисунок 1.14 – Типовая передаточная характеристика и зависимостинапряжений на базах VT0, VT1 от потенциала Uвх или Е=3В.

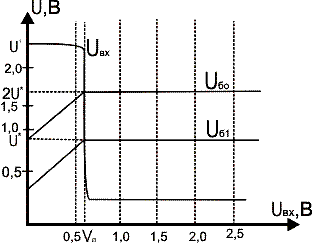

Передаточная характеристика Uвых=f(Uвх) при изменении потенциала Uвх на Мо входах схемы (1М0М) и поступлении на остальные М-М0 входов постоянного высокого потенциала U1 показана на рис.1.14.

Когда Uвх=U0≈0, то соответствующие М0 входных эмитерных переходов МЭТ открыты и потенциал его базы Uбо=U*. Коллекторный переход МЭТ открыт, и потенциал на базе транзистора VT1 равен Uб1=Uвх+Uост.о< U*, где Uост.о – остаточное напряжение на насыщенном МЭТ . Транзистор VT1 закрыт, и на выходе схемы устанавливается высокий потенциал Uвых= U1.

U=E – I1H * R1 (1)

При увеличении Uвх потенциалы Uб0 Uб1 возрастают. Когда потенциал Uб1 достигает величины напряжения отпирания эмиттерного перехода: Uб1= U1, транзистор VT1 открывается и потенциал Uвых уменьшается. Это происходит когда величина Uвх достигает значения порога переключения Vп , которое определяется выражением

Vп = U*-Uост.о.

Потенциал Uб0 устанавливается на уровне Uб0≈2U*, и при дальнейшем увеличении Uвх все эмиттерные переходы МЭТ запираются. МЭТ работает в инверсном режиме, и через его коллекторный переход в базу VT1 поступает ток, вызывающий насыщение транзистора.

В результате на выходе схемы устанавливается низкий потенциал U0, равный остаточному напряжению на насыщенном транзисторе VT1.

Для повышения помехоустойчивости Uп+, Uп- необходимо обеспечить малые значения напряжения Uост.о

Uп+=U*-Uост.о-U0,

Uп-= U1-U*-Uост.о.

Для уменьшения Uост.о целесообразно увеличить коэффициент В11- инверсный коэффициент усиления тока для каждого из элементов МЭТ.

14. Типовй элемент ттл – логики с простым инвертором. Динамические характеристики.

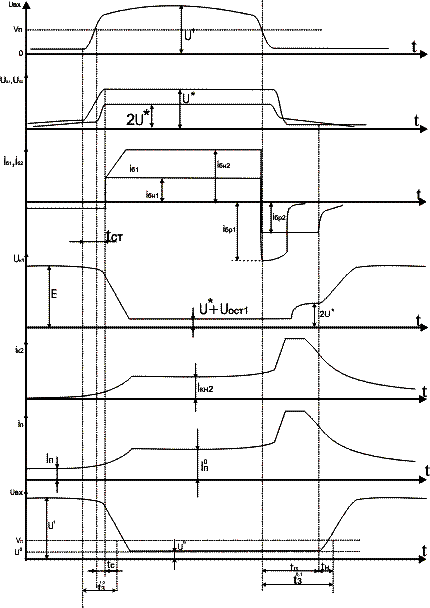

Переходные характеристики (динамические) (рис.1.15). Процесс переключения элемента состоит из нескольких этапов .

Стирание транзистора.

При поступлении на М0 входов элемента положительного перепада потенциала Uвх соответствующие эмиттерные переходы МЭТ запираются.

Потенциалы Uб0 и Uб1 увеличиваются вследствие заряда емкостей С0, С1, подключенных к базам транзисторов VT0, VT1 через резистор R0.

Время отпирания t0 представляет собой задержку между началом возрастания потенциала Uвх и началом формирования отрицательного фронта потенциала Uвых.(рис.1.15).

![]()

где

![]() -

постоянная времени заряда емкостей

С0, С1.

-

постоянная времени заряда емкостей

С0, С1.

Рисунок 1.15 – Переходные процессы в элементе ТТЛ с простым инвертором.

Спад выходного потенциала до порога переключения Vп. После отпирания транзистора VT1 элемент работает как транзисторный ключ с общим эмиттером в активном режиме. При отпирании VT1, выходной потенциал его уменьшается, начиная с U1≈Е:

![]()

![]()

![]() Емкость

С2=Сп2 + СН является

суммой паразитных емкостей Сп2

металлических соединений и общей

емкости нагрузки СН. Потенциал

Uвых снижается до

значения порога переключения Vп

за промежуток времени спада:

Емкость

С2=Сп2 + СН является

суммой паразитных емкостей Сп2

металлических соединений и общей

емкости нагрузки СН. Потенциал

Uвых снижается до

значения порога переключения Vп

за промежуток времени спада:

![]()

![]() где

где

![]() -

постоянная времени спада.

-

постоянная времени спада.

![]() Далее

выходной потенциал уменьшается до

величины Uвых=U0

=Uост.1 и фиксируется

на этом уровне, так как транзистор

входит в насыщение.

Далее

выходной потенциал уменьшается до

величины Uвых=U0

=Uост.1 и фиксируется

на этом уровне, так как транзистор

входит в насыщение.

![]() Рассасывание

избыточного заряда.

Рассасывание

избыточного заряда.

![]() При

поступлении на входы отрицательного

периода Uвх

открываются соответствующие эмиттерные

переходы и МЭТ из инверсного режима

переходит в режим насыщения. Происходит

рассасывание избыточного заряда в

транзисторе под действием базового

тока рассасывания iб1=Ібр1,

вытекающего из базы VT1

через насыщенный МЭТ.

При

поступлении на входы отрицательного

периода Uвх

открываются соответствующие эмиттерные

переходы и МЭТ из инверсного режима

переходит в режим насыщения. Происходит

рассасывание избыточного заряда в

транзисторе под действием базового

тока рассасывания iб1=Ібр1,

вытекающего из базы VT1

через насыщенный МЭТ.

![]() Время

рассасывания tp

представляет собой задержку между

моментом достижения потенциалом Uвх

порога переключения Vп

и началом формирования фронта

потенциала Uвых .

Время

рассасывания tp

представляет собой задержку между

моментом достижения потенциалом Uвх

порога переключения Vп

и началом формирования фронта

потенциала Uвых .

![]() Нарастание

выходного потенциала.

Нарастание

выходного потенциала.

![]() После

окончания рассасывания транзистор VT1

запирается. Начинается возрастание

выходного потенциала вследствие заряда

емкости (Ск+С2).

После

окончания рассасывания транзистор VT1

запирается. Начинается возрастание

выходного потенциала вследствие заряда

емкости (Ск+С2).

![]()

![]()

![]() Постоянное

время нарастания

Постоянное

время нарастания

![]() .

.

![]() Потенциал

Uвых достигает

порога переключения

Потенциал

Uвых достигает

порога переключения

![]() за время нарастания

за время нарастания

![]() .

.

![]() Проведенный

анализ статических и переходных

характеристик элемента ТТЛ с простым

инвертором показывает, что его

целесообразно использовать при малых

значениях помех (Uп≤0,1В)

и емкостей нагрузки (СН<5-10 пФ).

Проведенный

анализ статических и переходных

характеристик элемента ТТЛ с простым

инвертором показывает, что его

целесообразно использовать при малых

значениях помех (Uп≤0,1В)

и емкостей нагрузки (СН<5-10 пФ).

![]() Такие

условия обеспечиваются в микросхемах

высокой степени интеграции (БИС).

Такие

условия обеспечиваются в микросхемах

высокой степени интеграции (БИС).

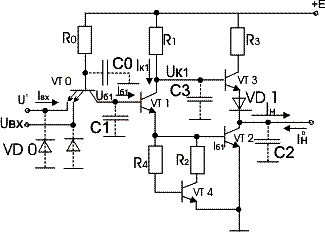

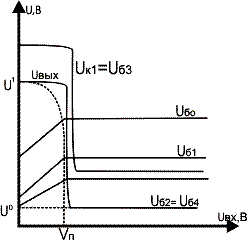

16. Типовой элемент ТТЛ- логики со сложным инвертором. Статические характеристики.

Использование в элементах ТТЛ сложного инвертора позволяет существенно увеличить помехоустойчивость и коэффициент разветвления , и также повысить быстродействие схемы при работе на значительную емкостную нагрузку.

Типовая схема ТТЛ со сложным инвертором показана на рис.1.16.

Рисунок 1.16 – Элемент И-НЕ ТТЛ со сложным инвертором .

Рисунок 1.17 – Типовая передаточная характеристика

Сложный инвертор состоит из фазоразделяющего (транзисторы VT1, VT4, резисторы R1, R2, R4), и выходного (транзисторы VT2, VT3, резистор R3, диод VD1) каскадов.

![]() Первый

каскад обеспечивает управляющие сигналы

для противофазного переключения

выходных транзисторов. Резистор R3

служит для ограничения тока в выходном

каскаде во время выключения схемы,

когда транзистор VT2 еще

находится в режиме насыщения, а транзистор

VT3 уже открылся.

Первый

каскад обеспечивает управляющие сигналы

для противофазного переключения

выходных транзисторов. Резистор R3

служит для ограничения тока в выходном

каскаде во время выключения схемы,

когда транзистор VT2 еще

находится в режиме насыщения, а транзистор

VT3 уже открылся.

![]() На

входах ТТЛ обычно включаются диоды

VD0, которые называются

антизвонными. Эти диоды ограничивают

амплитуду отрицательных помех V-,

образующихся при распространении

логических сигналов в линиях связи

между микросхемами из-за отражения на

концах несогласованных линий. В

результате амплитуда помехи будет

меньше порога переключения

На

входах ТТЛ обычно включаются диоды

VD0, которые называются

антизвонными. Эти диоды ограничивают

амплитуду отрицательных помех V-,

образующихся при распространении

логических сигналов в линиях связи

между микросхемами из-за отражения на

концах несогласованных линий. В

результате амплитуда помехи будет

меньше порога переключения

![]() .

Порог переключения элемента

.

Порог переключения элемента

![]() .

.

![]() Помехоустойчивость

Помехоустойчивость

![]()

![]()

![]()

![]() .

.

![]() Статические

характеристики.

Статические

характеристики.

![]()

![]() элементы представлены на рис. 1.17.

элементы представлены на рис. 1.17.

![]() При

подаче на М0 входов высокого

потенциала Uвх=U0,

а на остальные М входов высокого

потенциала U1>Vп

открыты М0 эмиттерных переходов

и коллекторный переход VT0.

Потенциал на базе VT0 равен

При

подаче на М0 входов высокого

потенциала Uвх=U0,

а на остальные М входов высокого

потенциала U1>Vп

открыты М0 эмиттерных переходов

и коллекторный переход VT0.

Потенциал на базе VT0 равен

![]() ,

а на базе VT1

,

а на базе VT1

![]() .

Транзисторы VT1, VT2,

VT4 закрыты, транзистор

VT3 открыт, и на выходе

поддерживается высокий потенциал U1.

.

Транзисторы VT1, VT2,

VT4 закрыты, транзистор

VT3 открыт, и на выходе

поддерживается высокий потенциал U1.

![]() При

увеличении Uвх

потенциалы Uбо и

Uб1,

растут, пока

Uвх не достигает

значения Vп. При

этом

При

увеличении Uвх

потенциалы Uбо и

Uб1,

растут, пока

Uвх не достигает

значения Vп. При

этом

![]() и транзисторы VT1, VT2,

VT4 открываются . Начинает

протекать коллекторный ток VT1,

вследствие чего потенциалы Uk1

и

и транзисторы VT1, VT2,

VT4 открываются . Начинает

протекать коллекторный ток VT1,

вследствие чего потенциалы Uk1

и

![]() уменьшаются.

уменьшаются.

При дальнейшем увеличении Uвх, эмиттерные переходы МЭТ запираются. Транзистор VT1 входит в режим насыщения.

![]() В

базу VT2 поступает ток

Iб2, вызывающий его

насыщение.

В

базу VT2 поступает ток

Iб2, вызывающий его

насыщение.

![]()

![]()

![]() На

выходе элемента устанавливается низкий

потенциал U0. Разность

потенциалов между коллектором VT1

и выходом эмитера недостаточна для

отпирания последовательно включенных

VT3 и VD1:

На

выходе элемента устанавливается низкий

потенциал U0. Разность

потенциалов между коллектором VT1

и выходом эмитера недостаточна для

отпирания последовательно включенных

VT3 и VD1:

![]() Поэтому VT3 и

VD1 закрыты и коллекторный

ток VT2 равен

Поэтому VT3 и

VD1 закрыты и коллекторный

ток VT2 равен

![]() где

где

![]() - выходной ток, поступающий от нагрузки.

- выходной ток, поступающий от нагрузки.

![]() Порог

переключения элемента ТТЛ со сложным

инвертором приблизительно в 2 раза

выше, чем элемента с простым инвертором.

Поэтому элементы ТТЛ со сложным

инвертором имеют значительно более

высокую помехоустойчивость

Порог

переключения элемента ТТЛ со сложным

инвертором приблизительно в 2 раза

выше, чем элемента с простым инвертором.

Поэтому элементы ТТЛ со сложным

инвертором имеют значительно более

высокую помехоустойчивость

![]() при Т=+200 С и

при Т=+200 С и

![]() при Т=+1250 С.

при Т=+1250 С.

![]() Переходные

(динамические) характеристики.

Переходные

(динамические) характеристики.

![]() Процесс

переключения разбивается та такие же

этапы, как для схемы с простым инвертором

(рис.1.18).

Процесс

переключения разбивается та такие же

этапы, как для схемы с простым инвертором

(рис.1.18).

![]() Отпирание

VT1.

Отпирание

VT1.

![]() При

поступлении на вход схемы положительного

периода Uвх открытые

эмиттерные переходы МЭТ запираются.

Начинается увеличение потенциалов

Uбо, Uб1

на базах VT0 и VT1

вследствие заряда паразитных емкостей

С0, С1 через резистор R0.

Транзисторы VT1, VT2,

VT4 открываются, когда

потенциалы Uб0, Uб1

возрастают до величины 2U*.

При

поступлении на вход схемы положительного

периода Uвх открытые

эмиттерные переходы МЭТ запираются.

Начинается увеличение потенциалов

Uбо, Uб1

на базах VT0 и VT1

вследствие заряда паразитных емкостей

С0, С1 через резистор R0.

Транзисторы VT1, VT2,

VT4 открываются, когда

потенциалы Uб0, Uб1

возрастают до величины 2U*.

![]() Рисунок

1.18 – Переходные процессы в элементе

ТТЛ со сложным инвертором.

Рисунок

1.18 – Переходные процессы в элементе

ТТЛ со сложным инвертором.

![]() Длительность

этапа отпирания

Длительность

этапа отпирания

![]() .

.

Спад выходного потенциала.

![]() После

отпирания транзисторов VT1

и VT2 их коллекторные токи

возрастают, а потенциалы их коллекторов

UK1

Uвых уменьшаются.

После

отпирания транзисторов VT1

и VT2 их коллекторные токи

возрастают, а потенциалы их коллекторов

UK1

Uвых уменьшаются.

![]() Время

спада Uвых до

значения

Время

спада Uвых до

значения

![]() .

.

![]() Далее

транзисторы VT1, VT2,

VT4 входят в режим насыщения.

Транзистор VT3 и

диод VD1 запираются и

на выходе устанавливается потенциал

Uвых=V0.

Далее

транзисторы VT1, VT2,

VT4 входят в режим насыщения.

Транзистор VT3 и

диод VD1 запираются и

на выходе устанавливается потенциал

Uвых=V0.

![]() Рассасывание

избыточного заряда в транзисторе VT2.

Когда напряжение на коллекторе VT1

достигает значения

Рассасывание

избыточного заряда в транзисторе VT2.

Когда напряжение на коллекторе VT1

достигает значения

![]() ,

отпирается транзистор VT3

и диод VD1. Через них и

насыщенный транзистор VT2

протекает значительный сквозной ток,

величина которого ограничивается

сопротивлением R3

,

отпирается транзистор VT3

и диод VD1. Через них и

насыщенный транзистор VT2

протекает значительный сквозной ток,

величина которого ограничивается

сопротивлением R3

![]() .

Сопротивление R3 выбирается

исходя из заданного значения предельно

допустимого тока транзисторов VT2,

VT3 и диода VD1

и обычно сопротивлений 50-500 Ом.

.

Сопротивление R3 выбирается

исходя из заданного значения предельно

допустимого тока транзисторов VT2,

VT3 и диода VD1

и обычно сопротивлений 50-500 Ом.

![]() через

насыщенный транзистор VT4

протекает ток

через

насыщенный транзистор VT4

протекает ток

![]() ,

вызывающий рассасывание избыточного

заряда в насыщенном транзисторе VT2.

,

вызывающий рассасывание избыточного

заряда в насыщенном транзисторе VT2.

![]() Нарастание

выходного потенциала.

Нарастание

выходного потенциала.

![]() После

окончания рассасывания транзистор VT2

запирается. Происходит увеличение

потенциала UK1

вследствие заряда эквивалентной емкости

С3, через резистор R1

После

окончания рассасывания транзистор VT2

запирается. Происходит увеличение

потенциала UK1

вследствие заряда эквивалентной емкости

С3, через резистор R1

![]()

![]() Транзистор

VT4 работает как эмиттерный

повторитель в активном режиме, обеспечивая

быстрый перезаряд емкостей, подключенных

к выходу схемы.

Транзистор

VT4 работает как эмиттерный

повторитель в активном режиме, обеспечивая

быстрый перезаряд емкостей, подключенных

к выходу схемы.

![]() .

Выходной потенциал нарастает до значения

.

Выходной потенциал нарастает до значения

![]() за время

за время

![]()

Далее потенциал Uвых экспотенциально возрастает до U1. Таким образом, благодаря включению транзистора VT3 в сложном инверторе влияние емкости CН на время нарастания tn оказывается значительно слабее, чем в простом инверторе.

![]() Наличие

«пиков» тока питания может вызывать

генерацию значительных помех на шинах

питания. Для предотвращения помех между

шинами «напряжения питания» и «земля»

на печатным платах содержащих элементы

ТТЛ, включают конденсаторы емкостью

104-105 пФ.

Наличие

«пиков» тока питания может вызывать

генерацию значительных помех на шинах

питания. Для предотвращения помех между

шинами «напряжения питания» и «земля»

на печатным платах содержащих элементы

ТТЛ, включают конденсаторы емкостью

104-105 пФ.

В этом случае ТТЛ кроме двух обычных состояний выхода (Uвых = U0 и Uвых = U1 ) имеют третье «отключенное» состояние. Для этого в схему со сложным инвертором включают дополнительный диод VD (рис.1.19). При низком потенциале на входе Uх = U0 все транзисторы в схеме оказываются закрытыми, и схема полностью отключена от нагрузки. При Uх = U1 элемент выполняет логическую операцию И–НЕ. Выходы таких элементов можно объединить, если в процессе работы устройства обеспечивать подключение к нагрузке не более одного элемента одновременно. Помимо элементов И–НЕ широкое применение находят созданные на их базе элементы И-ИЛИ-НЕ (рис.1.20)

Рис. 1.20

Каждый МЭТ выполняет операцию И, параллельное включение транзисторов VT1 реализует операцию ИЛИ, и сложный инвертор обеспечивает операцию НЕ. В результате на выходе элемента реализуется функция:

W = А1В1С1 + А2В2С2 + … + АкВкСк

Подключение каждой дополнительной сборки увеличивает потребляемую мощность на

![]() Р

= Е( Е – 2U*)/R0

Р

= Е( Е – 2U*)/R0

и несколько снижает быстродействие из-за возрастания паразитной емкости С3. Максимально допустимое число подключенных сборок k = 6-8.