- •21. Элементы эмиттерно-функциональной логики (эфл).

- •22. Элементы мало сигнальной эмиттерно-связанной логики (мэсл).

- •23. Особенности применения элементов эсл. Реализация монтажных логических операций.

- •24. Элементы инжекционной интегральной логики. Статические характеристики (и2л).

- •Статические характеристики.

- •25. Элементы инжекционной интегральной логики. Динамические арактеристики.

- •28. Типовые элементы мдп – логики. Статические характеристики.

- •29. Типовые элементы кмдп логики. Динамические характеристики.

- •30. Разновидности элементов мдп – логики и принцип их работы.

- •31. Типовой элемент кмдп – логики. Статические характеристики.

- •32. Типовые элементы кмдп – логики. Динамические характеристики.

- •33. Особенности построения, элементарная база и структура бис (сбис).

- •34.Общая структура бис, входные и выходные транзисторы.

- •35. Преобразователи уровней цифровых имс. Общие сведения.

- •36. Преобразование уровней ттл к мдп и обратно.

- •37. Преобразователи уровней ттл, эсл и обратно.

- •38. Преобразователи уровней ттл, и2л и обратно.

- •39. Преобразователи уровней ттл, кмдп и обратно.

21. Элементы эмиттерно-функциональной логики (эфл).

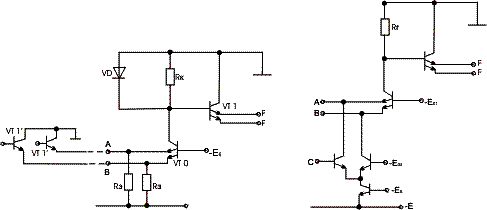

В системах ЭСЛ особенно широко применяется многоступенчатое включение переключателей тока, что существенно расширяет их логические возможности. Разновидностью элементов ЭСЛ является элементы так называемой эмиттерно- функциональной логики (ЭФЛ) (рис.1.24).

Рис.1.24 Одноступенчатый и двухступенчатый элементы ЭФЛ.

Если в схеме ЭФЛ на рис.1.24 ,а низкий

потенциал

![]() подан

хотя бы на один вход, то соответствующий

эмиттерный переход VT0

открыт и его коллекторный ток течет

через резистор Rк и диод

VD. Потенциал коллектора

VT0 равен

подан

хотя бы на один вход, то соответствующий

эмиттерный переход VT0

открыт и его коллекторный ток течет

через резистор Rк и диод

VD. Потенциал коллектора

VT0 равен

![]() ,

и на выходе установится низкий потенциал

,

и на выходе установится низкий потенциал

![]() .

При высоком потенциале на всех входах

.

При высоком потенциале на всех входах

![]() закрыт, потенциал на его коллекторе

равен нулю и на выходе устанавливается

высокий потенциал

закрыт, потенциал на его коллекторе

равен нулю и на выходе устанавливается

высокий потенциал

![]() .

Таким образом, схема реализует на выходе

операцию коньюнкции

.

Таким образом, схема реализует на выходе

операцию коньюнкции

![]() АВ.

При соединении выходов схем ЭФЛ, как и

схема ЭСЛ, реализуется операция

АВ.

При соединении выходов схем ЭФЛ, как и

схема ЭСЛ, реализуется операция

ИЛИ.

При рассмотрении ЭФЛ с выходными

транзисторами

![]() 1

предыдущих элементов видно, что элемент

ЭФЛ представляет собой два переключателя

тока, в которых отсутствует инверсные

выходы (

1

предыдущих элементов видно, что элемент

ЭФЛ представляет собой два переключателя

тока, в которых отсутствует инверсные

выходы (![]() =0),а

опорные транзисторы, коллекторы которые

подключены к резистору Rк,

совмещены в один много эмиттерный

транзистор

=0),а

опорные транзисторы, коллекторы которые

подключены к резистору Rк,

совмещены в один много эмиттерный

транзистор

![]() .

Поэтому большинство параметров схем

ЭСЛ и ЭФЛ имеет близкие значения.

.

Поэтому большинство параметров схем

ЭСЛ и ЭФЛ имеет близкие значения.

Достоинство схем ЭФЛ является более высокое быстродействие, что объясняется меньшим числом компонентов и соответственно уменьшенными значениями паразитных емкостей. Однако схема ЭФЛ не обладает функциональной полнотой, так как не выполняет операцию инверсии. Поэтому при реализации многих функций элементы ЭФЛ используются совместно с инверторами ЭСЛ.

Другой способ реализации инверсии в схемах ЭФЛ состоит в применении переключателя тока вместо резисторов Rэ (рис.1,24,б). При поступлении на вход переключателя логического сигнала С на выходе схемы реализуется операция F=АС+ВС, обладающая функциональной полнотой.

22. Элементы мало сигнальной эмиттерно-связанной логики (мэсл).

Для повышения быстродействия испытания

потребляемой мощности в схемах ЭСЛ

целесообразно уменьшить значения Е и

Ил. При этом можно исключить

эмиттерные повторители, потребляющие

значительную мощность, и использовать

простейший вариант схемы, показанный

на рис.1.25,а. В такой схеме транзисторы

входят в режим насыщения, но если

![]() <0,4-0,5

В, то степень насыщения мала: S<Smin.

Такой режим работы транзистора называется

квазинасыщенным.

<0,4-0,5

В, то степень насыщения мала: S<Smin.

Такой режим работы транзистора называется

квазинасыщенным.

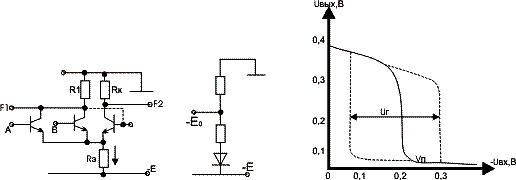

Рис. 1.25 Элемент МЭСЛ а) и его передаточная характеристика б).

При этом время рассасывания избыточного

заряда в транзисторах пренебрежимо

мало: tр<< tз.

Задержка переключения tз

оказывается значительно ниже (в 2

раза и более), чем в схемах ЭСЛ. Данная

модификация схем ЭСЛ называется

малосигнальной эмиттерно-связанной

логики (МЭСЛ), так как величина

логического перепада для них обычно

составляет Uл

![]() 0,3-0,4

В. Передаточная характеристика схемы

МЭСЛ показана на рис.1.25,б. Высокий

потенциал

0,3-0,4

В. Передаточная характеристика схемы

МЭСЛ показана на рис.1.25,б. Высокий

потенциал

![]() на выходе схемы определяется падением

напряжения на резисторе Rк

при протекании тока нагрузки:

на выходе схемы определяется падением

напряжения на резисторе Rк

при протекании тока нагрузки:

![]() =

-I1нRк.

Низкий потенциал U0

устанавливается при протекании через

резистор Rк коллекторного

тока Iк открытых

транзисторов и равен U0

= - IкRк

~ -( Е- U* )(Rк/Rэ).

Порог переключения Vn=-

Е0=-0,5Uл, где

опорное напряжение Е0 получают

от температурно-компенсированного

делителя. В следствии малого логического

перепада элементы МЭСЛ имеют относительно

низкую помехоустойчивость, которая

составляет U+n~U-n~

100-150 мВ. Так как в схеме отсутствуют

выходные эмиттерные повторители, то

коэффициент разветвления оказывается

значительно ниже, чем для элементов

ЭСЛ, и обычно составляет N=4-5.

В схеме МЭСЛ используется напряжение

питания Е=2-3 В. Благодаря снижению Е и

исключению эмиттерных повторителей,

мощность потребляемая этой схемой

в 3-5 раз меньше, чем схемой ЭСЛ.

Задержка переключения при малых

емкостях нагрузки (Сн

=

-I1нRк.

Низкий потенциал U0

устанавливается при протекании через

резистор Rк коллекторного

тока Iк открытых

транзисторов и равен U0

= - IкRк

~ -( Е- U* )(Rк/Rэ).

Порог переключения Vn=-

Е0=-0,5Uл, где

опорное напряжение Е0 получают

от температурно-компенсированного

делителя. В следствии малого логического

перепада элементы МЭСЛ имеют относительно

низкую помехоустойчивость, которая

составляет U+n~U-n~

100-150 мВ. Так как в схеме отсутствуют

выходные эмиттерные повторители, то

коэффициент разветвления оказывается

значительно ниже, чем для элементов

ЭСЛ, и обычно составляет N=4-5.

В схеме МЭСЛ используется напряжение

питания Е=2-3 В. Благодаря снижению Е и

исключению эмиттерных повторителей,

мощность потребляемая этой схемой

в 3-5 раз меньше, чем схемой ЭСЛ.

Задержка переключения при малых

емкостях нагрузки (Сн![]() 5-10

мФ) оказывается в 2-3 раза ниже, чем

для схем ЭСЛ.

5-10

мФ) оказывается в 2-3 раза ниже, чем

для схем ЭСЛ.

Для увеличения помехоустойчивости схем МЭСЛ можно ввести отрицательную обратную связь, подключив базу опорного транзистора VT0 к инверторному выходу F1 (вместо источника Е0)(рис.1.25,а). При этом порог Vn=Uвых1 и помехоустойчивость схемы возрастет приблизительно вдвое. Однако во столько раз увеличивается и задержка переключения.