- •21. Элементы эмиттерно-функциональной логики (эфл).

- •22. Элементы мало сигнальной эмиттерно-связанной логики (мэсл).

- •23. Особенности применения элементов эсл. Реализация монтажных логических операций.

- •24. Элементы инжекционной интегральной логики. Статические характеристики (и2л).

- •Статические характеристики.

- •25. Элементы инжекционной интегральной логики. Динамические арактеристики.

- •28. Типовые элементы мдп – логики. Статические характеристики.

- •29. Типовые элементы кмдп логики. Динамические характеристики.

- •30. Разновидности элементов мдп – логики и принцип их работы.

- •31. Типовой элемент кмдп – логики. Статические характеристики.

- •32. Типовые элементы кмдп – логики. Динамические характеристики.

- •33. Особенности построения, элементарная база и структура бис (сбис).

- •34.Общая структура бис, входные и выходные транзисторы.

- •35. Преобразователи уровней цифровых имс. Общие сведения.

- •36. Преобразование уровней ттл к мдп и обратно.

- •37. Преобразователи уровней ттл, эсл и обратно.

- •38. Преобразователи уровней ттл, и2л и обратно.

- •39. Преобразователи уровней ттл, кмдп и обратно.

39. Преобразователи уровней ттл, кмдп и обратно.

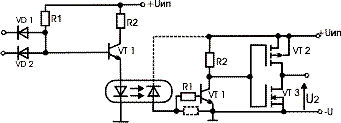

Для преобразования уровней ТТЛ к уровням КМДП используют схему ПУ13 (рис.1.43).

Первый каскад на транзисторе VT1

выполняет роль инвертора – усилителя

логического перепада

![]()

![]() Uл = U1

– U0 ТТЛ до

логического перепада КМДП. Второй каскад

(VT2, VT3)

выполнен в виде ключа на КМДП –

транзисторах. Если на вход ПУ13

поступает от ИМС ТТЛ уровень U10

Uл = U1

– U0 ТТЛ до

логического перепада КМДП. Второй каскад

(VT2, VT3)

выполнен в виде ключа на КМДП –

транзисторах. Если на вход ПУ13

поступает от ИМС ТТЛ уровень U10

![]() 0,4 В, транзистор VT1 заперт,

на его коллекторе устанавливается

высокий потенциал:

0,4 В, транзистор VT1 заперт,

на его коллекторе устанавливается

высокий потенциал:

Uk1

= Uun

– Ik0R2

![]() Uun,

который обуславливает отпирание n

– канального транзистора VT2.

На выходе ПУ13 устанавливается

низкий потенциал U20

Uun,

который обуславливает отпирание n

– канального транзистора VT2.

На выходе ПУ13 устанавливается

низкий потенциал U20

![]() 0. При подаче на вход высокого уровня

U11

0. При подаче на вход высокого уровня

U11

![]() 2,4 В транзистор VT1

насыщается, транзистор VT2

переключается в триодный режим, а

транзистор VT3 – в режим

отсечки, и на выходе ПУ13

устанавливается высокий уровень U21

2,4 В транзистор VT1

насыщается, транзистор VT2

переключается в триодный режим, а

транзистор VT3 – в режим

отсечки, и на выходе ПУ13

устанавливается высокий уровень U21

![]() Uun.

Uun.

Рис. 1.43

Достоинство схемы (рис. 1.43) – простота, высокое быстродействие и низкое энергопотребление.

Недостаток – низкая

помехозащищенность ПУ13 на уровне

«0» входного сигнала. Согласование

выходов ТТЛ – элементов со схемами p

– МДП, n –МДП и КМДП удобно

выполнять с помощью оптронной пары VD3

![]() VD4 (рис. 1.43)(пунктиром).

VD4 (рис. 1.43)(пунктиром).