- •21. Элементы эмиттерно-функциональной логики (эфл).

- •22. Элементы мало сигнальной эмиттерно-связанной логики (мэсл).

- •23. Особенности применения элементов эсл. Реализация монтажных логических операций.

- •24. Элементы инжекционной интегральной логики. Статические характеристики (и2л).

- •Статические характеристики.

- •25. Элементы инжекционной интегральной логики. Динамические арактеристики.

- •28. Типовые элементы мдп – логики. Статические характеристики.

- •29. Типовые элементы кмдп логики. Динамические характеристики.

- •30. Разновидности элементов мдп – логики и принцип их работы.

- •31. Типовой элемент кмдп – логики. Статические характеристики.

- •32. Типовые элементы кмдп – логики. Динамические характеристики.

- •33. Особенности построения, элементарная база и структура бис (сбис).

- •34.Общая структура бис, входные и выходные транзисторы.

- •35. Преобразователи уровней цифровых имс. Общие сведения.

- •36. Преобразование уровней ттл к мдп и обратно.

- •37. Преобразователи уровней ттл, эсл и обратно.

- •38. Преобразователи уровней ттл, и2л и обратно.

- •39. Преобразователи уровней ттл, кмдп и обратно.

23. Особенности применения элементов эсл. Реализация монтажных логических операций.

Рассмотрим особенности применения микросхем ЭСЛ на примере серии 100. Схемы ЭСЛ имеют отрицательное напряжение источника питания Uип= -5,2 В 5%, и как следствие, отрицательное напряжение логических уровней. Кроме того, логические уровни схем ЭСЛ малы по абсолютному значению U1вых= -1 В и U0вых= -1,65 В. Все это не позволяет непосредственно соединять входы и выходы микросхем ЭСЛ с микросхемами ТТЛ или МОП- структур. Для взаимной стыковки схем с различными по величине логическими уровнями на выходе следует применять специальные схемы преобразователей 100ПУ124, 100ПУ125.

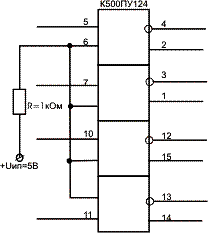

Неиспользованные входы микросхем 100ЛП115, 100ЛП116 должны быть подключены к источнику опорного напряжения (вывод 9- 100ЛП115 и вывод 11- 100ЛП116 ) или к напряжению источника питания Uип =-5,2 В 5%. Неиспользованные входы микросхемы 100 ПУ124 (рис.1.26) подключают к источнику питания Uип = 5,0 В; через резистор с номиналом 1 кОм. К одному резистору допускается подключение не более 20 неиспользованных входов.

Рис.1.26

Рассмотрение микросхемы ЭСЛ допускается

объединение их по прямым и инверсным

выходам в монтажное ИЛИ или монтажное

И с коэффициентом объединения Коб.вых

![]() 4,

а также объединение прямого выхода с

инверсии (рис.1.27).

4,

а также объединение прямого выхода с

инверсии (рис.1.27).

При увеличении числа объединений по выходу изменяется уровни выходного напряжения, что приводит к снижению помехоустойчивости микросхем. В схемах объединенных в монтажное ИЛИ, при переключении хотя бы одной микросхемы из состояния «1» в состояние «0» на выходе объединенных схем появляется отрицательная помеха, которая может вызвать ложное срабатывание элемента нагрузки. Амплитуда и длительность помехи зависят от длины линии связи, соединяющей элементы в монтажное ИЛИ. Рекомендуется объединение схем по выходам производить в пределах одной платы и по возможности для микросхем, расположенных рядом. Выход с платы с установленными на ней микросхемами рекомендуется брать от схемы, не имеющей объединений по выходу в пределах платы.

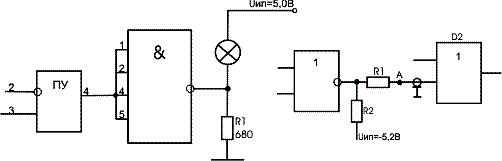

Совместное использование микросхем ЭСЛ и ТТЛ (рис.1.27) позволяет строить узлы специального назначения. На рис.1.27,а приведена схема индикации на микросхемах 100ПУ125 (D1) (серии ЭСЛ) и 133ЛА7 (D2) (серии ТТЛ).

а) б)

Рис.1.27 Схема, реализации способа согласования линии связи.

На рис.1.27,б приведена, схема реализации

последовательного способа согласования

линии связи. Для линии связи с волновым

сопротивлением

![]() Ом применяются резисторы с номиналами

R1 = 43 Ом и R2

= 240 Ом. При R1 = 51

Ом при параллельном согласовании

(рис.1.27,в).

Ом применяются резисторы с номиналами

R1 = 43 Ом и R2

= 240 Ом. При R1 = 51

Ом при параллельном согласовании

(рис.1.27,в).

Рис.1.27 в)

24. Элементы инжекционной интегральной логики. Статические характеристики (и2л).

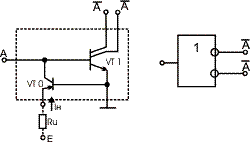

Элементы этого типа представляют собой физически объединенные (совмещение) горизонтальные p-n-p и вертикальные n-p-n – транзисторы (рис.1.28).

а) б)

Рис.1.28 Эквивалентная схема (а), условное обозначение (б) элемента И2Л.

Эмиттерная область p-n-p

–транзистора, называемая инжектором,

подключается к положительному источнику

питания. Общая область n-типа

служит базой p-n-h

–транзистора и эмиттером n-p-n

–транзистора и подключатся к потенциалу

«земля». Коллектор p-n-p

и база n-p-n

–транзистора также представляет собой

единую область полупроводника p-типа.

От одного инжектора может питаться

несколько схем, т.е. горизонтальный

p-n-p

– транзистор VT0 может

быть много коллекторным. Вертикальный

n-p-n

– транзистор обычно имеет несколько

коллекторов, которые являются логическими

выходами элемента (рис.1.28). При такой

физической структуре не требуется

изоляция между отдельными элементами

И2Л, так как все они имеют общую

n- область. Горизонтальный

p-n-p

– транзистор VT0 (рис.1.28)

служит в схемах И2Л источником

рабочего (переключаемого) тока Ip,

пропорционального коэффициенту передачи

тока

![]() транзистора VT0 .

транзистора VT0 .

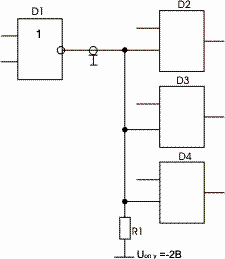

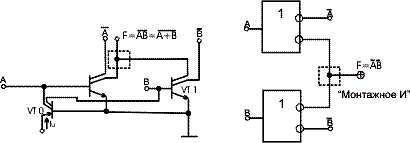

Типовой элемент И2Л представляет собой много выходной инверторов металлическими проводниками реализуется функция И (рис.1.29,а). На соединенных выходах F элементов в этом случае поддерживается низкий потенциал U0 , если высокий потенциал U1 подан хотя бы на один из входов (А или В). В результате выполняется коньюкция инверсных переменных А и В, которые образуются на выходах инверторов: F=АВ.

Рис.1.29 Реализация операции « Монтажное И».

Таким образом, если в схемах ТТЛ или ДТЛ операции И выполняются с помощью МЭТ или диодной сборки, то в схемах И2Л эта операция выполняется монтажным соединением. Используя элементы И2Л с монтажным соединением выходов, можно реализовать любую логическую функцию.