Рабочий стол / Alaev_A_N (1) / Алаев А.Н / DIGITAL_Konsp

.pdf

|

|

|

|

|

|

|

121 |

|

|

|

|

|

|

- вход разрешения считывания |

|

- |

OE |

данных, |

|||||

|

|

|

|

- вход выбора микросхемы, |

|

||

- |

|

CS |

|

||||

- |

|

- вход разрешения записи, |

|

||||

WE |

|

||||||

- D0...Dk - вход/выход данных. |

|

||||||

EO, DI, WR – внутренние сигналы, вырабатываемые блоком управления. Доступ к ЯП матрицы накопителя осуществляется с помощью двух дешифратор адреса столбцов и строк.

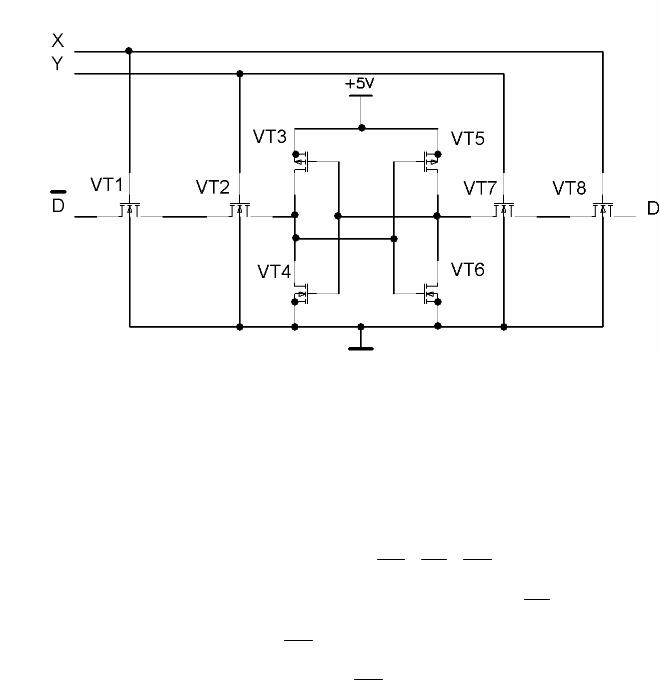

Упрощенная структурная схема элемента ЯП представлена на рис. 57.

Рис. 57. Упрощенная структурная схема элемента ЯП статического ОЗУ Комплементарные транзисторы VT3…VT6 образуют триггер. Последовательно включенные транзисторы VT1, VT2 и VT7, VT8 образуют элементы И. В случае, если данная ячейка не выбрана (на обеих шинах X и Y или на одной из них установлен низкий уровень), ЯП находится в режиме хранения информации. При одновременном появлении высокого уровня на обеих шинах X и Y данная ячейка оказывается

выбранной и в зависимости от состояния входов OE , CS , WE производится запись или считывание лог. состояния ячейки. В частности, если сигналы CS (chip select) –

выбор микросхемы низкого уровня , OE (output enabled) или RD (read data) –

переключения вход\выход - высокого уровня, WE (written enabled) или WR (written read) – разрешения записи низкого уровня, логический уровень, установленный на

информационном входе D микросхемы |

122 |

через специальные внутренние буферные |

усилители записи блока управления поступает на входы\выходы D, D элемента ЯП.

При этом, если состояние триггера элемента ЯП не соответствует приходящим сигналам, на его плечах на короткое время устанавливается напряжение равное примерно половине напряжения питания, что не достаточно для поддержания нижнего транзистора одного из плеч в открытом состоянии, этот транзистор закрывается и триггер устанавливается в состояние соответствующее приходящим сигналам.

В случае необходимости считывания информации сигнал OE устанавливается низкого

уровня, а сигнал WE - высокого уровня. При этом внутренние буферные усилители выходных сигналов внутри блока из третьего состояния переходят в активное

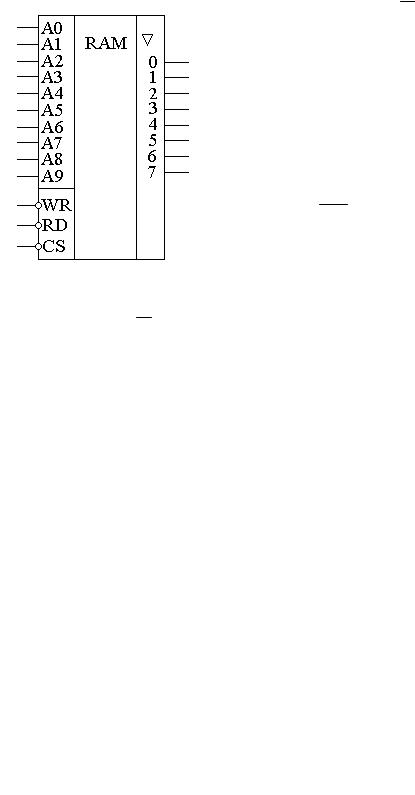

состояние, а к входам\выходам D, D элемента ЯП подключаются входы этих усилителей. Выходы внутренних буферных усилителей записи находятся при этом в третьем состоянии. И состояние триггера элемента ЯП передается на соответствующий вывод D микросхемы. В одной ЯП содержится k таких элементов. Пример условного обозначения ОЗУ на схемах электрических принципиальных приведен на рис. 58.

Рис. 58. Пример условного обозначения ОЗУ статического типа

Статические ОЗУ требуют для своего построения большой площади кристалла, поэтому их ёмкость относительно невелика. Статические ОЗУ применяются для построения микроконтроллерных схем из-за простоты построения принципиальной схемы и возможности работать на сколь угодно низких частотах, вплоть до

123

постоянного тока. Кроме того, они применяются для построения КЭШпамяти в универсальных компьютерах из-за высокого быстродействия статического ОЗУ.

4.2. Динамические ОЗУ

Статические оперативные запоминающие устройства позволяют обеспечивать хранение записанной информации до тех пор, пока на микросхему подаётся питание. Однако запоминающая ячейка статического ОЗУ занимает относительно большую площадь, поэтому для реализации ОЗУ большого объема были разработаны устройства, где в качестве запоминающей ячейки применяют конденсатор. Заряд на этой ёмкости естественно с течением времени уменьшается, поэтому его необходимо подзаряжать с периодом приблизительно 10 мс. Этот период называется периодом регенерации. Подзарядка ёмкости производится при считывании ячейки памяти, поэтому для регенерации информации достаточно просто считать регенерируемую ячейку памяти. Динамические ОЗУ характеризуются наибольшей информационной емкостью, немного меньшим быстродействием и повышенным энергопотреблением.

Схема запоминающего элемента динамического ОЗУ и его конструкция приведена на рис. 59.

Рис. 59. Схема запоминающего элемента динамического ОЗУ и его конструкция.

При считывании заряда ёмкости необходимо учитывать, что ёмкость линии считывания много больше емкости запоминающей ячейки. Графики изменения напряжения на линии считывания при считывании информации с запоминающей ячейки без применения регенерации приведены на рис. 60.

124

Рис. 60. Графики изменения напряжения на линии считывания при считывании информации с запоминающей ячейки.

Первоначально на линии записи/считывания присутствует половина питания микросхемы. При подключении к линии записи/считывания запоминающей ячейки заряд, хранящийся в запоминающей ячейке, изменяет напряжение на линии на небольшую величину ∆U. Теперь это напряжение необходимо восстановить до первоначального логического уровня. Если приращение напряжения ∆U было положительным, то напряжение необходимо довести до напряжения питания микросхемы. Если приращение ∆U было отрицательным, то напряжение необходимо довести до уровня общего провода.

Для регенерации первоначального напряжения, хранившегося в запоминающей ячейке в схеме применяется RS триггер, включенный между двумя линиями записи/считывания. Схема такого включения приведена на рис.61. Эта схема за счет положительной обратной связи восстанавливает первоначальное значение напряжения в запоминающем элементе, подключенном к выбранной линии считывания. То есть, при считывании ячейки производится регенерация хранящегося в ней заряда.

Рис. 61. Схема регенерирующего каскада.

|

125 |

Для уменьшения времени регенерации |

микросхема устроена так, что при |

считывании одной ячейки памяти в строке накопительной матрицы регенерируется вся строка.

Особенностью динамических ОЗУ является мультиплексирование шины адреса. Адрес строки и адрес столбца передаются поочередно. Адрес строки синхронизируется стробирующим сигналом RAS# (Row Address strobe), а адрес столбца - CAS# (Column Adress Strobe). Мультиплексирование адресов позволяет уменьшить количество выводов микросхем ОЗУ. Изображение микросхемы динамического ОЗУ приведено на рис. 62, а временные диаграммы обращения к динамическому ОЗУ на рис. 63.

Рис. 62. Изображение динамического ОЗУ на принципиальных схемах.

Рис. 63. Временная диаграмма обращения к динамическому ОЗУ На рис. 63 стрелками показана последовательность, в которой должны формироваться управляющие сигналы.

|

126 |

Именно так долгое время велась работа с |

динамическими ОЗУ. Затем было |

замечено, что обычно обращение ведется к данным, лежащим в соседних ячейках памяти, поэтому не обязательно при считывании или записи каждый раз передавать адрес строки. Данные стали записывать или считывать блоками и адрес строки передавать только в начале блока. При этом можно сократить общее время обращения к динамическому ОЗУ и тем самым увеличить быстродействие компьютера.

Такой режим обращения к динамическому ОЗУ называется быстрым страничным режимом доступа FPM (Fast Page Mode). Длина считываемого блока данных равна четырем словам. Для того чтобы оценить время такого режима доступа к памяти время измеряют в тактах системной шины процессора. В обычном режиме доступа к памяти время доступа одинаково для всех слов и составляет пять тактов. Поэтому цикл обращения к динамической памяти можно записать как 5-5-5-5. При режиме быстрого страничного доступа цикл обращения к динамической памяти можно записать как 5-3- 3-3, то есть время обращения к первой ячейке не изменяется по сравнению с предыдущим случаем, а считывание последующих ячеек сокращается до трех тактов. При этом среднее время доступа к памяти сокращается почти в полтора раза. Временная диаграмма режима FPM приведена на рис. 64.

Рис. 64. Временная диаграмма обращения к динамическому ОЗУ в режиме FPM.

Еще одним способом увеличения быстродействия ОЗУ является применение микросхем EDO (Extended Data Out — ОЗУ с расширенным выходом данных). В EDO ОЗУ усилители-регенераторы не сбрасываются по окончанию строба CAS#, поэтому

|

127 |

времени для считывания данных в таком |

режиме больше. Теперь для того чтобы |

сохранить время считывания на прежнем уровне можно увеличить тактовую частоту системной шины и тем самым увеличить быстродействие компьютера. Для EDO ОЗУ цикл обращения к динамической памяти можно записать как 5-2-2-2.

Следующим шагом в развитии схем динамического ОЗУ было применение в составе ОЗУ счетчика столбцов. То есть при переходе адреса ячейки к следующему столбцу запоминающей матрицы адрес столбца инкрементируется (увеличивается)

автоматически. Такое ОЗУ получило название BEDO (ОЗУ с пакетным доступом). В этом типе ОЗУ удалось достигнуть режима обращения к динамической памяти 5-1-1-1.

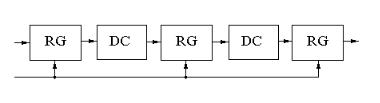

В синхронном динамическом ОЗУ (SDRAM) дальнейшее увеличение быстродействия получается за счет применения конвейерной обработки сигнала. Как известно при использовании конвейера можно разделить операцию считывания или записи на отдельные подоперации, такие как выборка строк, выборка столбцов, считывание ячеек памяти, и производить эти операции одновременно. При этом пока на выход передается считанная ранее информация, производится дешифрация столбца для текущей ячейки памяти и производится дешифрация строки для следующей ячейки памяти. Этот процесс иллюстрируется рис. 65.

Рис. 65. Структурная схема конвейерной обработки данных.

Из приведенного рисунка видно что, несмотря на то, что при считывании одной ячейки памяти время доступа к ОЗУ увеличивается, при считывании нескольких соседних ячеек памяти общее быстродействие микросхем синхронного динамического ОЗУ увеличивается.

|

128 |

4.3. Однократно программируемые |

постоянные запоминающие устройства |

В качестве элементов памяти ППЗУ имеют нaбop плавкиx пepeмычeк, кoтopыe в пpoцecce пpoгpaммиpoвaния пepeжигaютcя импyльcaми тoкa. Ha рис. 66 приведена cxeмa типового ППЗУ.

Рис.66. Типовая схема организации ППЗУ

Для любого значения aдpecныx сигнaлoв An-1,An-2,...,A1,A0(BIN) =i(DEC),

нaйдeтcя eдинcтвeнный выxoд дeшифpaтopa "i" на кoтopoм cигнaл Yi= 1, на ocтaльныx выxoдax бyдyт нули. Потенциал j-столбца будeт зaвиceть в этом cлyчae тoлькo от наличия или oтcyтcтвия пepeмычки fi. Если пepeмычкa есть (fi=1), то на столбце считывания выcoкий ypoвeнь cигнaлa, тpaнзиcтop усилителя oткpыт и выxoднoй cигнaл D0 j = 0. Если перемычки нет (fi=0), то D0 j =1. Пережиганием

перемычек в соответствующих j-битax вcex aдpecoв, в микpocxeмy записывается пpoгpaммa и/или данныe. Выходной сигнал дeшифpaтopa Yi = mi, где mi-минтepм

|

|

2n −1 |

n−1 |

входныx пepeмeнныx A0..An-1. Таким образом: |

DO j |

= ∑ fi mi , где mi = Λ/ Ak , |

|

|

|

i=0 |

k =0 |

причем / Ak = Ak , если Ak во входном нaбope paвнa 0 и / Ak = Ak , ecли Ak =1. Эти формулы соответствуют формулам СДНФ, поэтому c помощью ПЗУ c

n - адресными входами и m - выходами можно реализовать любые

|

129 |

m- логических функций c n - |

переменными (учитывая инверсию |

сигнала выходным каскадом). |

|

В масочных ЗУ элементами связи могут быть диоды, биполярные транзисторы, МОП - транзисторы. Программируются с помощью одной из масок при изготовлении ЗУ. На рис. 67 приведена упрощенная схема ЯП диодного масочного ЗУ.

Рис. 67. Упрощенная схема ЯП диодного масочного ПЗУ

При наличии диода высокий потенциал выбранной горизонтальной линии передается на соответствующую вертикальную линию и в данном разряде появляется «1». При возбуждении (высокий потенциал) линии А1 считывается слово 11010001. При возбуждении А2 считывается слово 10101011. Линии выборки слов А1…Aj являются выходами дешифратора адреса.

При выполнении матрицы на МОП транзисторах их истоки подключаются к нулевому проводу, на стоки подается питание, а затворы всех транзисторов слова подключаются к линиям выборки слов А. В МОП-транзисторах, соответствующих хранению нуля, увеличивают толщину подзатворного окисла, что ведет к увеличению порогового напряжения транзистора. В этом случае рабочие напряжения не могут открыть транзистор, что соответствует его отсутствию.

Масочные ЗУ отличаются высоким уровнем интеграции.

Область применения: хранение стандартной информации, имеющей широкий круг потребителей. Это прошивка кодов букв русского и латинского алфавита, таблицы типовых функций (sin, квадратичной функции и др.), стандартное программное обеспечение и т.п.

|

130 |

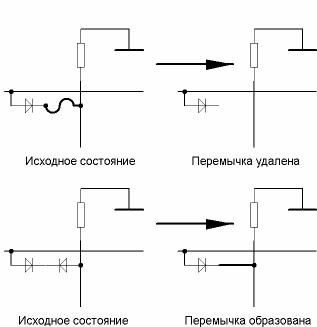

ЗУ типа PROM программируются |

пользователем устранением или |

созданием перемычек (рис. 68). |

|

Рис. 68. Схема ЯП ПЗУ программируемых пользователем В исходном состоянии ЗУ имеет все перемычки, а при

программировании часть их ликвидируется путем расплавления импульсами тока (большой амплитуды и длительности). Эти перемычки включаются в электроды диодов или транзисторов. Изготавливаются металлическими (нихром) и поликристаллическими (кремниевыми).

Другой тип перемычки: два встречно включенных диода. В исходном состоянии цепь можно считать разомкнутой. Для записи «1» к диодам прикладывается высокое напряжение, пробивающее диод, смещенный в обратном направлении. Диод пробивается с образованием в нем короткого замыкания.

Выпускаемые также схемы с тонкими пробиваемыми диэлектрическими перемычками (типа antifuze) более компактны и совершенны. Применяются в ПЛИС. Представителем ЗУ с плавкими перемычками является м/сх К155РЕЗ (ТТЛ).

Плавкие перемычки занимают довольно много места, поэтому уровень (степень) интеграции ниже, чем у масочных ЗУ. Однако имеют невысокую стоимость, т.к. изготовитель выпускает микросхему без учета конкретного содержимого ЗУ. Программирует ЗУ пользователь.