Рабочий стол / Alaev_A_N (1) / Алаев А.Н / DIGITAL_Konsp

.pdf111 |

|

|

позволяют вести подсчет электрических импульсов, |

количество |

которых |

(поступивших на вход счетчика) представляется, обычно, в параллельном коде. Счетчики могут отличаться модулем счета и типом счетной последовательности, которая, в частности, может быть двоичной, двоично-десятичной, в коде Грея и т.п. Цифровые последовательностные устройства, выполненные по схеме счетчика, но имеющие один счетный вход и один выход называются делителями частоты. Таким образом, любой счетчик может служить в качестве делителя частоты, если используется информация только одного из его выходов. Счетчики и делители имеют одинаковую структуру.

Счетчики и делители подразделяются на асинхронные и синхронные. У синхронных счетчиков все разрядные триггеры синхронизируются параллельно одними и теми же синхроимпульсами, поступающими из источника этих импульсов. Асинхронные счетчики имеют последовательную синхронизацию, т.е. каждый последующий разрядный триггер синхронизируется выходными импульсами триггера предыдущего разряда. Асинхронные счетчики иногда называют последовательными или счетчиками домино, а синхронные счетчики - параллельными.

Синхронные счетчики, в свою очередь, подразделяются на параллельносинхронные и последовательно-синхронные. Параллельные счетчики имеют более высокую скорость счета, чем асинхронные к тому же у них отсутствует эффект «гонок».

Счетчики, независимо от способа синхронизации, подразделяются на счетчики прямого счета (суммирующие) и на счетчики обратного счета (вычитающие). В интегральном исполнении выпускаются также реверсивные счетчики, в которых имеется специальный вход для переключения режима работы, т.е. направления счета. Многие типы счетчиков, выпускаемые промышленностью в интегральном исполнении, имеют дополнительные входы предустановки, позволяющие использовать эти счетчики в режиме регистра памяти.

В качестве разрядных триггеров счетчиков и делителей могут быть использованы двухступенчатые D-триггеры, Т- и JK-триггеры.

Счетчики относятся к последовательностным устройствам с циклически повторяющейся последовательностью состояний. Число, соответствующее количеству импульсов (поступивших на вход счетчика), при котором счетчик “возвращается” в

112

исходное состояние, называется модулем или коэффициентом счета. Модуль счета, обычно, обозначают буквой М (или Ксч). Например, максимальный модуль счета счетчика из двух триггеров равен М = 22 = 4, трех триггеров - М = 23 = 8 и т.д. В общем случае для n - разрядного счетчика - М = 2n. Модуль счета счетчика численно совпадает с модулем деления делителя частоты. Счетчик по модулю 8 позволяет реализовать (без дополнительных схемных затрат) делитель частоты на 8. Это значит, что данный делитель делит частоту входной импульсной последовательности на 8.

Асинхронный двоичный счетчик. Асинхронный двоичный счетчик представляет собой совокупность последовательно соединенных триггеров (D - или JK), каждый из которых ассоциируется с битом в двоичном представлении числа. Если в счетчике m триггеров, то число возможных состояний счетчика равно 2m, и, следовательно, модуль счета М также равен 2m. Счетная последовательность в двоичном суммирующем счетчике начинается с нуля и доходит до максимального числа 2m - 1, после чего снова проходит через нуль и повторяется. В вычитающем двоичном счетчике последовательные двоичные числа перебираются в обратном порядке, и при повторении последовательности максимальное число следует за нулем.

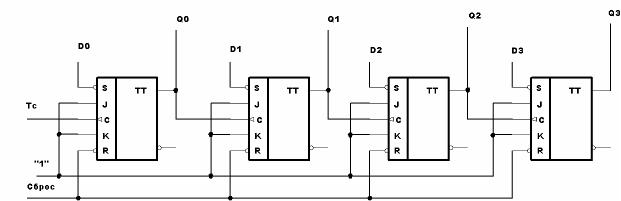

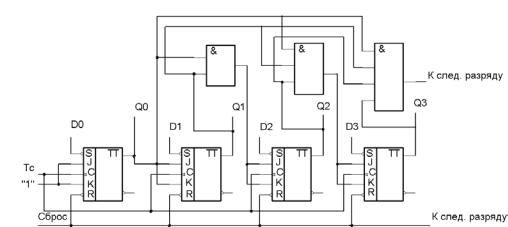

Рассмотрим устройство двоичного суммирующего счетчика по модулю М=16, выполненного на базе JK-триггеров (рис. 49).

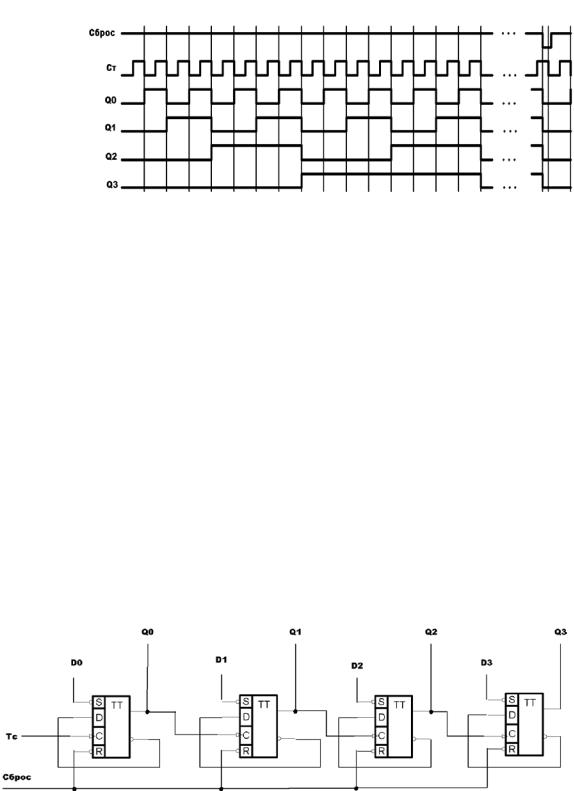

Рис. 49. Асинхронный суммирующий двоичный счетчик Как видно из рис. 49, синхронизирующие входы всех триггеров, кроме крайнего

левого, соединены с выходами предыдущих триггеров. Поэтому состояние триггера меняется в ответ на изменение состояния предыдущего триггера. Временная диаграмма работы этого счетчика при подаче на его вход логического сигнала в виде периодической последовательности «0» и «1» представлена на рис. 50.

113

Рис. 50. Временные диаграммы работы асинхронного двоичного счетчика.

Из рис. 50 легко заметить, что значение разряда в выбранной позиции меняется тогда, когда сигнал Ст переходит из “1” в “0”, управление триггерами осуществляется срезом синхроимпульсов (отрицательным перепадом напряжения импульса синхронизации). При поступлении лог. «0» на вход сброса все разряды счетчика также устанавливаются в «0» не зависимо от состояния входа Ст. Это устройство имеет, также, возможность предварительной установки по входам D0…D3. Причем перед подачей сигналов записи на D0…D3 все разряды счетчика должны быть сброшены в «0». Возможна реализация такого счетчика и на D – триггерах (при включении Т – триггером), при этом счетчик меняет свое состояние по фронту сигнала Ст.

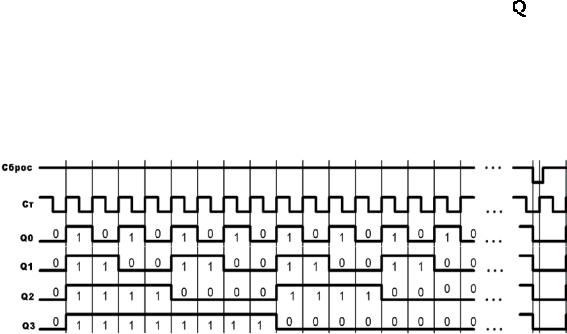

Счетчики обратного счета (вычитающие счетчики). На рис. 51 приведена схема асинхронного четырехразрядного двоичного вычитающего счетчика, построенного на базе D-триггеров.

Рис. 51. Асинхронный вычитающий двоичный счетчик Отметим, что условия для изменения состояний триггеров вычитающих

счетчиков аналогичны условиям для суммирующих счетчиков с той лишь разницей, что они должны “опираться” на значения инверсных, а не прямых выходов триггеров. Следовательно, рассмотренный выше счетчик можно превратить в вычитающий,

114 |

|

|

|

|

просто переключив входы “С” триггеров с выходов Q на выходы |

|

|

|

. Когда в |

|

|

|

качестве разрядных триггеров используются D-триггеры, синхронизируемые фронтом синхросигнала, для получения вычитающего счетчика (асинхронного) входы “С” последующих триггеров соединяются с прямыми выходами предыдущих, также как в счетчике прямого счета, построенного на JK-триггерах.

Рис. 52. Временные диаграммы работы вычитающего счетчика

Работа вычитающего счетчика на D-триггерах иллюстрирована на рис. 52. Из рис. 52 следует, что после нулевого состояния всех триггеров, с приходом первого синхроимпульса они устанавливаются в состояние “1”. Поступление второго синхроимпульса приводит к уменьшению этого числа на одну единицу и т.д. После поступления шестнадцатого импульса, снова все триггеры обнуляются, и цикл счета повторяется, что соответствует модулю М=16.

В некоторых случаях необходимо, чтобы счетчик мог работать как в прямом, так и в обратном направлении счета. Такие счетчики называются реверсивными. Реверсивные счетчики могут быть как асинхронного, так и синхронного типа. Они строятся путем применения логических коммутаторов (мультиплексоров) в цепях связи между триггерами. Так, например, асинхронный реверсивный двоичный счетчик можно построить, если обеспечить подачу сигналов с прямого (при суммировании) или с инверсного (при вычитании) выхода предыдущего JK- или T-триггера на счетный вход последующего. В случае, когда реверсивный счетчик строится на базе D-триггеров, управляемых передним фронтом, для получения режима прямого счета следует соединить инверсный выход предыдущего со счетным входом последующего триггера.

Все рассмотренные типы счетчиков могут быть использованы в цифровых устройствах, где различная задержка установки разрядов не играет значения. Подключение к выходам таких счетчиков последовательностных устройств может

115 |

|

|

приводить в некоторых случаях к сбоям последних |

вследствие |

проявления |

эффекта «гонок». Поэтому были разработаны синхронные счетчики.

Параллельные счетчики (синхронные счетчики). Как было уже сказано выше, параллельные счетчики бывают двух типов: синхронные параллельные и синхронные последовательные.

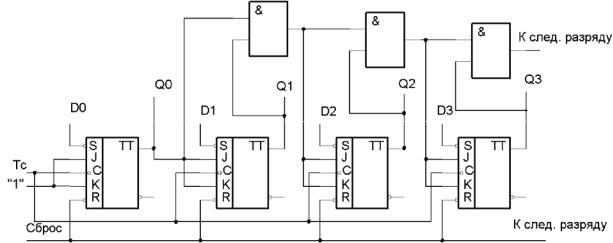

Последовательный синхронный счетчик. По способу подачи синхроимпульсов такие счетчики параллельные, т.е. синхроимпульсы поступают на все триггеры счетчика параллельно, а по способу управления (подачи управляющих импульсов) - последовательные. Схема последовательного синхронного счетчика, реализованного на JK-триггерах, приведена на рис. 53.

Рис. 53. Последовательный синхронный суммирующий счетчик на JKтриггерах Последовательный синхронный счетчик обладает повышенным быстродействием, однако, за счет последовательного формирования управляющих уровней, на входы “J” и “К” счетных триггеров, быстродействие несколько уменьшается. От этого недостатка лишены параллельные синхронные счетчики, в которых формирование управляющих уровней и их подача на соответствующие входы триггеров счетчика осуществляется одновременно, т.е. параллельно. Пример

реализации параллельного синхронного счетчика иллюстрирован рис. 54.

116

Рис. 54. Синхронный параллельный суммирующий счетчик Отличие от предыдущего заключается в том, что перенос в следующий разряд

формируется не последовательно включенными двухвходовыми элементами И, а для каждого разряда служит свой элемент, на входы которого поданы сигналы с предыдущих разрядов. Причем число входов элемента увеличивается с увеличением старшинства и числа разрядов. Поскольку триггеры меняют свое состояние синхронно, сигналы на всех входах схем переноса появляются одновременно и эффект гонок отсутствует. Счетчики с параллельным переносом по-сравнению с предыдущими имеют более высокое быстродействие.

Счетчики с произвольным коэффициентом счета. Принцип построения подобного класса счетных устройств состоит в исключении нескольких состояний обычного двоичного счетчика, являющихся избыточными для счетчиков с коэффициентом пересчета, отличающимися от двоичных. При этом избыточные состояния исключаются с помощью обратных связей внутри счетчика.

Число избыточных состояний для любого счетчика определяется из следующего выражения:

М = 2m - Ксч ,

где М - число запрещенных состояний, Ксч - требуемый коэффициент счета; 2m - число устойчивых состояний двоичного счетчика.

Задача синтеза счетчика с произвольным коэффициентом счета заключается в определении необходимых обратных связей и минимизации их числа. Требуемое количество триггеров определяется из выражения:

n= [log2 Ксч],

117

где [log2 Ксч] - двоичный логарифм заданного коэффициента пересчета Ксч, округленный до ближайшего целого числа.

В каждом отдельном случае приходится применять какие-то конкретные методы получения требуемого коэффициента пересчета. Существует несколько методов получения счетчиков с заданным коэффициентом пересчета Ксч. Один их этих методов заключается в немедленном сбросе в “0” счетчика, установившегося в комбинацию, соответствующему числу Ксч. Его называют также методом автосброса. Рассмотрим пример реализации счетчика с Ксч=10 методом автосброса. Очевидно, что “сбрасывая” двоичный четырехразрядный счетчик на нуль каждый раз, когда он будет принимать состояние 1010, можно обеспечить «возврат” счетчика в исходное состояние после каждых десяти импульсов. Подобный прием удобно применять при использовании счетчиков в интегральном исполнении, имеющих встроенные элементы И на входах установки в нуль, как это сделано в микросхеме К1533ИЕ5. В данном примере (рис. 55) соединения обеспечивают коэффициент пересчета Ксч =10.

Рис. 55. Пример реализации счетчика с произвольным коэффициентом пересчета,

отличным от 2m

Как следует из рис. 55, роль ячейки, выявляющей факт достижения кодовой комбинации 1010 на выходах счетчика, играет ячейка И, уже имеющаяся в микросхеме К1533ИЕ5.

В таблице 3.4 поясняются конфигурации соединений для получения различных коэффициентов пересчета с помощью счетчика К1533ИЕ5. Наиболее очевидные

118

варианты получения коэффициентов (2, 4, 8, 16) в таблице не указаны. В графе “Соединения” таблицы указано, какие выводы микросхемы должны быть соединены между собой: например, указание 1-12 означает, что нужно соединить вывод 1 с выводом 12. В строках “Ввод” и “Выход” таблицы указаны номера выводов микросхемы, на которые следует подавать входные импульсы и с которых надлежит снимать выходные, соответственно. Следует отметить, что К1533ИЕ5 состоит из четырех счетных триггеров, один из которых имеет раздельные выводы входа и выхода, а остальные три триггера соединены последовательно по схеме асинхронного счетчика, поэтому здесь возможно проявление эффекта «гонок» для некоторых коэффициентов пересчета, что требует усложнения схемы автосброса.

Счетчики с переменным коэффициентом счета имеют очень широкое применение в радиотехнике при реализации делителей частоты с переменным коэффициентом деления, при реализации различных программируемых таймеров. В основном при реализации таких устройств используются синхронные параллельные счетчики с синхронными схемами предустановки (сброса).

4. Полупроводниковые запоминающие устройства

Микросхемы памяти в общем объеме выпуска ИС занимают около 40%.

В последовательностных цифровых автоматах для хранения небольших кодовых слов используются регистры, описанные ранее. Причем при отключении питания информация стирается. При необходимости хранения больших объемов информации применяют запоминающие устройства (ЗУ), выполненные на специализированных микросхемах. Существуют микросхемы, позволяющие долгое время хранить информацию даже при отключенном питании.

По выполняемой функции ЗУ можно разделить на оперативные запоминающие устройства (ОЗУ), обозначаемые RAM (random access memory) и постоянные запоминающие устройства (ПЗУ), обозначаемые ROM (read only memory).

К оперативным относят ЗУ, которые используются для хранения информации, необходимой в процессе работы автомата. ОЗУ могут быть выполнены как статическими, так и динамическими. В статических ОЗУ записанная информация постоянно сохраняется в выделенном месте и не стирается при ее считывании. Стирание возможно только специальным сигналом или при отключении питания.

|

119 |

В динамических ОЗУ информация |

постоянно перезаписывается и при |

считывании стирается, поэтому для ее сохранения необходима постоянная перезапись. Для обозначения ОЗУ на принципиальных электрических схемах используется аббревиатура RAM (random access memory). В свою очередь ОЗУ делятся на статические (SRAM), динамические (DRAM) и регистровые (RG). ПЗУ могут быть масочными – запрограммированными изготовителем (ROM), однократно программируемые пользователем (PROM или OTP), многократно программируемыми (репрограммируемыми) с ультрафиолетовым стиранием (EPROM) или с электрическим стиранием (EEPROM, Flash). Широкое применение нашли также логические матрицы и устройства (PLM, PML, PLA, PAL, PLD, FPGA и т. д.) с большим выбором различных конфигураций.

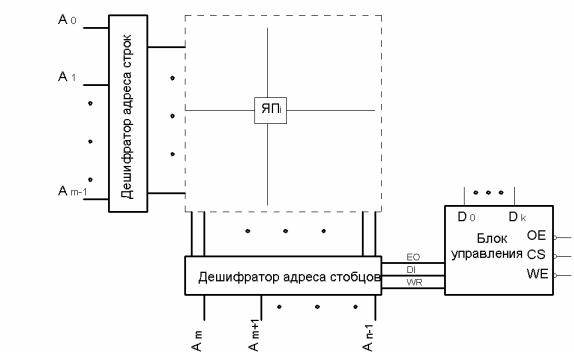

В зависимости от типа ЗУ элементом памяти может быть триггер, миниатюрный конденсатор, полевой транзистор с «плавающим» затвором, плавкая перемычка. Упорядоченный набор элементов памяти образует ячейку памяти (ЯП). Количество

элементов памяти в ЯП обычно кратно 2n . Обычно это количество называют длиной слова. В свою очередь ЯП группируются в матрицу памяти с упорядоченным доступом. Наиболее распространены три структуры доступа к ЯП: 2D, 3D, 2DM. Для ПЗУ и статических ОЗУ малой емкости применяется структура 2D, где в матрице памяти строками является адрес ЯП, а столбцами разряды слова данных. Т. е. активный сигнал в каждый момент времени может быть только в одной строке. Увеличение числа разрядов адреса ведет к значительному усложнению дешифратора. Поэтому для памяти с большим объемом применяются 3D структуры, где адресное слово делится на две (обычно равные) части, каждая часть дешифруется отдельно и из одной части образуются строки, а из другой столбцы матрицы. Считывание или запись информации в выбранную ЯП при этом происходит по отдельным шинам. Структура 2DM занимает промежуточное положение. При этом из части m разрядов адреса N

также формируются строки, и активируется одновременно 2N −m ЯП, а выбор соответствующей осуществляется с помощью дополнительного мультиплексора. Кроме адресного доступа существуют и другие:

-последовательные запоминающие устройства;

-ассоциативные запоминающие устройства.

Последовательные ЗУ делятся по способу считывания – записи информации:

|

120 |

- FIFO (first in – first out) первым пришел |

– первым вышел (очередь), |

-LIFO (last in - first out) последним пришел – первым вышел (стек), -файловые, где данные поступают в начало,

- циклические, где слова считываются одно за другим с определенным периодом. В ассоциативных ЗУ поиск информации производится по некоторым признакам, содержащихся в самих словах, а не по их координатам.

Основными характеристиками микросхемы памяти являются: информационная емкость (объем), быстродействие и энергопотребление. Емкость современных ЗУ чаще всего выражается в единицах кратных 210 = 1024 (один килобит), 220 = 1048576 (один мегабит) или 230 =1073741824 (один гигабит).

Для создания элементов ЗУ, в основном, применяют структуры МОП на основе кремния, что связано с технологичностью их изготовления.

4.1. Статические ОЗУ

Типичный вариант структурного построения микросхемы статического ОЗУ приведен на рис. 56.

Рис.56. Структурная схема статического ЗУ 3D.

На рис. 56 приняты следующие обозначения:

- A0 ...An−1 - n адресных входов,