Рабочий стол / Alaev_A_N (1) / Алаев А.Н / DIGITAL_Konsp

.pdf

|

91 |

Применяются также и неполные |

дешифраторы, например, для |

дешифрования тетрад двоично-десятичного кода, где число выходов равно десяти. Такое решение позволяет размещать устройства в корпусах с меньшим числом выводов.

Шифраторы выполняют функцию обратную дешифраторам. Различают неприоритетные и приоритетные шифраторы. Например, для неприоритетного шифратора 4 → 2 верна таблица истинности табл.. 3.3.

|

|

|

|

Таблица 3.3 |

|

||

|

|

|

|

|

|

|

|

№ |

X3 |

X2 |

X1 |

|

X0 |

Y1 |

Y0 |

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

|

|

|

|

|

|

|

|

2 |

0 |

0 |

1 |

|

0 |

0 |

1 |

|

|

|

|

|

|

|

|

3 |

0 |

1 |

0 |

|

0 |

1 |

0 |

|

|

|

|

|

|

|

|

4 |

1 |

0 |

0 |

|

0 |

1 |

1 |

|

|

|

|

|

|

|

|

При этом остальные комбинации Х0…Х3 запрещены.

В приоритетном шифраторе производится преобразование максимального десятичного номера в двоичный код:

|

|

|

|

Таблица 3.4 |

|

||

|

|

|

|

|

|

|

|

№ |

X3 |

X2 |

X1 |

|

X0 |

Y1 |

Y0 |

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

|

|

|

|

|

|

|

|

2 |

0 |

0 |

1 |

|

Х |

0 |

1 |

|

|

|

|

|

|

|

|

3 |

0 |

1 |

Х |

|

Х |

1 |

0 |

|

|

|

|

|

|

|

|

4 |

1 |

Х |

Х |

|

Х |

1 |

1 |

|

|

|

|

|

|

|

|

Знак Х в таблице 3.4 означает, что данная переменная может принимать как значение лог. «0» так и лог. «1».

Шифраторы применяются при формировании данных с клавиатур, в контроллерах прерывания микропроцессоров, параллельных аналого-цифровых преобразователях и т. п.

Пример условного обозначения приоритетного шифратора К155ИВ1 приведен на рис.26.

92

Рис. 26. Шифратор К155ИВ1.

В этой микросхеме кроме входа выбора ЕА имеются два выхода GS, E0, предназначенные для расширения шифратора на большее число разрядов. Сигнал лог. «0» на выходе GS появляется при одновременном наличии лог. «0» на входе ЕА и хотя бы на одном из входов А0…А7. Сигнал лог. «0» на выходе E0 появляется при одновременном наличии лог. «0» на входе ЕА и наличии лог. «1» на всех входах

А0…А7.

3.4.4. Преобразователи кодов

Преобразователи кодов могут быть весовыми и невесовыми. Весовые преобразуют информацию из одной системы счисления в другую. Основное назначение невесовых преобразователей – преобразование информации для ее дальнейшего отображения с помощью устройств индикации. В качестве примера рассмотрим преобразователь двоично-десятичного кода в код для отображения на семимисегментых светодиодных индикаторах (разд. 1.4.3) К155ПП5. Его обозначение на схеме электрической принципиальной представлено на рис. 27.

Рис. 27. Преобразователь в семи сегментный код К155КП5.

93

Работа этого устройства описывается следующей таблицей истинности:

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 3.4 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Десятичная |

1 |

2 |

4 |

8 |

E |

A |

B |

C |

D |

E |

F |

|

G |

|

цифра |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

x |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

0 |

0 |

0 |

x |

0 |

0 |

x |

x |

x |

|

x |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

x |

0 |

0 |

x |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

x |

x |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

0 |

0 |

1 |

0 |

0 |

x |

0 |

0 |

x |

x |

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5 |

1 |

0 |

1 |

0 |

0 |

0 |

x |

0 |

0 |

x |

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

0 |

1 |

1 |

0 |

0 |

0 |

x |

0 |

0 |

0 |

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

x |

x |

x |

|

x |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

x |

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

X |

X |

X |

1 |

x |

x |

x |

x |

x |

x |

|

x |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Здесь знаком «Х» обозначено, что переменная может принимать любое значение: как лог. «0», так и лог. «1». Знаком «х» обозначено, что выходы микросхемы переходят в состояние с высоким сопротивлением. Как видно из условного обозначения, выходные каскады микросхемы выполнены по схеме с «открытым коллектором», что позволяет соединять параллельно выходы нескольких микросхем в случаях, когда нужно преобразовывать данные от нескольких источников без применения специальных микросхем мультиплексоров. Пример использования К155ПП5 с семи сегментным светодиодным индикатором представлен на рис. 28.

94

Рис. 28. Пример использования микросхемы семисегментного преобразователя кода К155ПП5.

Резисторы R1…R7 предназначены для ограничения тока через сегменты светодиодного индикатора и выходные транзисторы преобразователя кода. Весовые преобразователи используются, например, для преобразования двоичного кода в двоично-десятичный (К155ПР7) и т. п. Хотя они и отличаются высоким быстродействием используются редко, т. к. существуют более простые схемные решения.

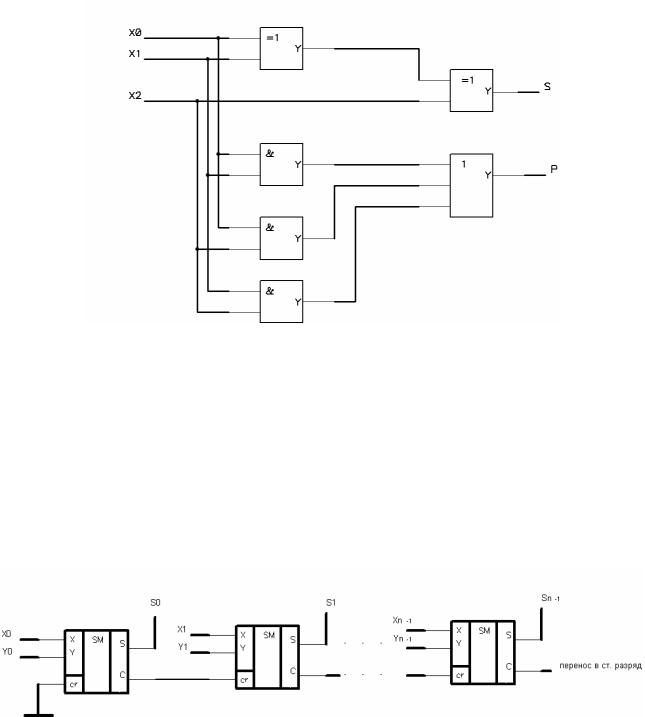

3.4.5. Сумматоры

Сумматором называется комбинационное логическое устройство, предназначенное для выполнения операции арифметического сложения чисел, представленных в виде двоичных кодов.

Сумматоры являются одним из основных узлов арифметико-логических устройств. Различают полусумматоры и полные сумматоры. Полусумматором называется устройство, предназначенное для сложения двух одно разрядных кодов, которое имеет два входа и два выхода и формирующее из двух входных сигналов сигнал суммы и сигнал переноса в старший разряд. Ниже представлена таблица истинности полусумматора:

|

|

95 |

|

|

|

|

|

Таблица 3.5 |

|

|

|

|

|

|

X1 |

X0 |

|

S |

P |

|

|

|

|

|

0 |

0 |

|

0 |

0 |

|

|

|

|

|

0 |

1 |

|

1 |

0 |

|

|

|

|

|

1 |

0 |

|

1 |

0 |

|

|

|

|

|

1 |

1 |

|

0 |

1 |

|

|

|

|

|

В таблице 3.5 S – выходной сигнал суммы, P – выходной сигнал переноса.

На основании таблицы 3.5 составлена система логических уравнений полусумматора:

S = X 0 X1 + X1 X 0 = X 0 X1. P = X 0 X1

Для технической реализации полусумматора необходимы логические элементы И и исключающее ИЛИ.

При построении много разрядных сумматоров необходим полный сумматор. От полусумматора он отличается наличием третьего логического входа для сигнала переноса. Его работа описывается таблицей 3.6:

Таблица 3.6

X2 |

X1 |

X0 |

S |

P |

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

0 |

0 |

1 |

1 |

0 |

|

|

|

|

|

0 |

1 |

0 |

1 |

0 |

|

|

|

|

|

0 |

1 |

1 |

0 |

1 |

|

|

|

|

|

1 |

0 |

0 |

1 |

0 |

|

|

|

|

|

1 |

0 |

1 |

0 |

1 |

|

|

|

|

|

1 |

1 |

0 |

0 |

1 |

|

|

|

|

|

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

или системой логических уравнений:

S = X 0 X1 X 2 + X 0 X1 X 2 + X 0 X1 X 2 + X 0 X1* X 2,

(31)

P = X 0 X1 + X 0 X 2 + X1 X 2.

Вход Х2 служит для подачи сигнала переноса из предыдущего разряда. Возможная схема одно разрядного полного сумматора приведена на рис. 29.

96

Рис. 29. Схема полного одноразрядного двоичного сумматора Сумматор для сложения n – разрядных двоичных чисел с последовательным переносом показан на рис. 30. Здесь “cr” обозначен вход переноса, а “C”- выход переноса. Основным недостатком много разрядных сумматоров, построенных по такой схеме, является большая задержка формирования переноса. Рассматривая схему рис. 29, можно заключить, что задержка переноса в одном разряде составляет 2tзад .

Рис. 30 Схема n-разрядного двоичного сумматора

Как видно из рис. 30 перенос распространяется последовательно по разрядам и общее время задержки составит: 2ntзад . При этом в процессе установления сигнала на выходах сумматора ярко выражен эффект «гонок».

Как было сказано в ЭВМ сумматоры являются одной из основных составляющих частей арифметико-логического устройства. Использование последовательной схемы переноса при сложении многоразрядных чисел приводит к возникновению недопустимо больших задержек и существенному снижению быстродействия ЭВМ.

97

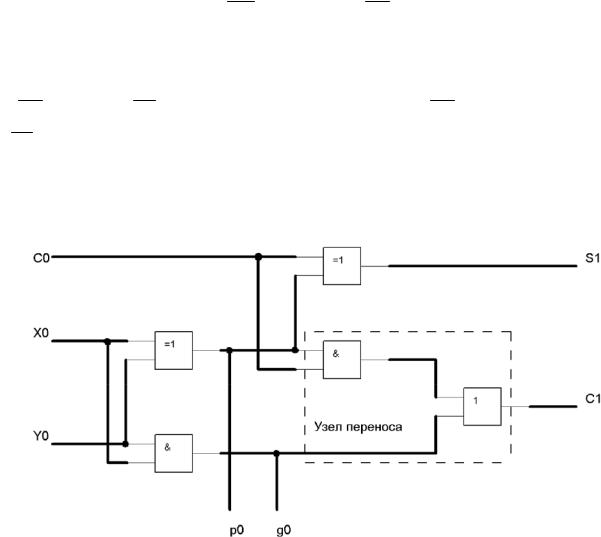

Поэтому были разработаны параллельные схемы формирования переноса.

Используя тождество X 0 + X1 = X 0 X1 + X 0 X1 + X 0 X1, выражение для переноса Р в (30) можно преобразовать к следующему виду:

P = X 0 X1+ X 0 X 2 + X1 X 2 = X 0 X1+ X 2 (X 0 + X1) = X 0 X1+

+ X 2 (X 0 X1+ X 0 X1+ X 0 X1) = X 0 X1(X 2 +1) + X 2(X 0 X1+ , (32) + X 0 X1) = X 0 X1+ X 2(X 0 X1)

Уравнению для суммы S из (31) с учетом уравнения для переноса соответствует схема рис. 31.

Рис. 31 Схема первого разряда сумматора

Узел, обведенный пунктирной линией называется узлом переноса, а сигналы рn и g n

– сигналами генерации переноса и распространения переноса соответственно. Рассматривая рис. 30 и 31, можно записать:

C1 = g0 + p0 C0 , |

|

|

C2 = g1 |

+ p1 C1 = g1 + p1 g0 + p0 p1 C0, |

(33) |

C3 = g2 |

+ p2 C2 = g2 + p2 g1 + p2 p1 g0 + p2 p1 p0 C0. |

|

. . .

Технически реализуя уравнения (33) получают схему ускоренного переноса (узел переноса), где задержка переноса не превышает 4tзад не зависимо от числа разрядов сумматора. Причем узел переноса усложняется от разряда к разряду.

|

98 |

В качестве примера на рис. 32 |

представлено условное графическое |

обозначение на схеме электрической принципиальной микросхемы полного четырехразрядного сумматора К155ИМ3.

Рис. 32. Полный четырехразрядный сумматор К155ИМ3 Кроме рассмотренных сложных микросхем комбинационной логики промышленность выпускает множество других типов, например схемы сравнения кодов, схемы проверки четности, арифметико-логические устройства и т. д.

3.5.Последовательностные схемы цифровых автоматов

Впоследовательностных устройствах (схемах) выходные сигналы зависят не только от входных, но и от выходных сигналов и внутреннего состояния устройства в предшествующий момент времени. Для работы последовательностных схем

принципиальное значение имеет наличие времени задержки распространения рассмотренное ранее. Различают асинхронные и синхронные последовательностные схемы. В первых выходные сигналы изменяются сразу же после изменения входных сигналов. Во-вторых – выходные сигналы изменяются в строго определенные моменты времени. Для определения этих моментов служат специальные синхронизирующие сигналы.

Простейшим последовательностным устройством является триггер. Триггером называют последовательностную схему с несколькими устойчивыми состояниями. Наиболее часто используются триггеры с двумя устойчивыми состояниями. Различают триггеры с асинхронным управлением, когда его состояние зависит от текущего состояния входных сигналов в любой момент времени и триггеры с синхронным управлением, когда состояние триггера может измениться (в зависимости от состояния

|

99 |

входных сигналов) только при наличии |

сигнала на синхронизирующем входе. По |

способу представления синхронизирующего сигнала различают триггеры со статическим управлением, когда состояние входных сигналов «считывается» в течение всего времени наличия сигнала на синхронизирующем входе и триггеры с динамическим управлением, когда состояние входных сигналов «считывается» в моменты изменения лог. уровня сигнала на синхронизирующем входе, т. е. по фронту или срезу этого сигнала. При считывании по фронту синхронизирующий вход называют прямым, а по срезу – инверсным.

3.5.1. Асинхронный R-S триггер

Асинхронный R-S триггер имеет два входа: вход установки S(et) и сброса R(eset) и два

выхода: прямой Q и инверсный Q . Триггер переходит из текущего состояния на выходах Х к состоянию, когда на выходе Q устанавливается лог. «1», а на выходе

Q - лог. «0» при подаче на вход S сигнала лог. «1», а на вход R сигнала лог.»0». И

наоборот, триггер переходит из текущего состояния на выходах Х к состоянию, когда

на выходе Q устанавливается лог. «1», а на выходе Q - лог. «0» при подаче на вход S

сигнала лог. «0», а на вход R сигнала лог. «1». Состояние, когда одновременно на оба входа подаются сигналы лог. «1» является запрещенным. В практике более часто применяются R-S триггеры с инверсными входами, когда активными являются входные сигналы лог. «0». Таблица истинности для этого триггера представлена в таблице 3.7. Здесь значения Q и Q в ячейках таблицы говорят о том, что выходы могут принимать любое значение, совпадающее с предыдущим по времени значением, значение d соответствует запрещенному состоянию входов и будет доопределено на этапе оптимизации.

100

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 3.7. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

S |

|

Qt |

Qt+dt |

|

Qt+dt |

|

Название режима |

|||

1 |

|

1 |

|

Q |

Q |

|

|

|

|

Хранение информации |

|

|||

|

|

Q |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||

1 |

|

0 |

|

X |

1 |

0 |

|

|

Установка в «1» |

|

||||

|

|

|

|

|

|

|

|

|

|

|

||||

0 |

|

1 |

|

X |

0 |

1 |

|

|

Сброс |

|

||||

|

|

|

|

|

|

|

|

|

|

|||||

0 |

|

0 |

|

X |

d |

d |

|

Запрещенное |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

(неопределенное) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

состояние |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

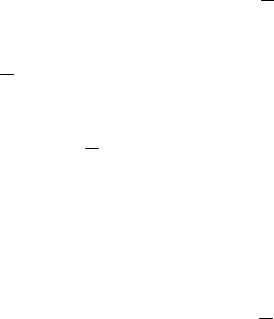

Карта Карно, соответствующая таблице 3.7. приведена на рис. 33.

Рис. 33. Карта Карно R-S триггера.

Логическое уравнение по этой карте при условии, что d до определены как «1» будет иметь вид:

Qt+dt = S + |

R |

Qt = |

S |

* |

R |

Qt . |

(34) |

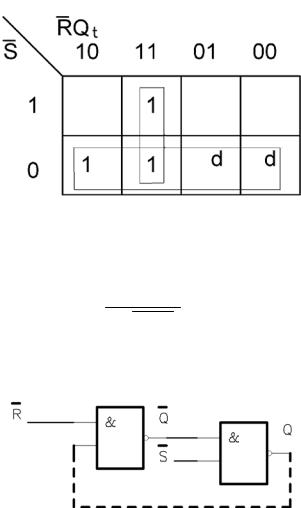

Схема, реализующая (34) представлена на рис. 34.

Рис. 34. R-S триггер

На рис. 34 сигналам и Qt соответствует выход Q (пунктирная линия на рисунке).

На схемах R-S триггеры, полученные соединением двух элементов И-НЕ изображают как на рис. 35. Здесь же справа приведено условное графическое обозначение этого триггера как функционального элемента.